一种低功耗低噪声高共模抑制斩波稳定放大器

李大为,吴昱灵

(中南民族大学电子信息工程学院,武汉 430074)

随着经济社会的不断发展,老年人口和肥胖人群比重持续增大,数据显示,心血管和心脏类疾病是这类人群的高发疾病.心脏和大脑作为维持人体正常运作最重要的器官,其活动状态可以通过心电图(electrocardiogram,ECG)和脑电图(electroencephalograph,EEG)表征.临床上,通过综合分析ECG和EEG图谱,可以对以上疾病进行及时诊断.传统心电图和脑电图检测需要病患定期到医院采用贴片电极连接专业设备进行检测,生成相关图谱后交由医生诊断,检测过程较为繁琐.而异常信号转瞬即逝,低功耗、便携式设备对于长期监测人体健康状况具有重要意义[1-2].为了实现对病患心电/脑电的实时遥测,必须将原本庞大且复杂的生理信号测量系统小型化、集成化.随着CMOS技术的发展,集成电路能将整个检测系统集成到单块芯片上,使用远程计算机对生理信号进行遥测成为可能[3].在ECG检测芯片中,最重要的模块之一便是模拟前端放大器,因为其直接获取生理信号,其性能决定了采集的ECG信号的品质.同时,由于直接采集的心电信号非常微弱,其幅度只有约100 μV~5 mV,经过衰减传到体表后的心电信号变得更加微弱[4].加之可能受到一系列干扰(人体各种动作、肌肉收缩、外界电源干扰等等),导致采集到的信号失真,高性能模拟前端是完成微弱信号检测与识别的关键.

闪烁噪声(flicker noise)消除和偏移电压(offset voltage)消除是模拟前端面临的两个主要挑战,在当前产业界和学术界,研究都集中在如何降低闪烁噪声和输入偏移电压[5-6].CMOS工艺与BJT工艺相比,CMOS工艺电路在低频有很大的闪烁噪声,虽然其量级只有μV大小,但对于ECG信号却是很大的干扰.同时仪表放大器的输入偏移电压也是造成信号受到干扰的原因,例如1 mV的输入偏移电压经过增益为10000的放大器后,幅度达到了10 V,这会导致运放直接饱和,减小放大器的输入偏移电压是设计时的重要考量之一.当前降低闪烁噪声和偏移电压的方法有自动归零技术[1,3](Auto Zero)和截波稳定技术[5-6](Chopper Stabilization).自动归零技术基于交流耦合(AC-Coupling),可有效隔绝偏移电压,其中偏移电压包括电路本身不匹配和氯化银电极带来的偏差.同时,自动归零技术使用了两相时钟来消除闪烁噪声,但其只在采样频率大于转折频率时才有效,并且该方法会将宽带噪声混叠到低频段.截波稳定技术是将低频噪声和低频信号调制至不同的频段,然后通过滤波器来分离低频段的噪声和信号.与自动归零技术相比,不需要开关电容的采样,所以不存在热噪声增加的问题,对于低频应用是比较好的选择.然而,对于生物医疗应用来说,传统的斩波放大器并不能满足要求,因为一般ECG信号频率约为0.01 Hz-250 Hz,为了实现0.05 Hz低频截止频率需要使用TΩ级的电阻,这将会消耗很大的芯片面积造成成本增加.此外,在临床使用时,模拟前端通过电极与患者相连,患者的移动可能会导致较大的直流偏移,AFE电路可能会进入饱和区域从而影响电路的正常放大功能.

针对上述问题,本文提出了一款应用于心电信号采集的斩波稳定低噪声放大器,通过电容反馈回路提高增益精度,通过采用有源PMOS可控电阻取代无源电阻极大地减小了芯片面积,同时有效抑制了MOS管栅端漏电流;为了消除由于人体动作造成的不可控的输入直流偏置,提出了一种简易直流偏置电路,通过一个二极管连接的MOS,控制直流偏移电平,维持电路正常工作.

1 现有结构分析

目前关于仪器放大器(Instrumentation Amplifier,IA)的研究,主要有传统三运放仪表放大器[7],电容反馈仪表放大器[5],电流平衡式仪表放大器[8],微分差动仪表放大器等[9-12].这些仪表放大器的输入阻抗均能够达到109-1012Ω,高输入阻抗对于采集像ECG这样的微弱信号十分重要.此外低噪声,高共模抑制比和低失调电压也是仪表放大器的重要指标之一,这里对几种类型的仪表放大器进行简要分析.

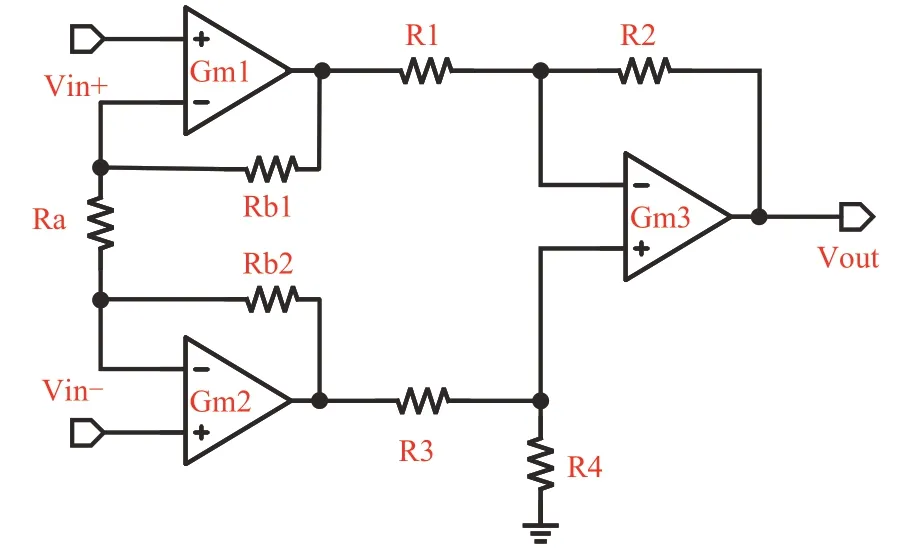

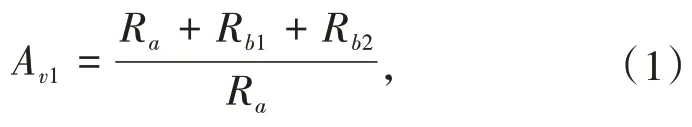

1.1 三运放仪表放大器

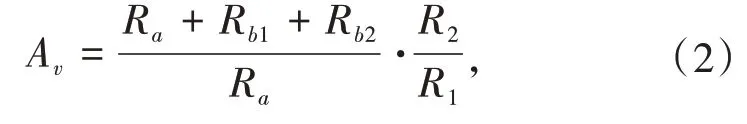

传统三运放仪表放大器[7]如图1所示,使用3个运算放大器构建分立式仪表放大器.电路将差动信号转换为单端输出信号,当输入和输出信号分别处于电路的输入共模和输出摆幅范围内时,运算放大器以线性模式运行.电路的输入级采用两个放大器,且输入端是同向差分输入,电路的第一级增益由式(1)给出.

图1 三运放仪表放大器Fig.1 The circuit of three-ops based instrumentation amplifier

最后一级放大器是核心放大器,电路总增益为:

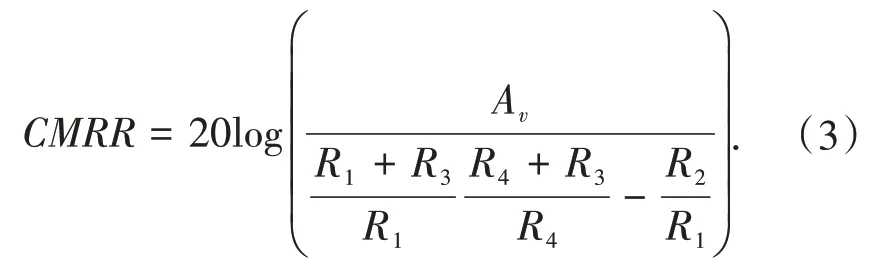

三运放仪表放大器的共模抑制比为:

由(3)式可知此种放大器非常仰赖电阻的匹配,而CMOS工艺下电阻偏差可达20%,导致该种结构CMRR不佳,同时三个运算放大器会消耗大量功率.

1.2 交流耦合-电容反馈放大器

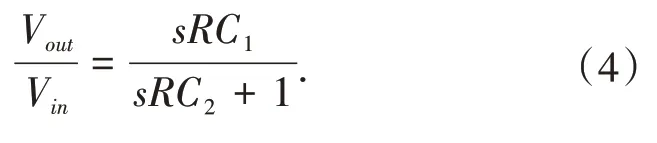

针对三运算放大器的高功率消耗问题,交流耦合-电容反馈放大器通过更小的电容面积取代了放大支路,有效地降低了功耗[5].交流耦合-电容反馈放大器电路如图2所示,该类型的仪表放大器最大的优点为其架构简单以及功率消耗非常低.由图可知其传递函数如式(4).

图2 交流耦合-电容反馈放大器Fig.2 The circuit of AC coupling-capacitor feedback amplifier

由式(4)可知,虽然交流耦合-电容反馈放大器能通过R、C构成一个带通滤波器以达到交流耦合的效果,但R、C的匹配问题将会严重影响到CMRR.

1.3 电流平衡式仪表放大器

为了解决电阻匹配的问题,电流平衡式放大器通过不对称的结构输出不对称的电流,有效的防止了电阻失配[8].电流平衡式仪表放大器电路如图3所示,由图可推导出传递函数如式(5),由式(5)可知电流平衡式结构传递函数无电阻匹配的问题.电路增益可由电阻调整,且Vref可调整输出共模电位,但内部电路本身的不对称带来的电压偏移会导致CMRR下降.

图3 电流平衡式仪表放大器Fig.3 The circuit of current balanced instrumentation amplifier

1.4 差动仪表放大器

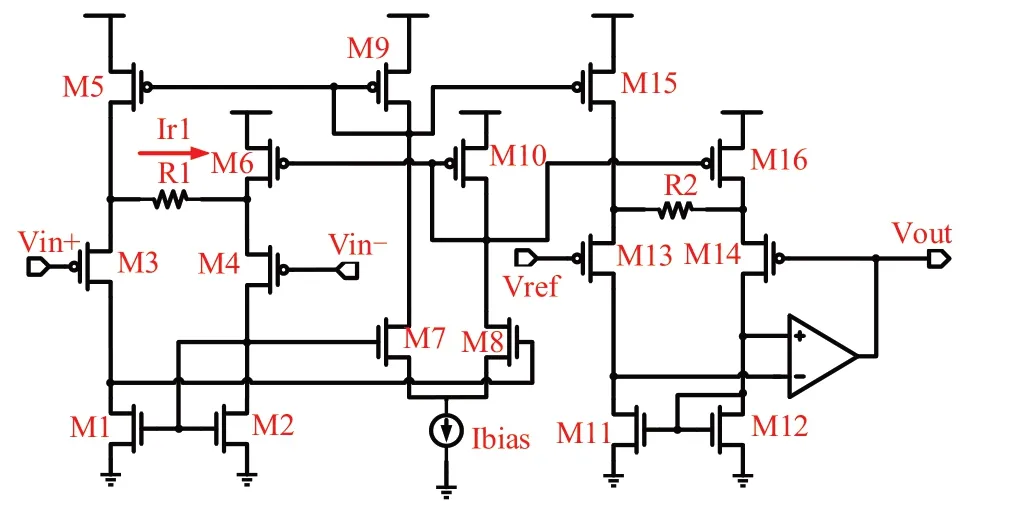

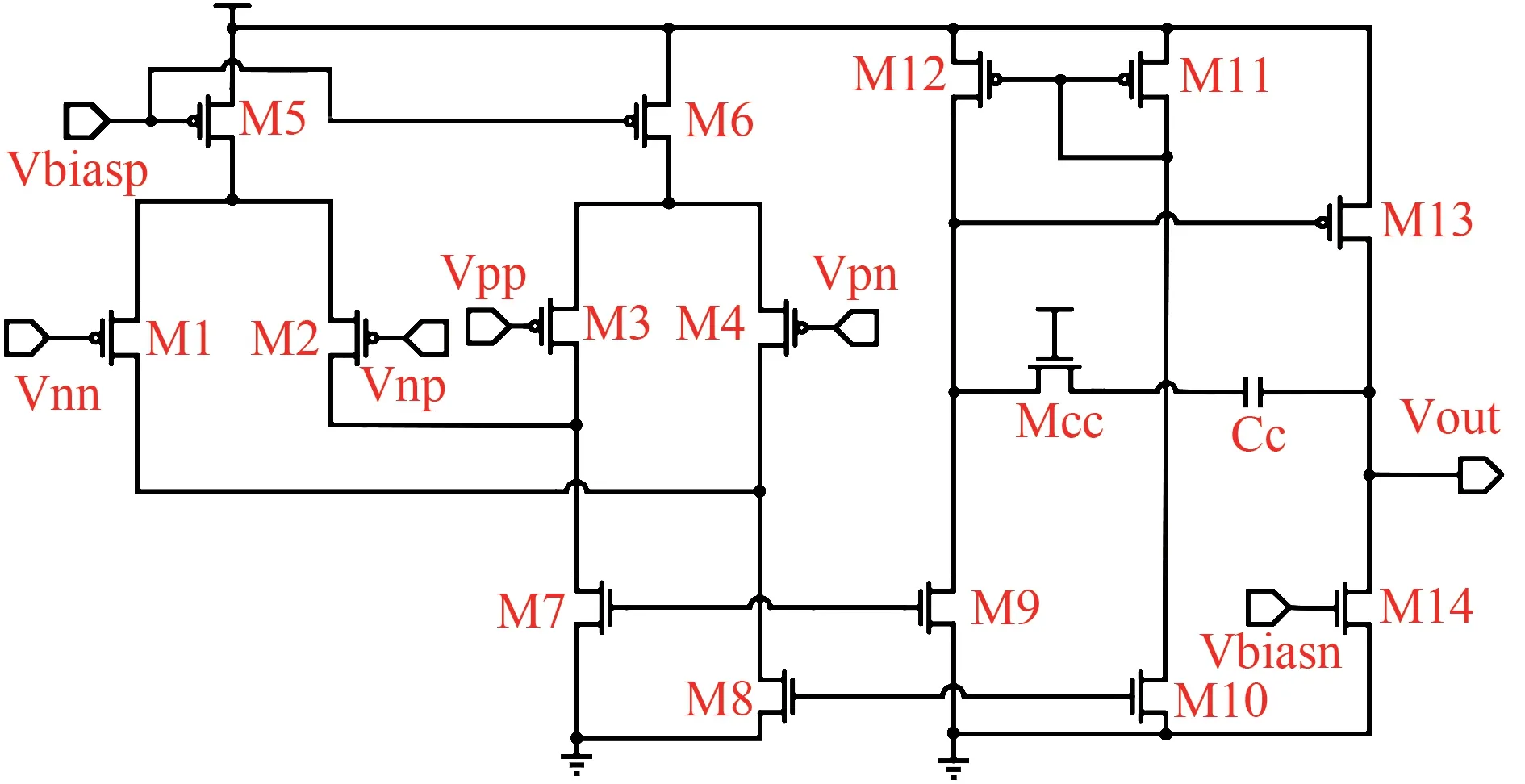

以上几种方法都没有在CMRR和功耗性能之间实现很好的平衡,差动仪表放大器通过双输入Gm级和伪电阻设计,在实现高输入阻抗的前提下对两者进行了很好的平衡[9-12].如图4为差动仪表放大器,其中M1~M4为输入对,为降低噪声采用PMOS输入对.M7和M8为负载,将输入电压转换成电流复制到M9和M10.M9和M10可视为一个共源(Common Source)差动放大器,借由其负载M11和M12将电流转成电压传送到输出级,M13和M14为常见的PMOS管共源放大器,其中,M14提供偏置电流,M13为输入管.

图4 差动仪表放大器电路Fig.4 The circuit of differential instrumentation amplifier

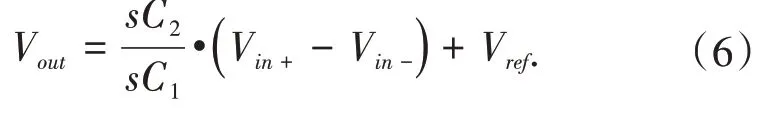

图5为差动仪表放大器架构,根据图5可得到式(6),由式(6)可知增益是两个阻抗之间的比例.因为电路增益是电容阻抗的比值,所以相对误差可达1%,所以容值的漂移问题对增益无明显影响.

图5 差动仪表放大器架构图Fig.5 The structure of differential instrumentation amplifier

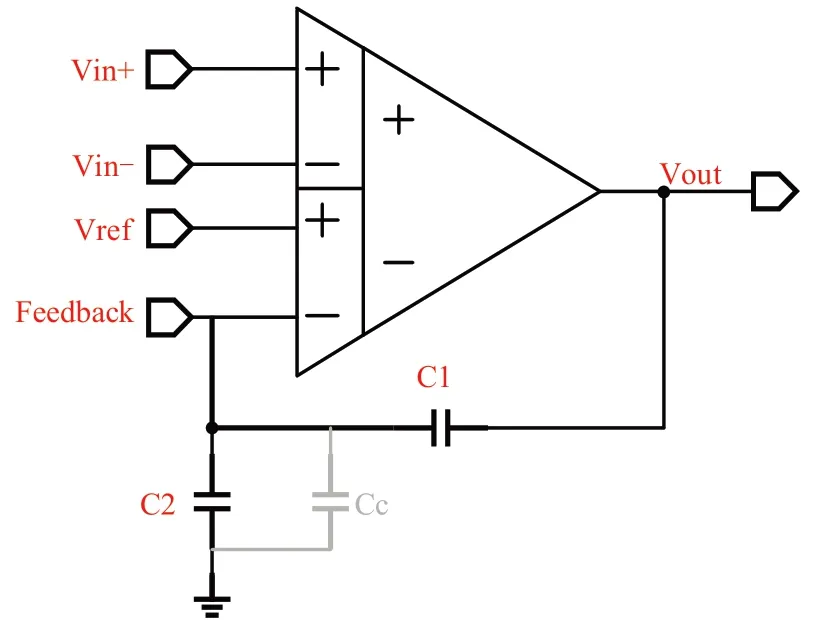

对于几种仪表放大器的性能对比如表1所示,表1中,差动式结构(Differential Difference Amplifier,DDA)在输入阻抗、CMRR与功耗方面均有不错的表现.综合考虑在本设计中使用斩波差分放大器(Chopper-stablized Differential Difference Amplifier,

表1 常用仪表放大器功效比较表Tab.1 Comparison of common instrumentation amplifiers

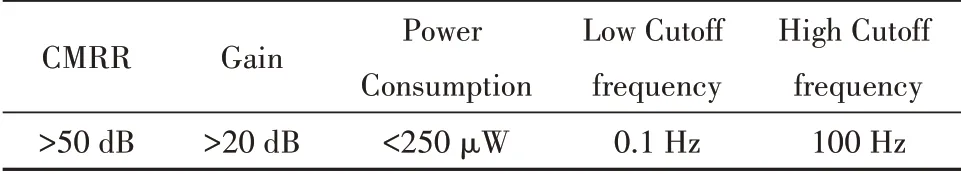

CHSDDA)[9,13].斩波差分放大器是一种基于斩波技术的DDA,具有输入端口失配容限高、共模抑制比高、输入失调噪声低等特点,而且CHSDDA只使用一个有源放大器,因此面积和功耗远小于使用三个有源放大器的IA,本文采用的CHSDDA仪表放大器设计指标如表2所示.

表2 整体仪表放大器指标Tab.2 Instrument amplifier circuit specifications

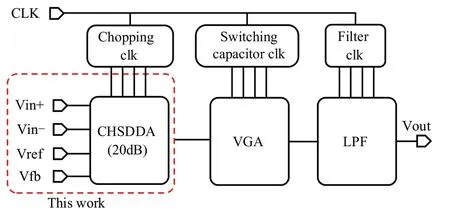

2 ECG模拟前端

整个模拟前端电路共分三级如图6所示,图6中,第一级仪表放大器作为前置放大器提供基本增益并呈现高输入阻抗,斩波电路与带噪声的低频信号作乘法操作后将噪声升频,运放内置的低通滤波器将升频后的噪声滤除,同时第一级放大器输出端的斩波电路将升频后的信号降频.第二级为可变增益放大器(Variable Gain Amplifier,VGA)选取合适增益,以补偿第一级仪表放大器放大倍数不足.第三级低通滤波器(Low Pass Filter,LPF)将信号进一步滤波后输出给后级.最后在输出端得到放大后的低噪ECG信号.前端放大器处于模拟前端的第一级,其性能直接决定了采集的ECG信号的品质,也是本文的工作重点.

图6 ECG前端系统架构图Fig.6 The architecture of ECG front-end system

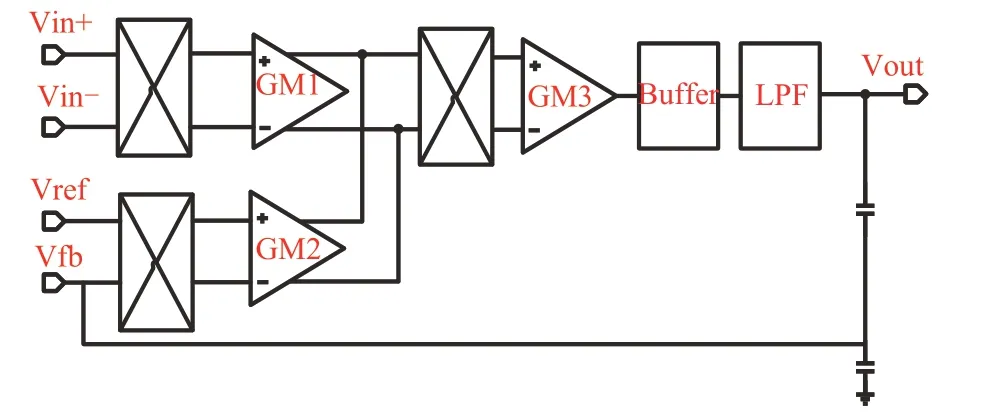

2.1 差分斩波放大电路

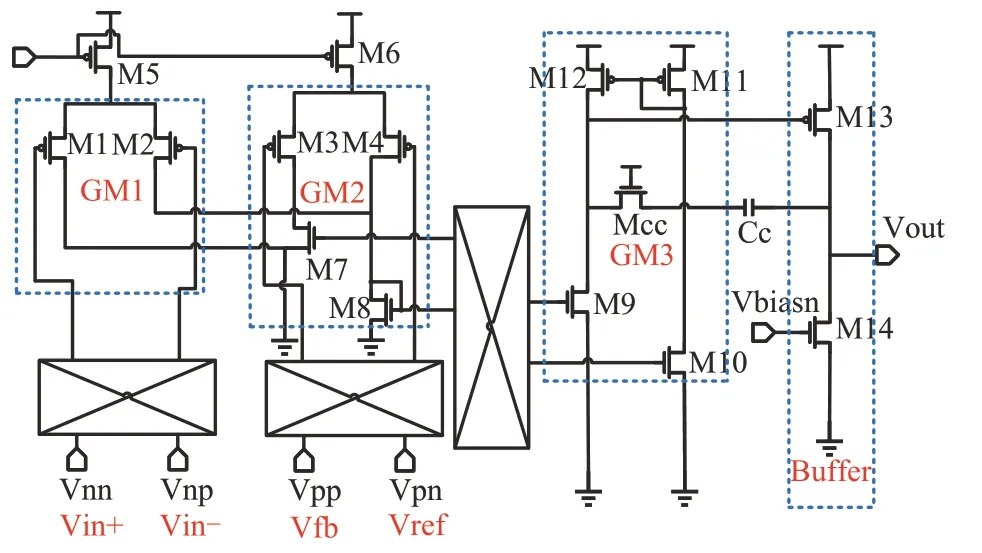

所采用的斩波放大器架构如图7所示,斩波电路的原理是通过乘法操作将信号频率搬移到高频,正常放大过程夹带的低频噪声(如闪烁噪声)也被转换为高频噪声,通过滤波器将高频噪声滤除后,再通过一次乘法操作将高频正常信号搬回低频.具体的电路结构如图8所示,图8中,Vnn和Vnp是输入ECG信号,Vpp连接到参考电压,Vpn连接到反馈电路,输入直接连接到斩波电路,用于将低频噪声转换为高频噪声.其他电路中,M1~M4为输入对,M5和M6为电路提供电流,M1~M4将信号从电压型转换为电流型,M7和M8再将信号转换回电压型,并通过M9~M14进行放大.

图7 CHSDDA架构图Fig.7 The architecture of CHSDDA

图8 主差分斩波放大电路图Fig.8 The circuit of main chopper differential amplifier

2.1.1 全差分放大电路

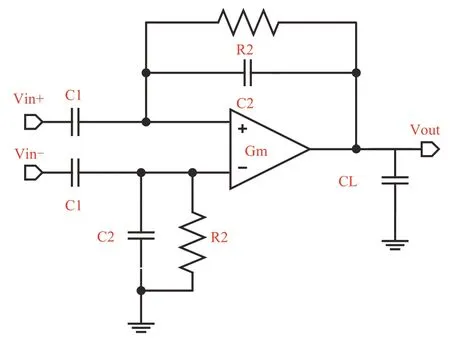

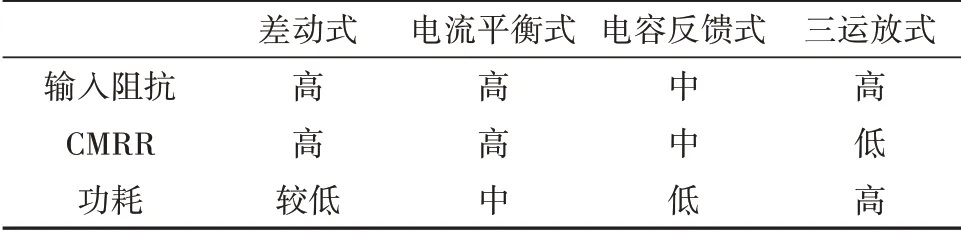

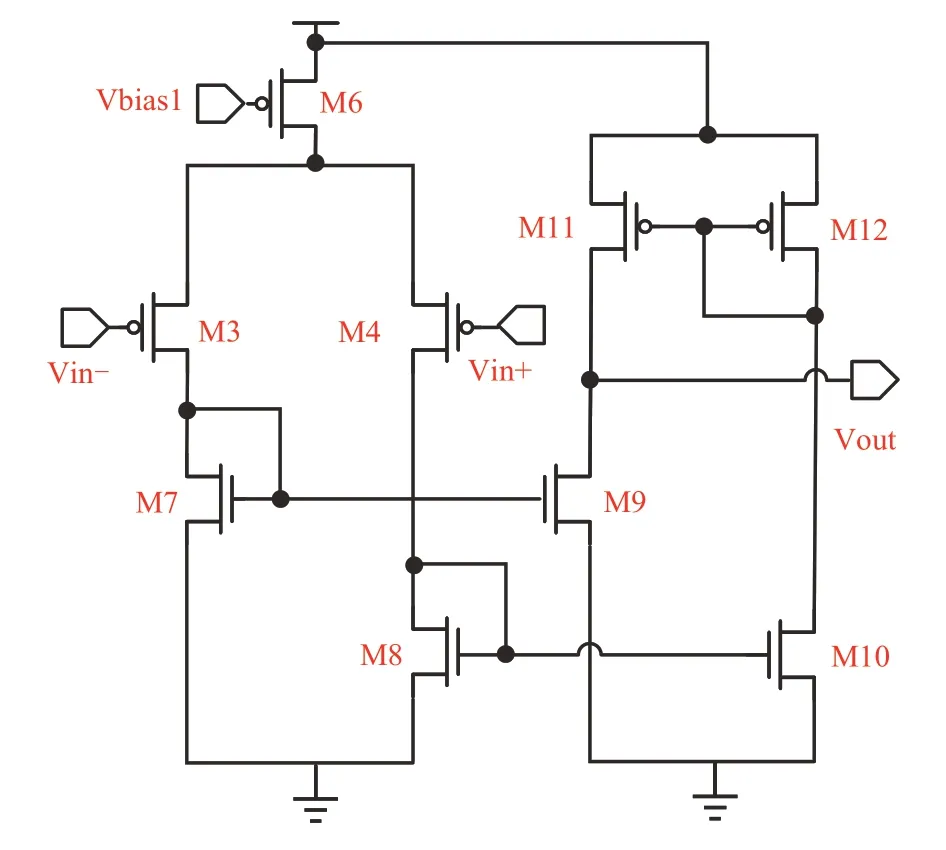

低噪声运算放大器可以通过两种方法来实现:一种是使用外部方法,如斩波电路;另一种是通过电路拓扑、晶体管选择和尺寸优化来最小化噪声.这两种方法在本设计中均有使用.核心放大器的拓扑是两级运算跨导放大器(Operational Transconductance Amplifier,OTA),如图9所示.图9中,由于PMOS器件的闪烁噪声比NMOS器件小一到两个数量级,为了最小化1/f噪声,采用PMOS晶体管作为OTA的输入器件.同时增加输入第一级MOS管的宽长比以降低闪烁噪声.此外,负载管(M11和M12)的长度选择大于输入管(M3和M4)的长度,以降低整体噪声.为了降低系统功耗,该放大器中作为电流源的M6被偏置在亚阈值区工作.

图9 全差分电路图Fig.9 The circuit of fully differential circuit

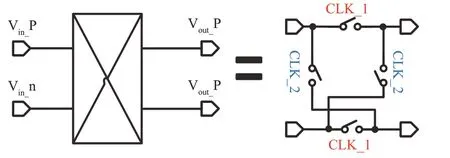

2.1.2 斩波电路

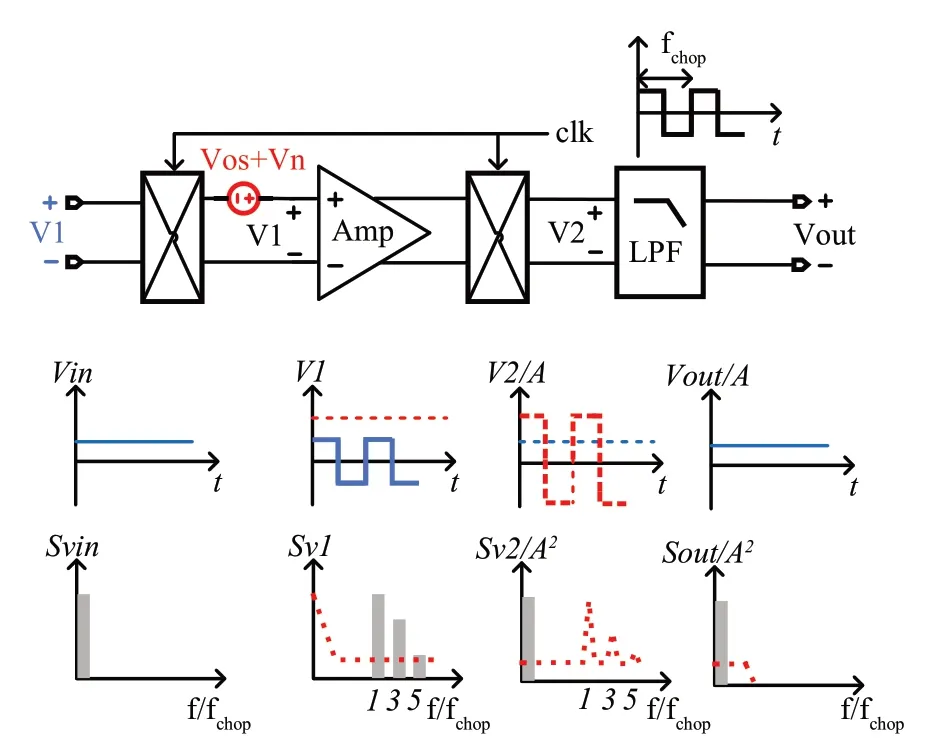

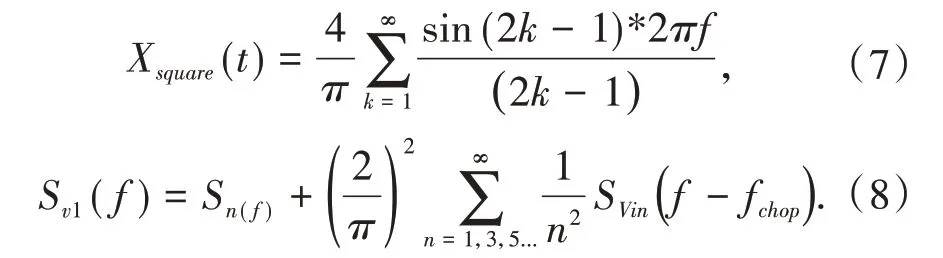

图10定量分析了斩波技术工作原理[14],通过方波来调制低频输入信号,该操作通过一组被称为“斩波器”的开关来完成.调制过程将输入信号调制为fchop的奇次谐波.具体为输入信号被斩波频率调制到更高的频率,式(7)给出方波的傅里叶级数,将输入信号转换为调制后的奇次谐波,结果为式(8).

图10 斩波器原理图Fig.10 Principle of chopper-stabilized amplifier

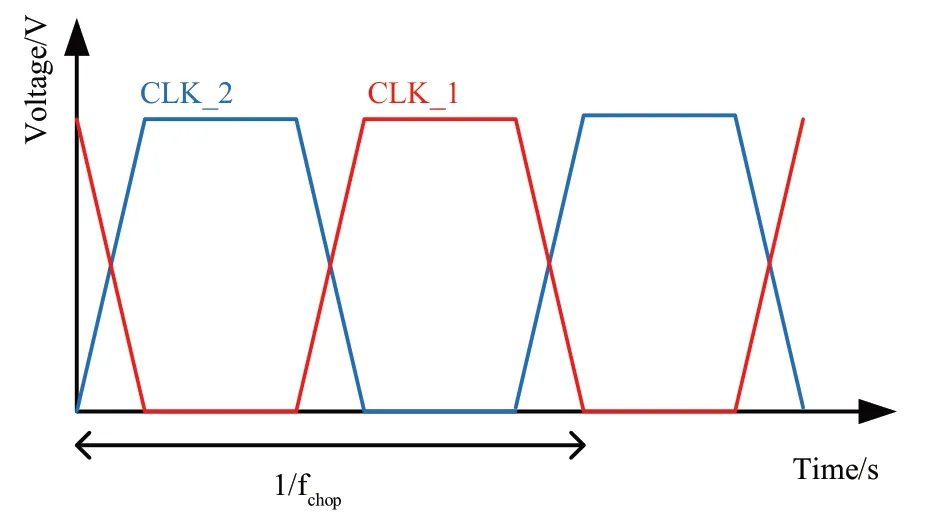

斩波电路由四个相同的MOS开关组成,如图11所示,图11中,这些开关在时钟的每半周期中翻转一次极性,根据奈奎斯特采样定理,斩波器频率应大于ECG信号最高频率的2倍.这里进一步考虑闪烁噪声与热噪声的分布,计算方式由式(9)确定,其中,K值大于等于2,BWsingal为信号带宽,fcorner为噪声的角频率,这里斩波器频率取10 kHz保证同时满足以上2个条件.非重叠时钟CLK_1和CLK_2是斩波信号的时序,如图12所示,CLK_1和CLK_2时序非重叠是为了防止时钟馈通到输出电压.信号放大后,由输出斩波器调制回原频率.同时,放大器的偏移和闪烁噪声被调制到高频.输出斩波后的功率谱密度(Power Spec⁃tral Density,PSD)由式(8)给出.由于第二次斩波后输出电压带有放大器偏移的高频分量.为了消除该高频分量,在放大器输出斩波后采用LPF对上调的偏置电压和闪烁噪声进行平均.

图11 斩波器电路图Fig.11 Chopper circuit

图12 斩波器时钟时序Fig.12 Timing of chopper clock

2.1.3 低通滤波器

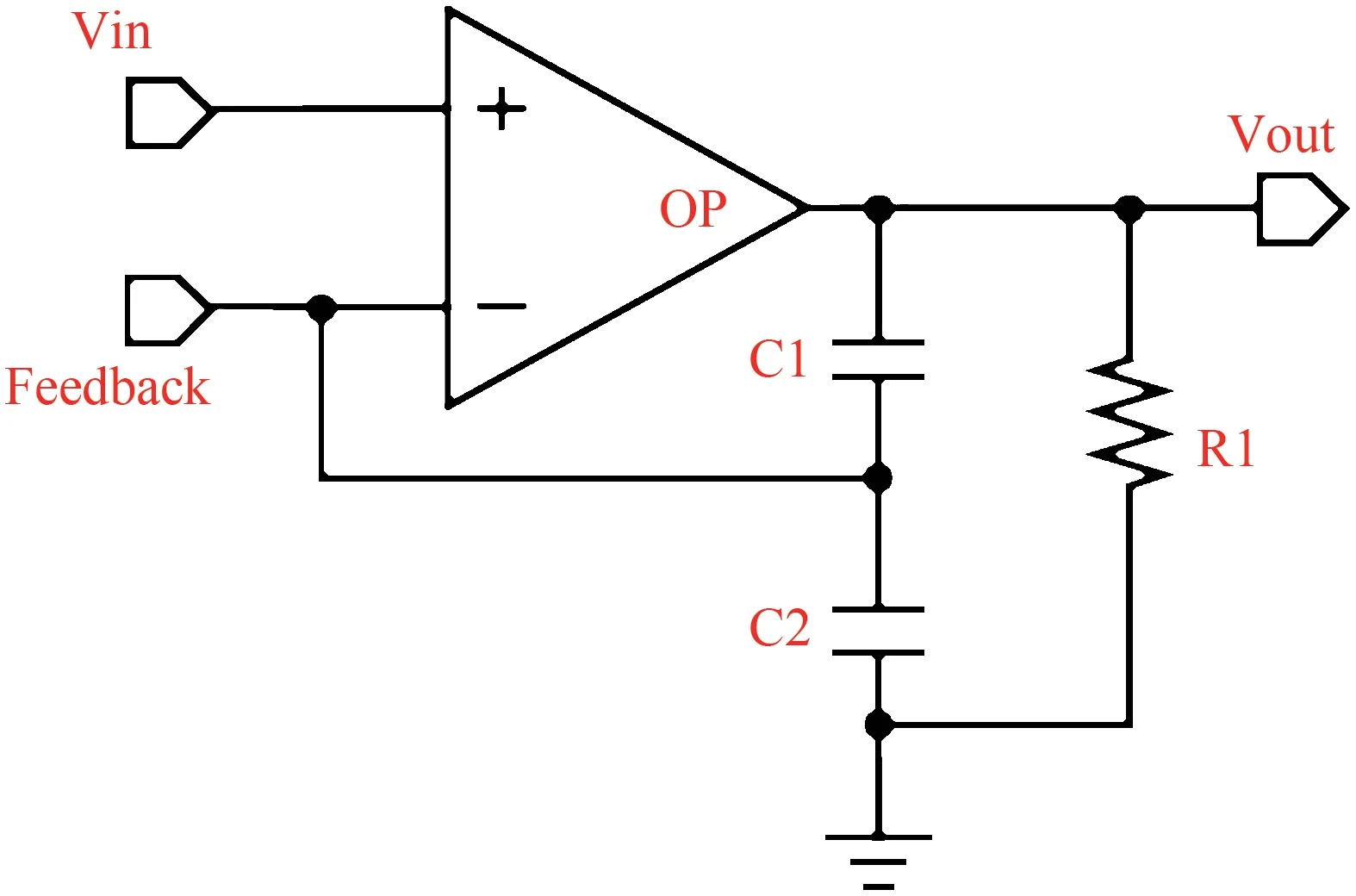

滤波器的滤波效果依赖其衰减止带(Stop band)频率的能力,滤波效果越好的滤波器,止带信号被衰减的幅度就越大.理想状态的低通滤波器,在通带以外的信号被衰减至0 dB.实际过程中,信号通过截止频率之后会缓慢的衰减,且不同滤波器其衰减幅度也各有不同.以滤波器阶数(order)来分类,阶数越高效果越好,但其电路也越复杂,消耗功率也会提升.考虑低功耗设计,本文以一阶滤波器为主来设计系统电路[15-17].因为ECG信号频率较低,对应的滤波电阻会占据大量的芯片面积.为了解决这个问题,该设计用电容代替电阻,如图13所示.

图13 一阶低通滤波器图Fig.13 The first-order low-pass filter

2.2 伪电阻

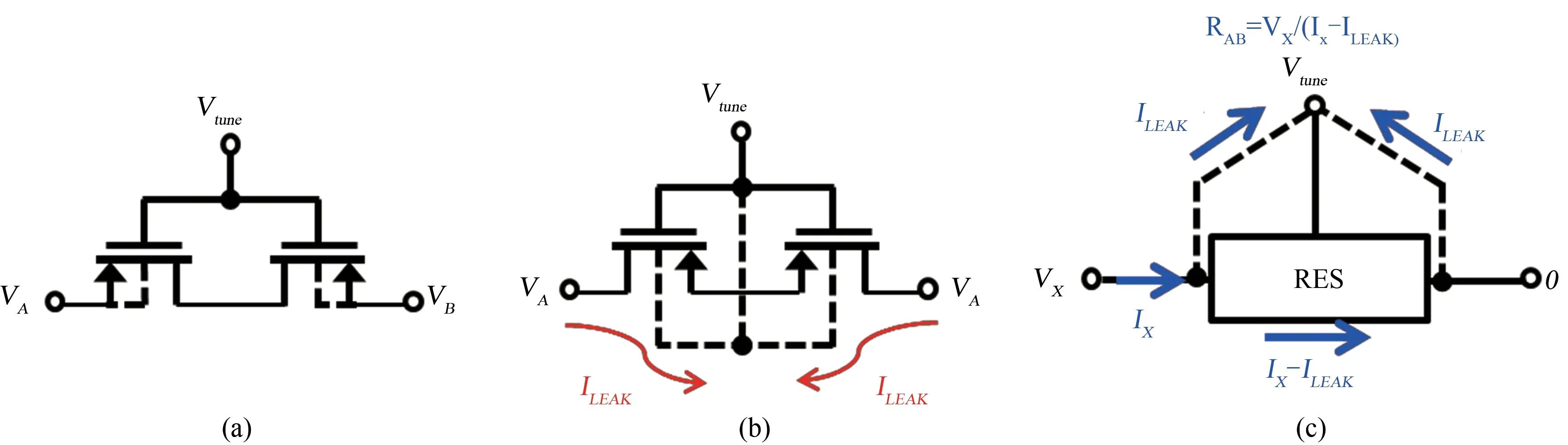

伪电阻用于替换CHSDDA低通频率所需的大电阻.它由工作在弱反型层的PMOS晶体管组成,如图14所示.这里讨论两种架构,图14(a)所示的第一个架构是最常用的架构[14].图14(b)是由图14(a)修改后的版本,通过将衬底(bulk)连到栅极,再由栅极电压Vg控制.由于状态界定模糊,至今为止,伪电阻的理论模型仍然存在误差.计算结果和仿真结果之间的差异解释了这一点,仿真仍然是预测测量结果的主要方法.图14(c)给出了两种架构的电阻计算方法.电阻RAB定义为通过电阻器的电压降VX除以流入/流出电阻器的电流IR.流入/流出电阻器的电流可以通过IR=IX-ILEAK得到,其中IX是来自测试电压源的电流,ILEAK是从伪电阻到Vg的泄漏电流.

图14 伪电阻结构Fig.14 The structure of Pseudo-resistor

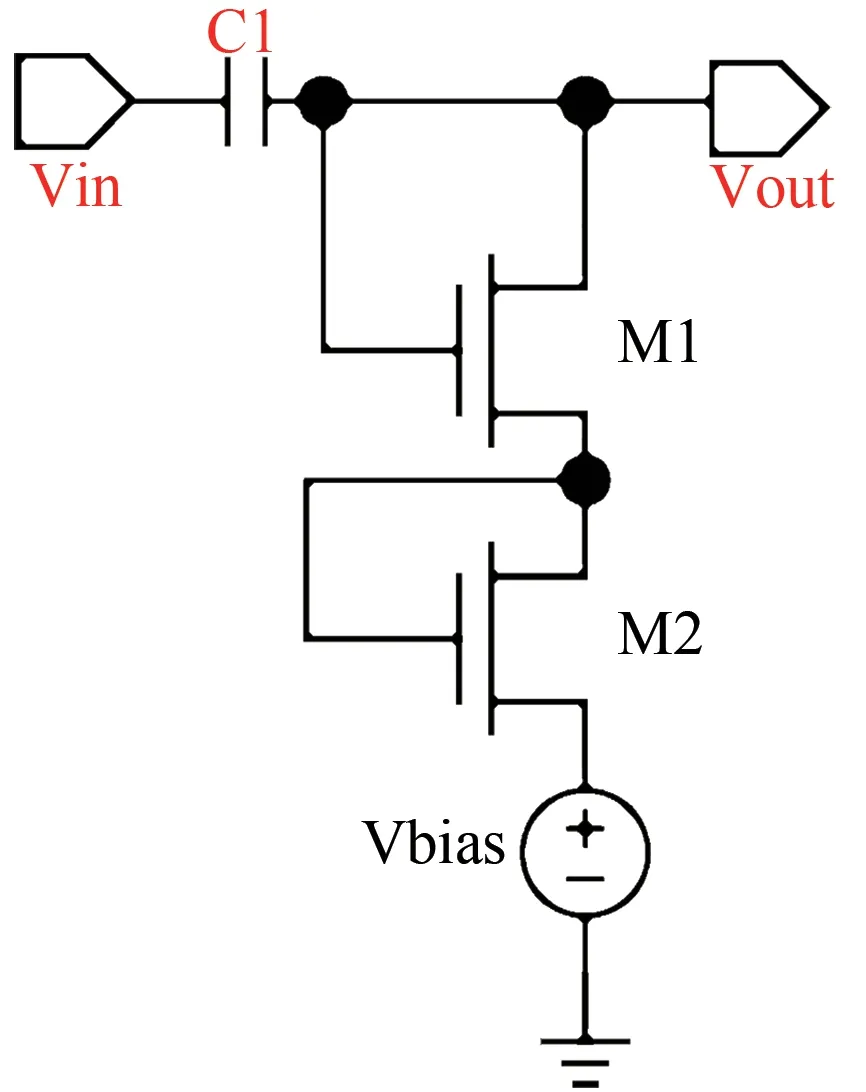

2.3 直流偏置电路

患者的移动可能会导致较大的DC偏移,从而使AFE电路进入饱和区域[18-20].为了解决这个问题,我们为差动放大器的输入端增加了一路如图15的直流偏置电路,该支路由两个NMOS管M1和M2组成,C1为输入电容.该直流偏置支路将输入信号本身的直流隔离后自偏置产生所需的直流电压,避免了由于携带者身体移动导致输入直流的失配.M2源极连接直流偏置电压Vbias,直流偏置电路提供的稳定直流电压由式(11)得到.式中k值为Vout随Vbias改变的变化率,由NMOS管宽长比和Vbias的大小决定,Vbias是外接的偏置电压,用于控制输出直流电压.

图15 直流偏置电路结构图Fig.15 DC bias branch

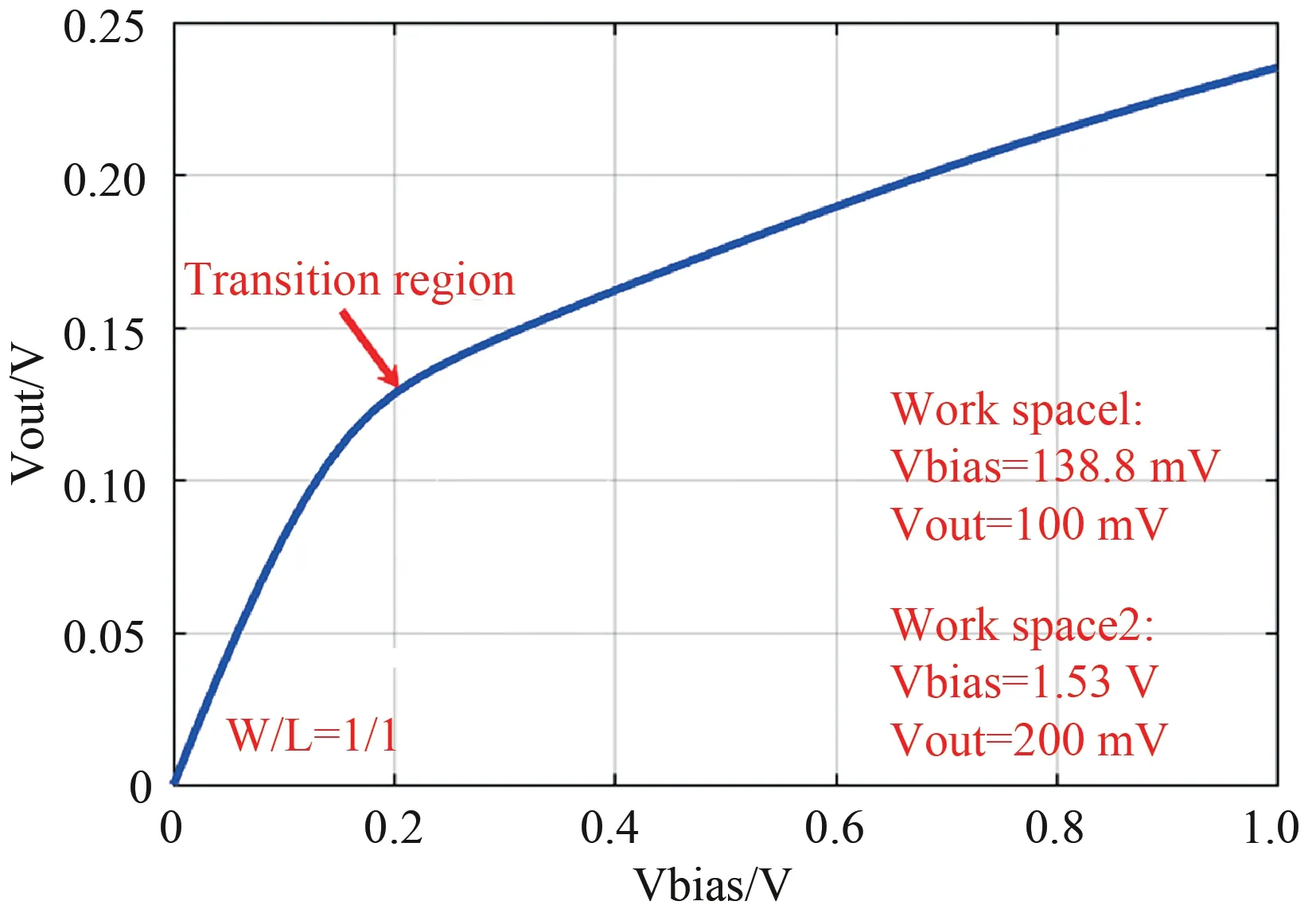

直流偏置电路的仿真结果如图16所示,Vbias在区间0~160 mV对应工作区1,斜率k近似为0.72,Vbias在区间200 mV~1 V是工作区2,斜率k值近似为0.13.Vbias在区间160 mV~200 mV处于转折区,因为该区域Vout与Vbias处于非线性区,应该尽量避免Vbias处于这个区域.

图16 偏置电路仿真图Fig.16 Simulation results of bias circuit

3 实验结果与分析

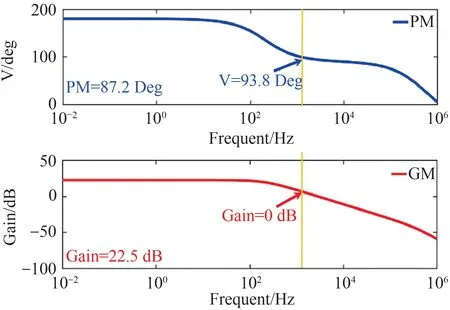

图17为第一级CHSDDA的相频特性和幅频特性仿真结果.图17中,CHSDDA在所设计的0.01 Hz-100 Hz带宽范围内增益为22.5 dB,在单位增益带宽处的相位变化为93.8°,由此可计算出系统的相位裕度为87.2°,符合相位裕度大于45°的要求.

图17 CHSDDA增益(归一化处理)及相位裕度Fig.17 The gain and phase margin of CHSDDA(normalized processing)

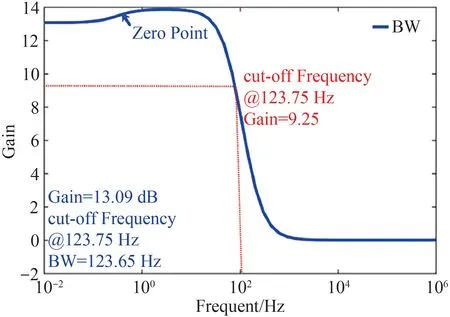

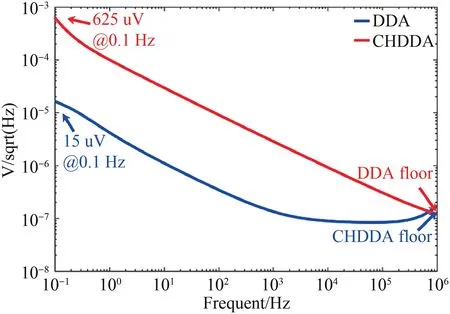

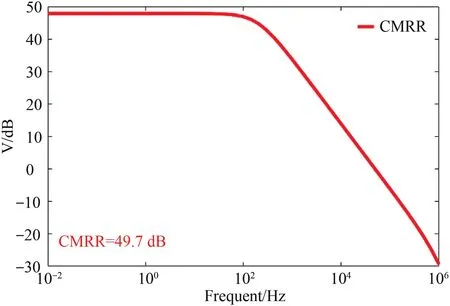

带宽仿真结果如图18,图18中,斩波频率为123.75 Hz时低频增益为13.09 dB,由于零点的存在使得系统增益在0.8 Hz时有显著的抬升效果,最大增益可以达到14 dB.在斩波频率123.75 Hz处,电路增益还有9.25 dB.从图中可看出截止频率为143.5 Hz,fL=0.01 Hz,fH=123.75 Hz,由于fL< 图18 CHSDDA带宽Fig.18 The bandwidth of CHSDDA 图19为DDA加入斩波电路前后噪声性能对比.在图19中,红线为未加斩波电路时的等效输入噪声仿真结果,蓝线为加入斩波电路之后的等效输入噪声仿真结果.可以看到加入斩波电路后低频噪声性能显著提升,在0.1 Hz时噪声从625 μV/√Hz下降到15 μV/√Hz,计算可得,无斩波电路的噪声PSD为212 μV/√Hz,有斩波电路的PSD为852 nV/√Hz,降低了约4000倍.由于ECG信号集中在0.1 Hz~100 Hz,在该有效频段内显著改善了电路的噪声.图20为共模抑制比的仿真结果,从图中可以得出直流共模抑制比为49.7 dB,满足设计要求的50 dB,共模抑制比在123.75 Hz处开始下降,表明电路对带内共模噪声有很好的抑制效果. 图19 加入斩波电路前后输出噪声对比Fig.19 Comparison of output noise with and without adding chopper circuit 图20 共模抑制比仿真结果Fig.20 Simulation results of CMRR 本文提出了一种用于ECG信号检测的斩波稳定放大器,仿真结果可知该放大器增益为22.5 dB,满足增益20 dB的要求,相位裕度为87.2°,符合相位裕度大于60°的要求,共模抑制比仿真结果为49.7 dB.加入斩波器后低频噪声显著降低,作为对比,无斩波电路的噪声PSD为212 μV/√Hz,有斩波电路的PSD为852 nV√Hz,由于ECG有效信号主要集中0.1 Hz~100 Hz,等效输入参考噪声仅为15 μVrms,同时总消耗电流仅为80 μA.

4 结语