一种集成4/5 和8/9 的异步预分频器设计

张 博,王好博

(西安邮电大学 电子工程学院,陕西 西安 710121)

基于锁相环(Phase Locked Loop,PLL)的射频频率综合器是收发机电路的主要组成部分,主要为无线收发系统提供本地振荡信号[1]。随着通信技术的不断发展,无线通信工作频段日益提高,部分场景下需求频段已达到了几个GHz[1-2]。因此对锁相环的要求也逐渐提高,高速、低功耗、小型化已成为追求的目标。在锁相环中,分频器和压控振荡器是核心模块,分频器位于锁相环反馈支路上,直接接收来自压控振荡器的信号,工作在频率综合器中的最高频率,其工作速度、工作频率和功耗决定了整个频率综合器的性能[3]。因此,研究和设计一种高频率、低功耗、面积小的双模预分频器有着重要的意义和价值[4]。

双模预分频器以D 触发器为基本组成单元,近年来为了提高D 触发器的性能,不断涌现出各种类型的触发器电路结构。文献[4]采用MOS 电流模逻辑电路,设计了一个二分频器和一个四分频器,其中二分频器最高工作频率为7.7 GHz,功耗为76.68 μW,四分频器最高工作频率为3 GHz,功耗为153 μW。文献[5]采用真单相位时钟控制电路,设计了8/9 双模预分频器,其中8/9 双模预分频器的最高工作频率为5.7 GHz,功耗为6.25 mW。文献[6]采用电流模逻辑电路设计了4/5,8/9 前置分频器,最高工作频率可达10 GHz,功耗为80 mW。

本文采用CMOS 源极耦合逻辑(Source Coupled Logic,SCL)电路,针对同步分频器最高频率受工作速度和D 触发器个数的影响,设计了异步分频器,提高了电路的工作频率,并减少了D 触发器的个数,降低了功耗,节省了芯片面积。由于双模预分频器只能实现两种分频比,为了满足不同应用需求且不增加分频器的个数,本文通过一种电路结构同时实现了4/5分和8/9 分的双模预分频器功能,提升了预分频器的电路性能,同时也提高了频率综合器的性能。

1 预分频器设计

分频器是锁相环频率综合器的主要模块之一,其作用是将压控振荡器产生的高频时钟进行降频处理,在鉴频鉴相器的输入端与参考信号作比较,通过锁相环路的负反馈原理,使分频后的信号和参考信号频率相等且相位对齐,从而锁定输出频率[7]。双模预分频器主要包括同步预分频器和异步预分频器两种结构。

1.1 同步4/5 预分频器

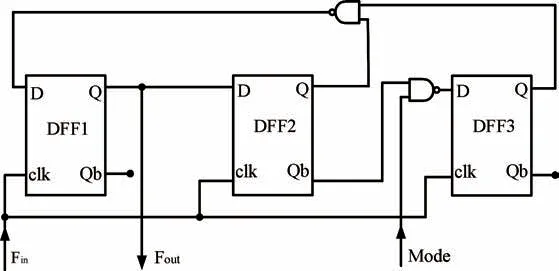

同步4/5 预分频器的结构框图如图1 所示,由四个SCL-D 触发器和两个与非门构成,当Mode 信号为低电平时,电路的分频比为4。当Mode 信号为高电平时,电路的分频比为5。在D 触发器1(DFF1)和D 触发器2(DFF2)之间再加入两级触发器即可构成同步8/9 分频器,控制逻辑不变。之所以称之为同步预分频器,是因为四个D 触发器的输入为同一个信号,因此它们的时钟会同步。该种类型分频器逻辑结构简单,得到了很广泛的应用,但双模预分频器电路直接接收来自压控振荡器的输出信号,工作频率很高,同步的电路结构使得所有的触发器都工作在最高频率,会消耗非常大的功耗。当有更高分频比的需求时,只能通过增加D 触发器的个数来实现。电路过于冗余且会造成不正常的循环,电路逻辑会发生错误。异步分频器会很好地解决该类问题[8-9]。

图1 同步4/5 预分频器结构框图Fig.1 Synchronous 4-or-5 prescaler structure

1.2 异步8/9 预分频器

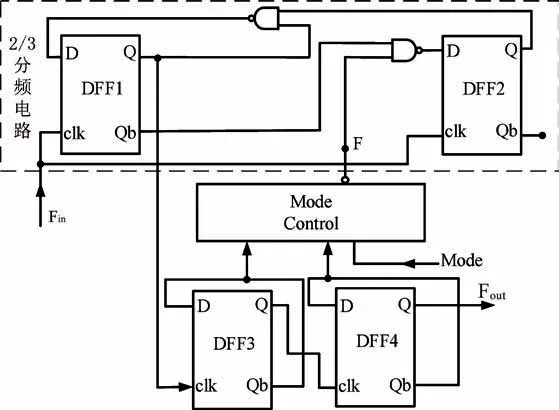

异步8/9 预分频器的结构框图如图2 所示,异步8/9 预分频器可以看作由同步2/3 分频器结构和两个二分频器级联以及模式控制电路组成。工作原理为:当Mode 信号为高电平时,模式控制电路的输出恒为低电平,如图3 所示虚线框中的2/3 分频电路工作在2分频模式,Fin信号经过2/3 分频电路二分频后,再经过DIFF3 和DIFF4 两级二分频器电路,输出Fout信号为8 分频后的信号。当Mode 信号为低电平时,节点F为逻辑“1” 时,2/3 分频电路工作在3 分频模式;节点F 逻辑为“0” 时,2/3 分频电路工作在2 分频模式,Fin信号在经过2/3 分频电路后再经过下面的两级二分频电路,此时输出Fout信号为9 分频后的信号。异步分频器的核心思想是:在进行奇数分频时,在一个输出周期内,它的输出有且仅有一个输入时钟周期与其他周期不同。与具有相同分频比功能的同步分频器比较,异步分频器电路结构在保证逻辑正确的同时,避免了所有D 触发器都工作在电路最高频率,D 触发器的数量也有所减少。尤其当需要更高分频电路时,异步触发器所需增加的触发器个数远远小于同步触发器,大大节省了芯片的面积和电路整体功耗。

图2 异步8/9 分频器结构框图Fig.2 Asynchronous 8-or-9 prescaler structure

1.3 集成4/5 和8/9 异步预分频器

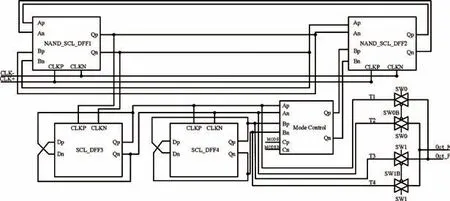

集成4/5 分和8/9 分异步预分频器的结构框图如图3 所示,电路由四个D 触发器、一个模式控制电路和四个传输门组成。框图上面部分构成2/3 分频的D 触发器与逻辑门电路进行了合并,构成了集成门电路的D 触发器。集成4/5 分和8/9 分异步预分频器电路通过四个传输门和模式控制电路来实现不同分频模式的切换,当开关SW0=1,SW0B=0,且SW1=0,SW1B=1 时,传输门T1、T2 导通,传输门T3、T4 关断,输出4 或5 分频信号。当开关SW0=0,SW0B=1,且SW1=1,SW1B=0 时,传输门T3、T4 导通,传输门T1、T2 关断,输出8 或9 分频信号。当控制信号MODE=0,MODEB=1时,模式控制输出信号在高低电平之间切换,控制2/3分频电路工作模式在2 或3 分频之间切换,整体电路工作在5 或9 分频模式。当MODE=1,MODEB=1 时,模式切换电路输出恒为低电平,2/3 分频电路一直工作在2 分频模式,整体电路工作在4 或8 分频模式。

图3 集成4/5 分和8/9 分异步预分频器结构框图Fig.3 Integrated 4-or-5 and 8-or-9 asynchronous prescaler structure

2 电路设计

2.1 SCL D 触发器电路

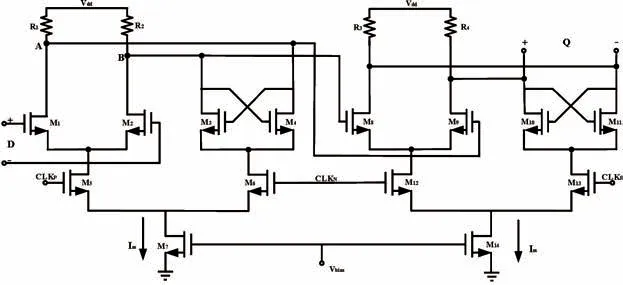

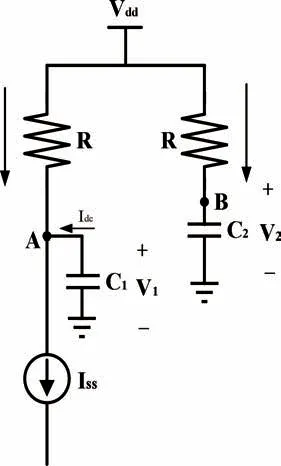

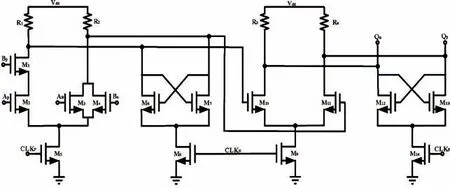

源极耦合逻辑(SCL)电路由两个锁存器级联组成,其电路原理图如图4 所示,其中M1和M2,M8和M9为两对采样对管,采样管负责信号的输入输出,信号从其栅极差分输入,漏极差分输出;M3和M4,M10和M11为两对交叉耦合对管,也被称作锁存管,为环形电路提供负阻,确保电路能保持振荡,并形成正反馈。锁存管会锁定前一时刻采集到的信号,当下一个时刻时钟信号到来的时候,前一时刻采集到的信号才能被发送到下一级。R1,R2,R3,R4为负载电阻,也被称作上拉电阻,电阻有两方面的作用,一方面会形成压降,可以限制电路的输出摆幅。一方面可以通过检验电阻两端的电流检验环路的自谐振情况[10]。

图4 SCL 电路原理图Fig.4 SCL schematic

MOS 管M5和M6,M12和M13为两对时钟输入对管,其中M5和M13接正向时钟信号CLKP,M6和M12接反向时钟信号CLKN,MOS 管M7和M14作为尾电流源,其作用主要是在直流偏置电压的控制下,为电路提供稳定的工作电流。

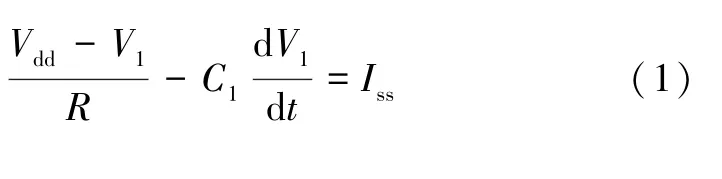

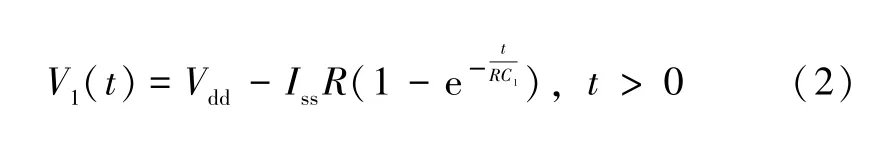

整体电路可分为三部分:由电阻组成的上拉网络,MOS 管组成的下拉网络和恒定电流源[11-12]。SCL 电路是一种静态的差分结构,在任意时间,电流仅会导向其中一条支路,导向哪条支路取决于输入的时钟信号和下拉网络要实现的逻辑[13]。没有电流导向的支路输出恒为Vdd,而电流导向的支路由于上拉电阻的存在,输出电压被限制在Vdd-IssR。图5 为锁存器等效电路,A,B 节点与图4 中的A,B 节点相对应。C1,C2为A,B 两点的寄生电容,V1,V2分别表示两条支路的电压,Iss表示尾电流源,R为上拉电阻的阻值。

图5 输出信号从高到低阶段的等效电路图Fig.5 Equivalanet circuit when output singal changes state from “high” to “low”

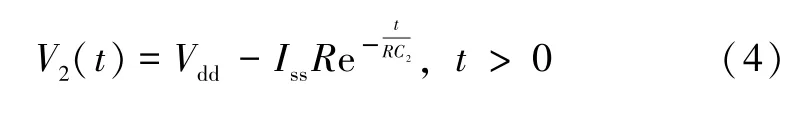

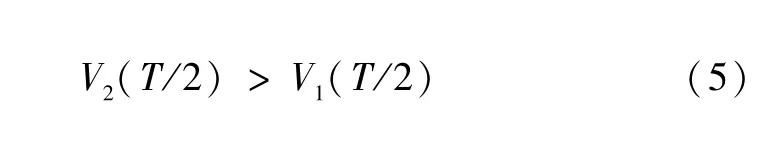

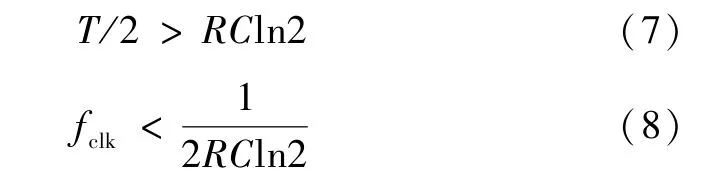

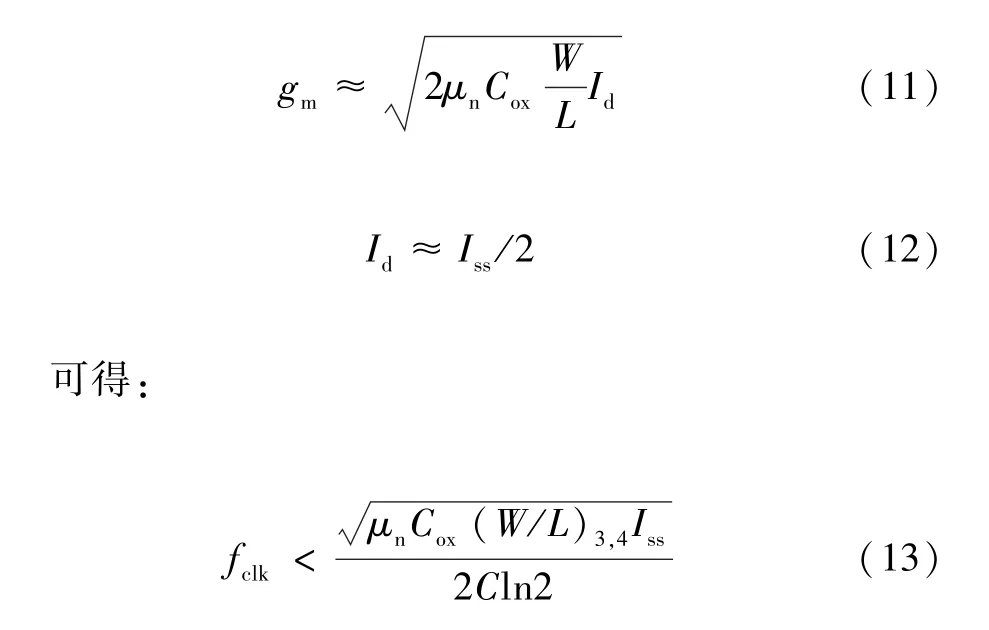

下面分析电路工作频率的影响因素,首先定义输出“高” 和“低” 的值。当t=0 时,时钟信号变高,输入D 为高,C1会放电至Vdd-IssR,该电压为低。同理,C1充电时直到Vdd停止,该电压为高。假设在t<0时,输出Q 是低,那么C1被充电至高,C2会放电为低,V1(0)=Vdd,V2(0)=Vdd-IssR。假设MOS 管足够快速切换电流。当t=0+时,电流通过M1流向M5,在0 将初始条件V1(0)=Vdd代入一阶线性微分方程(1),解得: 同理在B 点应用KCL 可得: 将初始条件V2(0)=Vdd-IssR代入式(3)可得: 因此半个时钟周期长度必须满足: 当式(5)的条件满足,锁存电路导通后,V2(t)将进一步增大,V1(t)继续放电,输出会锁定为高。定义V1(t)放电电压和V2(t)充电电压相等时的时间为Tr,时钟周期必须满足T>Tr。将式(2)和(4)代入式(5),可得: 从式(6)中可以看出C1,C2的不同主要是来源于MOS 管M1和M2导通和关断的差异,C1=C2时结果最优,假设C1=C2=C,代入式(6)可得: 从式(8)中可以看出降低电阻R可以提高电路的工作频率,但R的大小与起振条件息息相关,主要取决于交叉耦合管,交叉耦合管为电路提供负阻,从而和正电阻抵消,保证电路环路增益始终大于1[14-15],所以起振条件应满足: 式中,gm3,4为MOS 管M3和M4的跨导。将式(9)代入式(8)可得: 在锁存阶段开始时,Iss均等地流过M5和M6,M3和M4对称的栅极和漏极电势相等,M3和M4应处于饱和区,将式(11)和(12)代入式(10): 从式(13)可以看出,最高频率随着Iss的增大而增大,但增大Iss的同时,功耗也会增加。而且,在固定电源电压下,Iss的值增加到某一水平时,只有增加MOS管的尺寸才能有限增大工作频率,但这同时又会增加电容C的值。本文通过适当减少C的大小来提高工作频率,在保证M1和M2跨导足够强大可以快速切换电流的条件下,通过减小M3和M4的尺寸,使得C降低。 集成门电路的电路原理图如图6 所示。其中M1和M2组成了与门,M3和M4组成了或门。把门电路作为独立的模块加入电路中会降低信号传输的时效性,且增加电路版图的负担,增大芯片的面积。集成门电路的SCL电路不仅使得电路结构设计更简便,而且消除了逻辑门模块带来的寄生参数,仿真结果表明这种结构的D 触发器相比普通结构,其工作速度提高了10%~20%[16-17]。 图6 集成门电路的SCL 电路原理图Fig.6 SCL circuit with integrated gate schematic 模式控制电路原理图如图7 所示,电路相当于三输入或非门。其中An、Ap、Bn、Bp用来控制第四个触发器是否接入电路,进而控制电路工作在4/5 还是8/9 分频模式;Cn、Cp控制电路工作在奇数分频还是偶数分频模式。 图7 模式控制电路原理图Fig.7 Mode control schematic 芯片版图设计优先考虑总体版图布局,版图设计也遵循电路原理图的结构,以D 触发器为最小单元,也就是最小模块。因为SCL 电路是一种全差分结构电路,版图的设计应该格外注意电路的对称和匹配。此外,在满足电流密度的前提下,需要尽可能减小连线的寄生参数和连线之间的耦合[18-19]。图8 为分频器电路的整体版图,芯片尺寸仅为120 μm×150 μm。 图8 芯片版图Fig.8 Chip layout 基于TSMC 0.18 μm 工艺,应用Cadence Spectre工具对电路进行仿真。在27 ℃,电源电压Vdd=1.8 V下,仿真波形如图9~12 所示。图9 为输入8 GHz 下5分频模式输出仿真图,图10 为输入7 GHz 下4 分频模式输出仿真,图11 为输入3 GHz 下9 分频模式输出仿真,图12 为输入2 GHz 下8 分频模式输出仿真。结果表明,电路在四种模式下均能正确分频,最高工作频率可达8 GHz,每个D 触发器尾电流源为50 μA,单个电阻阻值为1.6 kΩ,整体电路功耗为6 mW。 图9 输入时钟8 GHz 下5 分频模式输出仿真图Fig.9 Simulation result of 5-divider mode at 8 GHz clock input 图10 输入时钟7 GHz 下4 分频模式输出仿真图Fig.10 Simulation result of 4-divider mode at 7 GHz clock input 图11 输入时钟3 GHz 下9 分频模式输出仿真图Fig.11 Simulation result of 9-divider mode at 3 GHz clock input 图12 输入时钟2 GHz 下8 分频模式输出仿真图Fig.12 Simulation result of 8-divider mode at 2 GHz clock input 表1 是该预分频器与不同文献预分频器的参数对比。从表1 中可以看出本文设计的预分频器极大地拓宽了预分频器的分频范围,功耗较小,面积较小,性能更优。 表1 预分频器参数对比Tab.1 Parameter comparison of prescaler 本文提出了一种集成4/5 和8/9 的预分频器设计方案。基于SCL 结构设计了基本D 触发器和集成门电路的D 触发器,并采用异步逻辑构成了4/5 分频器和8/9 分频器,通过传输门和模式控制模块把两个电路整合为一个电路。仿真结果表明所设计的预分频器在功耗和工作频率上均优于传统的CMOS 分频器。该电路最高工作频率可以达到8 GHz,降低了功耗,减少了芯片的面积,拓宽了电路的分频范围,节约了成本,更符合现代电路对分频器的需求。

2.2 集成门电路的SCL D 触发器电路

2.3 模式控制电路设计

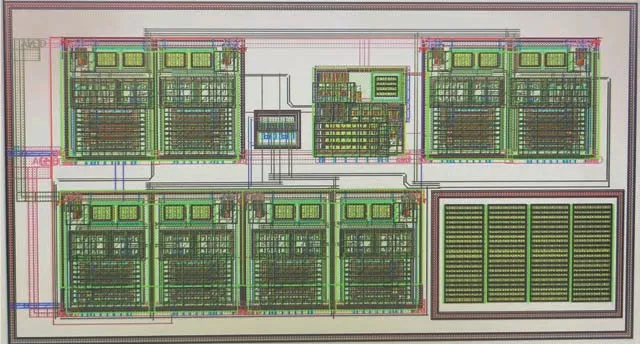

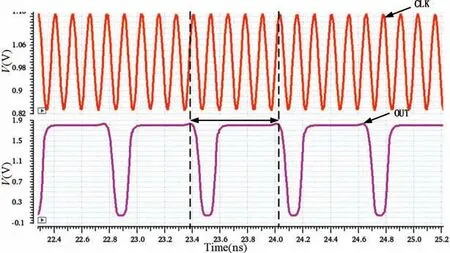

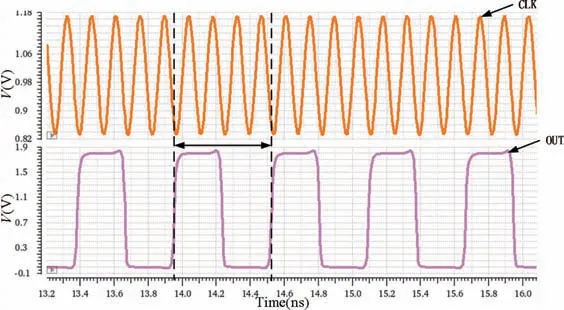

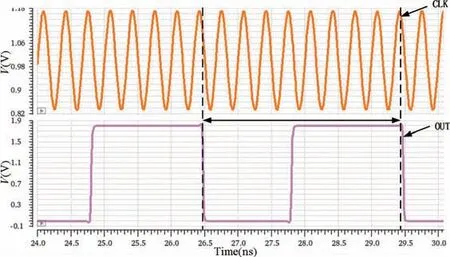

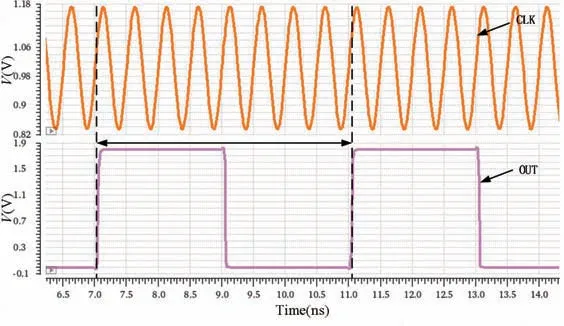

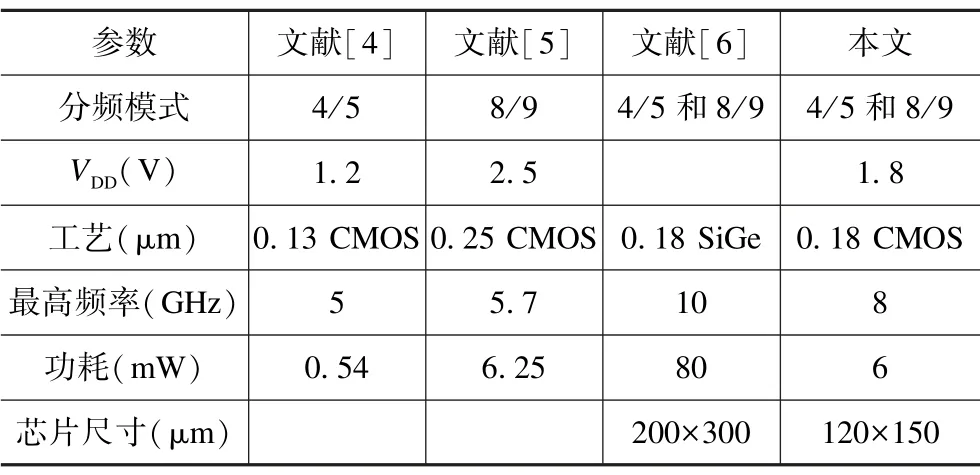

3 芯片版图设计及电路仿真

4 结论