基于反激式AC-DC 开关电源中运放电路设计*

吴启琴,沈克强,赵俊霞,孙小羊

(1.三江学院,江苏 南京 210012;2.东南大学,江苏 南京 210096)

模拟IC 的基本单元电路模块之一便是运算放大器,其因拥有输入阻抗高、输出增益高、输出阻抗较低等优势,一直是电子行业中研讨的热门话题。在开关电源电路中,检测谐振的谷底位置之前,先将辅助绕组上,经分压网络对输出电压值采样得到反馈电压VFB,再用开关电容放大电路对反馈电压VFB 进行放大,最后将放大后的VFB 与电容上的电压进行比较,从而得到谷底位置。由上可知,运放电路性能的好坏对开关电源电路能否正常运作起直接作用。随着科学技术的发展,运算放大器在实际中的运用越来越广泛,如V/I 转换器、有源滤波器、微积分电路等。现今,高性能、低成本的运算放大器已在市场中占据了重要地位。

1 两级运放电路设计

运放一般是偏置电路,由输入级、中间级、输出级所组成,其中偏置电路为运放正常工作供给适宜的直流电压;一般在输入级运用差动放大来获得比较高的电源抑制;此外,将有源负载电路作为中间级,使运放的放大倍数得到提高;输出级常采用互补对称结构电路,有利于电路进行负载的驱动,其原理见图1。

图1

图1(a)偏置电路为(b)提供合适的VB 值,使运放处于正常的直流工作中。此外,因希望运放的输出摆幅大些,则会使Vp 的值小于VB,而(a)中的M12 管工作在线性区,等效于电阻的功能,从而使VD13的值拉低,有VD13≈Vp,M11 与M12 管构成电流镜,M11 管为M12 管提供合适的偏置电压使其工作在线性区。图(b)的两级运放采用了频率补偿的原理,电路中第一级放大由M1~M5 组成,其中M3、M4 管组成电流镜结构,将输入电流进行比例放大,又因M3 和M4 管对称,所以使VD3与VD4两点的电压在Vin 的共模输入范围内,不再伴随Vin 而发生改变,从而给运放的下一级放大供给稳定的偏置。M5 是尾电流源,为跨导管提供直流偏置,其上的电流被M1 和M2 管平分;第二级放大由M6、M7 管组成,M7 为负载管,M6 为共源放大管,C0为引入的米勒补偿电容,此可有效将主极点与非主极点进行分离,R0为调零作用,其可将右半平面中的零点转移至左半平面。一、二级放大器之间补偿网络的使用,使相位裕度稳定在60°左右。

利用Cadence 仿真软件,采用CSMC 0.5μm 工艺对两级运算放大器进行研究与设计,并且使其满足表1 所示的性能指标要求。

表1 两级运放的性能指标(tt)

由CSMC 0.5μm 工艺库可知,nmos 器件模型主要参数:最小沟道长LMIN=0.5μm,栅氧厚度TOX=1.28×10-8m,阈值电压VTHN=0.719V,迁移率系数U0=4.04×10-2cm2/v·s;pmos 器件模型主要参数:最小沟道长LMIN=0.55μm,栅氧厚度TOX=1.24×10-8m,阈值电压VTHP=-0.972V,迁移率系数U0=2.15×10-2cm2/v·s。

由上可知:

相位裕度的计算:

已知一个两级运放有两个极点和一个RHP 零点,若要求相位裕度达到60°及以上,假设零点超过10GB,则有第二极点超过2.2GB。

由60°的相位裕度得到:

假设运放的单位增益频率为GB,用其替代ω 可得到:

若A(v0)很大,上式可化简为:

所以有:

由频率响应可知其零极点为:

为保证相位裕度能达到60°及以上,则有:

此次设计取CL为800fF,为获得足够的相位裕度,选择C0为900fF。

此次设计取得ID5为11uA,则ID1、ID2、ID3、ID4为5.5uA。

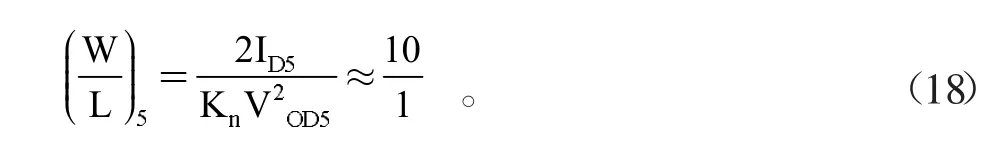

因为M5 管处在饱和区,则有:VDS5>VGS5-VTH,在线性区与饱和区的临界过驱动电压为VOD5=VDS5=VGS5-VTH,所以有:

根据共模输入电压的范围为1.2~4.8V,有Vin(cm)min=VGS1+VOD5=1.2V,且Vin(cm)min=VDD-|VGS3|+VTH1=4.8V,假设M1 管与M5 管的临界过驱动电压相等,可得出:1.2V=VOD5+VTH1+VOD5,即VOD5≈0.2,所以:

同理可算出:

可得到:

得到:

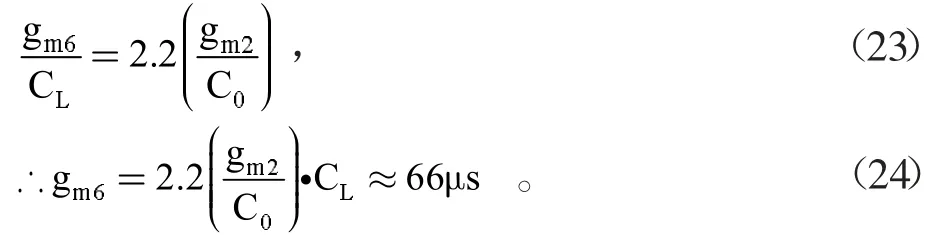

根据第二极点为单位增益带宽的2.2 倍,得到:

假设ID6=ID5=11uA,则得:

M7 管尺寸由平衡方程可得:

采用密勒补偿技术,可将右半平面的零点移动到左半平面,且略大于GB 处,一般取其1.2 倍处,此处的零点既不影响幅度特性,又为好的相位裕度做贡献,所以有:

该运放的增益为

利用Cadence 软件设计绘制的电路原理图见图2。

图2 两级运放的绘制图

2 两级运放电路仿真

2.1 共模输入范围仿真

仿真信号添加:电源上接入5V,将该电路中反相的输入端与输出端连接在一起,起缓冲的作用,正相端接入0~5V 的直流电压进行扫描,仿真后获得的共模输入范围如图3 所示。A 线代表输出信号,B 线为M5管漏源电流IDS5的波形,IDS5进入饱和区为起点,Vout随Vin 变化不再变化为终点,其共模输入范围从1.2V到4.8V,满足参数的设计指标。

图3 运放共模输入仿真波形图

2.2 输出摆幅仿真

由图1(b)可得输出摆幅:VOD7≤Vout≤VDD-VOD6。仿真信号添加:设反相比例放大器增益10,正相端接2V 直流信号,反相端接直流0~5V 进行扫描,采用负反馈方式进行运放的连接,其仿真后的波形见图4。

图4 输出电压摆幅特性波形图

由图4 可知:该运放的输出电压摆幅为0~5V,满足了设计的要求。

2.3 电源抑制比仿真

此时的运放电路处于单位增益工作状态,其正相端接入2V(DC),电源信号接入5V 的直流信号,并同时串联一个1V 的交流小信号源,其波形如图5 所示。

图5 电源抑制比特性曲线图

由图5 可见,该运放电路的电源电压抑制比为84dB,满足设计指标要求。

2.4 共模抑制比仿真

在运放开环的条件下,其正相和反相端同时接入一个1V 的交流小信号,且正相输入端同时加入一个2V 的直流信号,仿真波形见图6。

从图6 可得,运放的共模抑制比近似78dB,符合运放的设计指标要求。

图6 共模抑制比仿真波形图

2.5 运放的转换速率仿真

转换速率的仿真环境设置如下:正相端接pwl 电源脉冲;反相端与输出之间用导线相接成单位增益型,对该电路进行瞬态仿真研究,其仿真输出波见图7。

图7 转换速率仿真波形图

从仿真波形得到:在输出波形的10%和90%处,其电压分别为1.804V 和0.203V;对应的时间分别为3.232μs 和3.093μs。可得到该运放的转换速率:SR=满足设计要求。

2.6 幅频与相频特性仿真

图8 曲线反映了该运放的开环小信号放大倍数及其相位随频率的变化情况,运用RC 补偿网络,对单位增益带宽及相位裕度进行改善。仿真得到运放的相位裕度约为60°,其单位增益带宽约6.8MHz,此两级运放的低频开环增益为77dB,符合设计的指标要求。

3 结论

本文设计了一款应用于开关电源的谐振谷底检测电路中的两级运放电路,根据设计的性能要求,选择合适的电路结构,利用公式计算出运放电路的各个参数,因希望运放的输出摆幅大,设计了相应的偏置电路,采用CSMC 0.5μm 工艺,基于Cadence 平台来进行的电路设计与仿真,最后对该电路进行了仿真验证,结果符合设计指标要求。

图8 幅频与相频特性曲线图