MEDA芯片菊花链的自动容错设计

张 玲

(江西财经大学软件与物联网工程学院,江西 南昌 330013)

1 引言

MEDA芯片(Micro-Electrode-Dot-Array biochip)是新出现的一种基于微单元阵列的数字微流控芯片[1]。与传统数字微流控芯片不同,MEDA的每个微单元MC(Micro-electrode Cell)都包含驱动电极和传感检测电路,这些MC可动态分组驱动不同质量、不同形状的液滴,灵活地实现各类生化实验[2,3]。基于MEDA的原型结构已由3.3 V电平,TSMC 0.35 μm的工艺实现[3]。

随着生化协议复杂度的提高,其对MEDA芯片规模的要求也不断增加。MEDA芯片的结构涉及流体领域和电子领域,导致其更易出现多类型、高复杂性的故障。按故障发生的位置,可将MEDA芯片的故障分为2大类,即MC之间的故障和MC之内的故障[4];按故障发生的持久性,MEDA芯片的故障可分为永久性故障和间歇性故障。不同类型的故障均可能导致错误,影响整个实验结果[2]。MEDA芯片通常用于生命科学领域,必须进行全面的在线和离线测试,离线测试主要发生在制作阶段,用于测试芯片在制作完成后的正确性,而在线测试一般与生物协议实验同时进行,用于进一步提高生化实验的准确性[5,6]。

由于MEDA芯片在每个MC中嵌入了传感检测单元,因此它可在驱动液滴的同时,实现对每个液滴运行情况的实时监测。由于外部引脚面积代价较大,为减少外部引脚和增加控制能力,MEDA结构的所有微单元(MC)的一位寄存器被一个菊花链(也称为数据扫描链)串接,这个链可用最少的外部引脚100%地控制所有的阵列单元。在将驱动数据移入到每个微阵列的同时,菊花链也以同样的方式移出所有微单元的检测结果。菊花链用极少的端口实现了对所有MC的控制,但这也正是MEDA芯片的问题所在,菊花链的串接使得其故障具有全局效应,即使只有一个故障存在于菊花链上,也会带来灾难性的后果。

文献[7]首次提到了菊花链故障,并进行了故障测试,但没有给出相应的测试和诊断方法;文献[8]针对MEDA芯片设计了相对可靠的微单元系统,提高了MEDA芯片的有效性。文献[9]首次对菊花链进行初步容错设计,但未给出具体的实现过程。对MEDA结构来说,故障不仅出现在流体领域而且还会出现在电子领域,而绝大多数的电子故障会导致流体移动的异常。可靠性是MEDA芯片的重要指标之一,为保证MEDA芯片结果的准确性,不仅需要对菊花链进行全面的测试和诊断,而且需要有效的容错策略。

本文为MEDA芯片设计有效的菊花链容错结构。该结构将具有整体性的菊花链分成单个微单元,打破菊花链故障的全局性,利用测试响应自动触发容错过程,实时对故障单元进行修复,若修复失败则将其旁路,实现对菊花链中微单元的自动容错。该结构为每个微单元增加一个二选一选择器和一个与门电路,不会增加额外的外部引脚,硬件代价合理。另外,通过与电脑的接口控制诊断容错过程,可在电脑端以友好的方式监测整个测试诊断及运行过程。

2 菊花链故障全局性分析

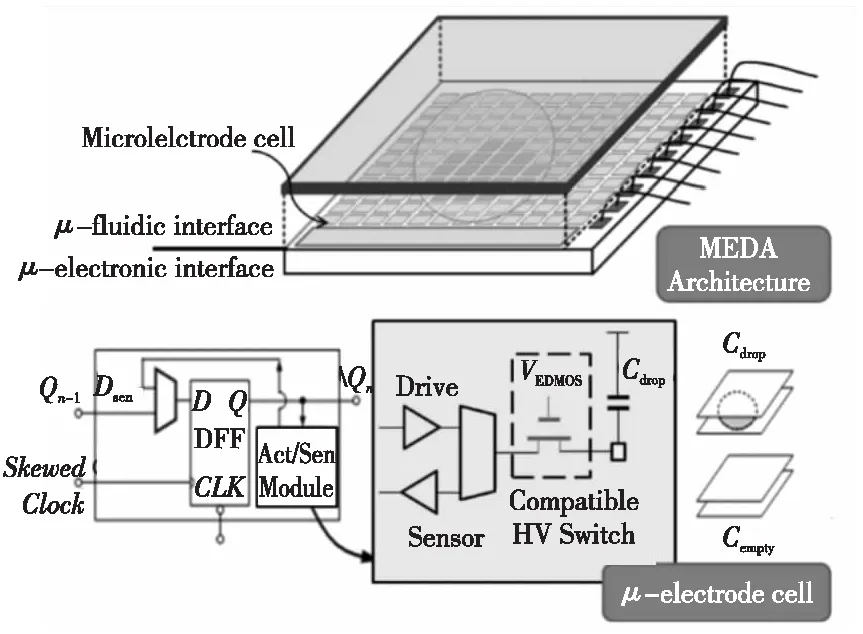

MEDA芯片基于微单元阵列结构,每个微阵列单元由驱动电路和传感监测电路组成,其示意图在图1[10]中给出,每个微阵列单元的驱动数据和检测数据被存储在其一位寄存器中,这些一位寄存器被串成可移动的数据通路,即菊花链。菊花链通过一个外部入口实现了对所有微阵列单元的完全控制,具有较高的效率,但这同时也是其问题所在。

Figure 1 Diagram of MEDA architecture图1 MEDA结构示意图

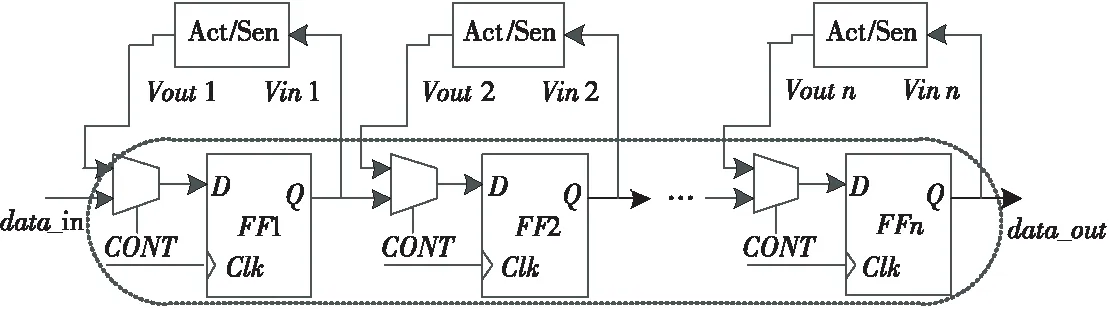

Figure 2 Daisy chain of MEDA architecture图2 MEDA结构的菊花链结构示意图

图2给出了MEDA结构的菊花链结构(用来移入微单元的驱动数据和移出检测数据)。如图2所示,在每个驱动周期,每个微阵列单元的驱动数据都通过菊花链移入到对应的一位寄存器,用来表示是否驱动相应的微单元,而检测电路检测到的数据也会存入其一位寄存器中,并通过菊花链移出。由此可见,菊花链串行移入微阵列单元的驱动数据,并移出相应的检测数据,其操作的串行性会导致其故障的全局效应。如图2所示,若FF2上出现故障,则其用来驱动微电极阵列的数据将不能串行正确地移入到FF2~FFn,此时虽然FF2的传感监测电路可能捕获到相应液滴的异常,但相应的检测结果却无法从菊花链移出,这就导致了整个微阵列的失效。MEDA芯片常用于生命科学领域,其可靠性至关重要,因此必须对菊花链进行测试诊断,并进行有效的容错设计。

3 测试响应触发的菊花链容错设计

MEDA结构的菊花链与传统CMOS电路的扫描链类似,但由于其固有属性,多数用于传统扫描链的测试和容错结构并不能直接用于MEDA结构的菊花链上。

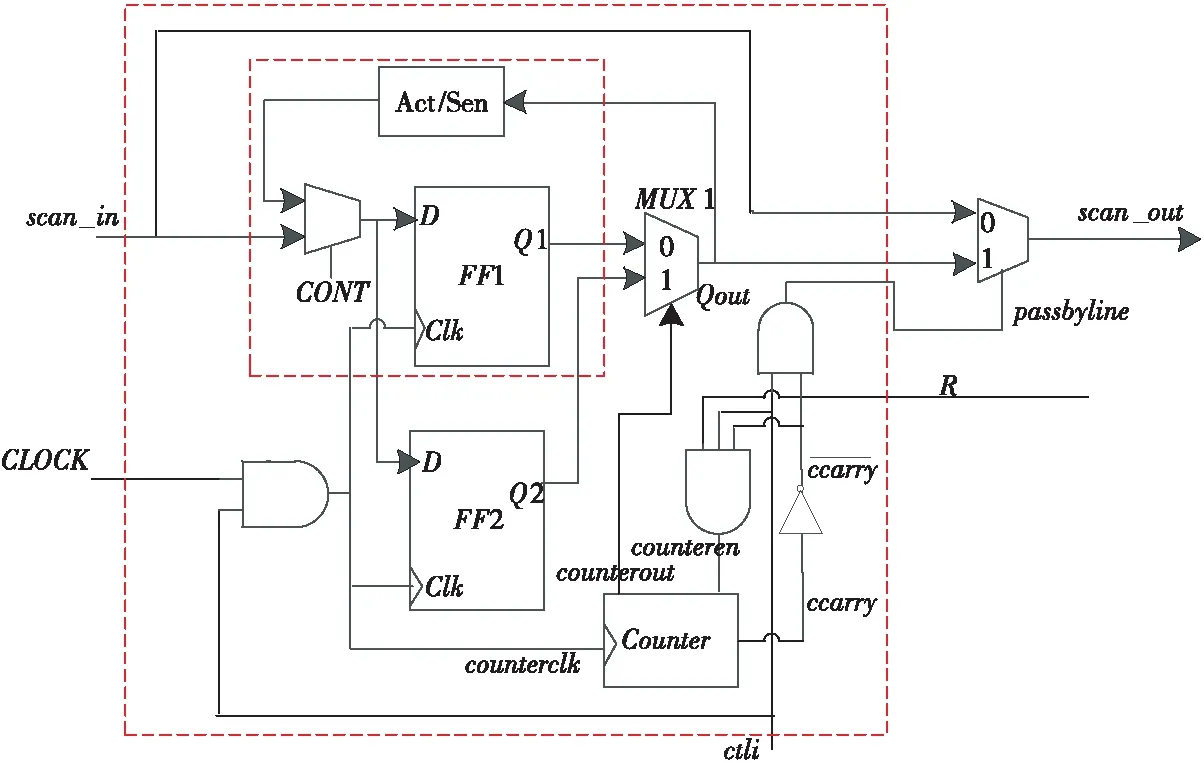

Figure 3 Illustration of the New MC architecture图3 New MC结构示意图

它们的区别主要存在于3个方面:功能不同、结构不同、对可靠性的要求也不同。功能上,传统扫描链将电路中的触发器串成用于测试的通路,其主要功能是为测试服务,而MEDA结构的菊花链是功能性的,用来传输的是功能数据;结构上,传统电路扫描链的单元之间具有其他功能路径,而MEDA结构的菊花链在未运行生化协议之前不存在任何其他功能路径;对可靠性的要求上,传统扫描链是用来传输测试数据,而MEDA结构的菊花链传输的是功能数据,且是对精确度要求非常高的实验数据,因此,它对可靠性的要求更高。

MEDA结构菊花链测试不难实现,只需用链测试模式(Chain Pattern,也称Flush Pattern,用来测试扫描链的完整性)[11]来对其进行测试,Chain Pattern本身就足以确定扫描链存不存在故障,但它不能定位故障,也不具有容错功能。而对于MEDA芯片的容错设计来说,其外部引脚的面积要比内部单元大得多,因此容错设计要以不增加外部引脚为原则。

3.1 自诊断容错的New MC结构

相对于图2中的原始扫描单元,本文称具有自诊断和容错功能的单元为New MC。如图3所示,图中较小的虚线框内为原始MC,为实现容错功能,New MC在原始MC的基础上增加了一个冗余DFF(D Flip-Flop)FF2,一个一位计数器和若干与门,如外围虚线框所示。scan_in、scan_out和CLOCK分别为扫描输入、扫描输出和时钟信号;R为scan_out与正确响应比较的结果(此处仅给出New MC结构,scan_out与正确响应的比较部分电路未画出),若相同则表示该单元不存在故障,该值为0,否则为1;ctli为该单元的访问信号,该值为1时,该单元被访问,否则该单元被旁路。其他内部信号还包括计数器时钟counterclk,计数器输出counterout,计数器使能信号counteren,计数器溢出信号ccarry,该New MC的旁路信号passbyline。

该New MC单元通过比较其输出与正确响应来确定FF1是否在在故障,若存在故障,则响应的比较结果信号R会控制Counter计数一次,从而控制MUX1的输出信号Qout从Q1转到Q2,实现容错功能。Qout=Q2会以同样的方式测试、诊断,若FF2也存在故障,则Counter会溢出,其溢出信号ccarry会控制passbyline=0,该单元被永久旁路。该New MC的具体工作过程如下所示:

初始化:

1ctli=1;

2R=0;

3counterout=0;

诊断过程:

4counterout=0;

5Qout=Q1;

6response=Qout?

7 Yes,R=0;counteren=0;goto 4;

8 No,goto 7;

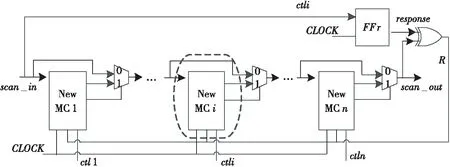

Figure 4 Data scan chain composed of New MC图4 由New MC组成的菊花链

修复过程:

9R=1;

10counteren=1;

11 falling edge ofcounterclk;

12counterout=counterout+1;

检查FF2:

10counterout=1;

11Qout=Q2;

12reponse=Qout?

13 Yes,R=0,counteren=0;goto 10;

14 No,goto 13;

旁边过程:

15R=1;

16counteren=1;

17 falling edge ofcounterclk;

18counterout=counterout+1;

19counteroverflows;

20ccarry=1;

counterkeeps holding;

The MC is bypassed.

初始ctli=1,R=0,counterout=0,如第1~2行所示;由于counterout=0,因此Qout=Q1,response为正确响应,与Qout进行比较,若正确,则R=0,该单元无故障,正常工作如第4~6行所示;若存在故障,则启动修复过程,R=1(ccarry=0,ctli=1),使能Counter,它会在时钟下降沿做一次计数操作,如第7~9行所示;Counter的计数操作使counterout=1,从而使Qout从存在故障的FF1转到FF2,即Qout=Q2,此时Qout再以同样的方式比较response与Qout,若无故障,则R=0,counteren=0;否则启动旁路过程,如第10~12行所示;此时R=1表示FF2也存在故障,Counter会在时钟下降沿计数一次,Counter溢出,ccarry=1,从而Counter的使能信号Counteren=0,该counter不会再计数,而passbyline=0,该New MC被永久旁路。

3.2 由New MC组成的菊花链

由该New MC组成的菊花链如图4所示,相对于原始菊花链,为每个New MC增加一个二选一选择器,通过控制其ctl信号可实现对每个单元的测试和诊断。其具体测试诊断过程可描述如下:

(1)i=n。

(2)第i个New MC的控制信号ctli为1,其他New MC的控制信号为0,则此时 New MCi被访问,其他被旁路。通过与FFr输出值进行比较,测试诊断New MCi。

(3)i=i-1,若i≠0,则转(2);否则退出。

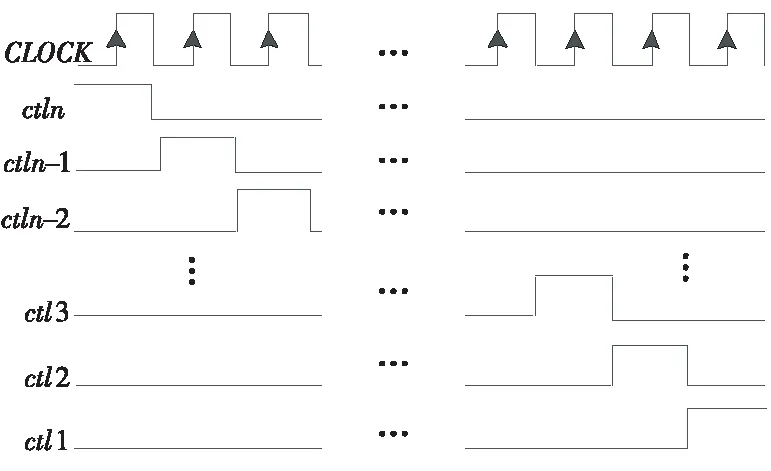

其控制信号的时序图如图5所示。如图5所示,由ctl控制New MC的轮询访问,第1个时钟周期,ctln=1,而ctl1,ctl2,…,ctln-1均为0,因此只有第n个New MC接收时钟信号,其他New MC 被旁路,此时其测试数据在送入New MCn的同时也被送入FFr,通过异或逻辑,比较两者的输出,若结果相同,表示无故障,则R=0,否则R=1,启动New MC的修复过程。第2个时钟周期,ctln-1=1,其他ctl为0,ctln-1将以同样的方式进行测试、诊断和修复。依次为ctln-2,ctln-3,…,ctl1进行测试、诊断和修复。如图5所示,ctl信号为一组相同的、时间相差1个时钟周期的信号,它们可以从CLOCK信号获得,不需要增加额外的外部信号。

Figure 5 Time sequence of the control signals of ctl图5 ctl信号时序图

3.3 容错诊断的实时监测

MEDA结构一般通过电脑端控制其运行,并通过其集成的传感检测电路实时将测试数据送到电脑端,因此实现了实时数据的监测[12]。但是,这些运行过程均依赖不存在故障的菊花链,因此必须提高菊花链的可靠性。

基于New MC的菊花链对每个单元进行分时访问,并在访问过程中实现自测试和容错过程,可用于离线和在线测试。本结构中,本文还可以在电脑端设计监听端口,实时检测每个New MC的故障、修复和旁路情况。在芯片测试诊断过程中,电脑端接收scan_out的信号,并与正确的响应进行比较,与芯片同步更新故障、容错和旁路信号,并可用不同标识在电脑端显示,从而实现对每个New MC的实时容错监测。

电脑端的测试诊断过程如下所示:

Ftj用于记录每个MC产生故障的次数;每个单元包含2个DFF;Flag用来标识是否存在故障MC。

1 初始化:所有的Fti=0;//i=1,2,…,n

2 测试遍历New MC;

3forj=0 ton

4 应用测试激励0;

5if(存在struck-at-1故障,且Ftj!=-1)

6 则Ftj=Ftj+1;

7 修复一次;

8else应用测试激励1

9if(存在stuck-at-0故障,且Ftj!=-1)

10 则Ftj=Ftj+1;

11 修复一次;

12elseif(Ftj==1)

标记该单元为修复成功单元;

13 endif

14endif

15endfor

16Flag=0;

17forj=0 ton

18if(Ftj==0)

19 标记该单元为无故障单元;

20elseif(Ftj==1)

21Flag=1;//启动下一次遍历修复

22break;

23elseif(Ftj≥2)//该单元被旁路

24Ftj=-1;

标记该单元为修复失败被旁路单元;

25endif

26endfor

27if(Flag)

28 转2;

29endif

其中,Fti用来记录第i个New MC产生故障的次数,Flag用来标识菊花链中是否存在有故障的MC。其具体过程可描述如下:初始化,所有Ft=0,如第1行所示。利用分时方法测试遍历菊花链,应用测试激励0,用来检测stuck-at-1故障,若scan_out的比较结果与正确响应不同,则对应的Ftj加1,如第4~7行所示;而若不存在stuck-at-1故障,则检测是否存在stuck-at-0故障,若存在,则相应的Ftj加1,如第8~11行所示;若既不存在stuck-at-0故障,也不存在stuck-at-1故障,则检查该单元是否已被修复一次,若被修复一次,即Ftj==1,则标记该单元为修复成功单元,如第12行所示。完成遍历后,设置标识Flag为0,检查所有New MC的Ft,若Fti=0,标记该i单元为无故障单元,如第18~19行所示;若Fti==1,则表明其对应的Qout已从Q1转向Q2,完成修复,则设置Flag=1,表示需要进行第2次测试诊断,以完成FF2是否存在故障的测试,如第20~22行所示(即只要存在1个被修复FF1,就会跳出循环,进行第2次修复)。而若Fti≥2,则表明第i个单元修复失败,已被旁路,因此设Fti为-1,标记该单元为修复失败被旁路单元,将不能再被使用,如第23~24行所示。检查Flag,若为1,则表明存在需要检查FF2的单元,启动第2次修复,否则表明该菊花链测试诊断修复完成,如26~29行所示。

4 实验结果和分析

为验证本结构的有效性,本文对30×30[12]的MEDA芯片进行实验,Multisim[13]被用来对本自诊断和容错的菊花链进行仿真,其时钟设为1 MHZ[14],高电平为3.3 V,低电平设为0 V。本文对单故障、多故障、单个New MC和多个New MC进行仿真。

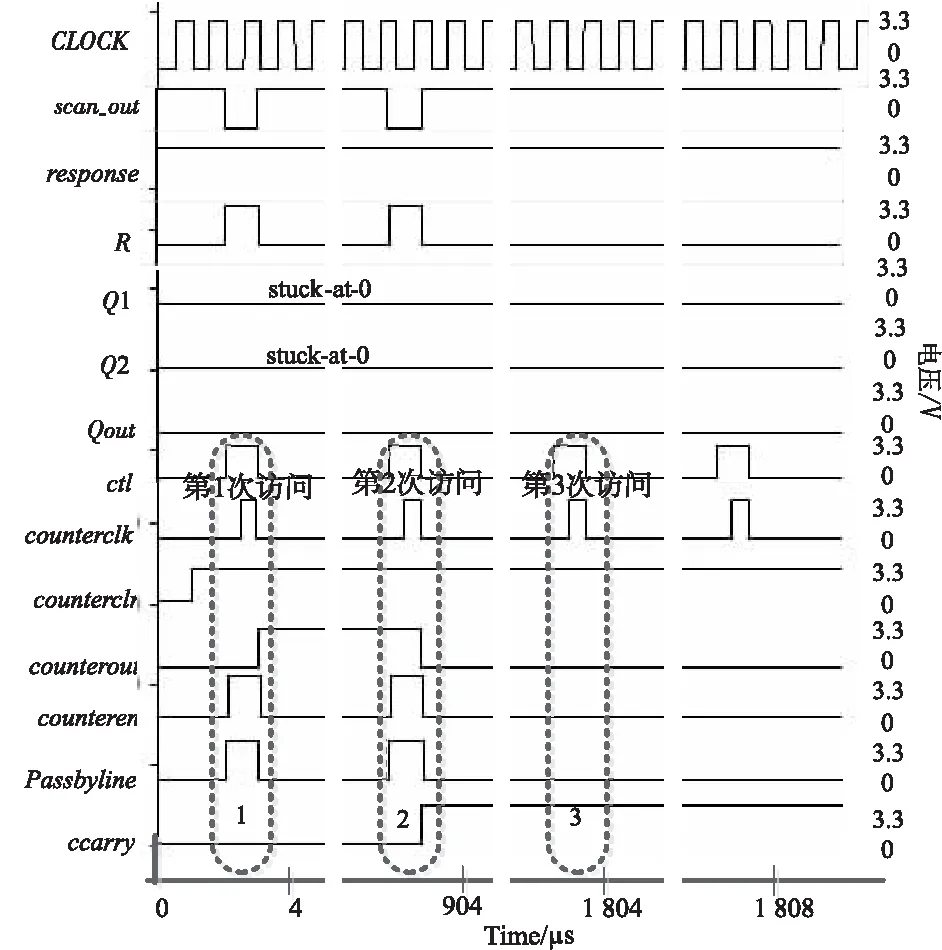

首先对出现在单个New MC上的单故障和多故障进行仿真,其仿真结果如图6和图7所示。

Figure 6 stuck-at-1 defects on single New MC图6 stuck-at-1故障出现在单个New MC上

Figure 7 Stuck-at-0 defects on signal New MC图7 stuck-at-0故障出现在单个New MC上

图6给出了New MC上出现单个故障和多个故障的仿真结果。如图6所示,图中左侧给出了所对应的信号,它们分别为时钟信号CLOCK、扫描输出scan_out、正确的响应response、故障信号R、FF1输出Q1、FF2输出Q2、该New MC的输出Qout、控制信号ctl、计数器时钟信号counterclk、计数器清零信号counterclr、计数器输出counterout、计数器使能信号counteren、旁路信号passbyline、计数器溢出信号ccarry,这些信号与图3和New MC具体工作过程中的信号对应,图6中横坐标为时间。图6表示的是New MC的FF1和FF2均存在stuck-at-1故障(仿真中FF1、FF2初始值为0,插入故障为stuck-at-1),第1次访问该New MC时,由于stuck-at-1故障与response的值不同,因此R=1,Counteren被使能,在counterclk下降沿,Counter计数一次,counterout由0变1,Qout从Q1转向Q2,该过程如图6中虚线框1所示,可见若FF2不存在故障,则修复成功。但是,FF2同样被插入了stuck-at-1故障,因此在第2次访问期间,R=1,counteren=1,使能计数器,在counterclk的下降沿,计数器又计数一次,导致该计数器溢出,ccarry=1,该过程如虚线框2所示。由于ccarry为1,导致passbyline=0,计数器的使能信号counteren=0,因此该单元被旁路,在第2次之后的访问中,该单元被永久旁路,即passbyline永久为0,如虚线框3所示。

图7给出了FF1和FF2上均出现stuck-at-0故障的仿真结果,与图6类似,在第1次访问期间,由于故障的存在使R为1,因此使能Counter计数一次,使Qout从Q1移到Q2,如图7中虚线框1所示;在第2次访问期间,FF2仍存在故障,因此R仍为1,Counter作第2次计数,造成passbyline永久为0,该单元被旁路。

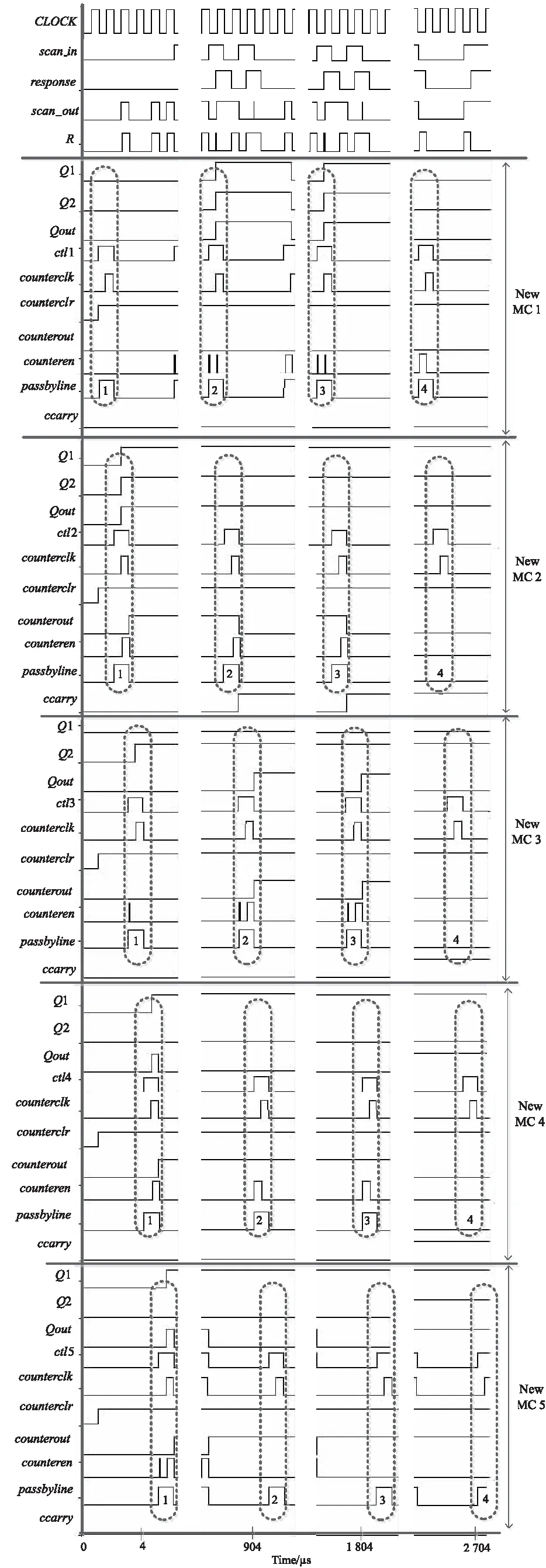

图8给出了相邻5个单元的仿真结果,其左侧仍为每个New MC对应其结构中的信号,右侧为其电压,横坐标为时间。如图8所示,最上侧的5个公共信号分别为时钟信号CLOCK、测试数据信号scan_in、正确响应信号response、数据输出信号scan_out,故障信号R。在第1个时钟周期,New MC 1被访问一次,该单元不存在故障,scan-out与response相同,因此R=0,Counter不作加法,Qout=Q1,该过程在虚线框1中给出;在第2次访问时,测试数据为1,该单元无故障,因此Counter保持为0,如虚线框2所示;可见该单元为无故障单元,因此在第3次和第4次访问中,scan_out总是与response相等,R保持为0。

第2个New MC的FF1存在stuck-at-1故障,而其FF2也存在stuck-at-1故障,因此在第1次访问时,其故障信号R=1,在counterclk下降沿,Counter计数一次,Qout转向FF2,如虚线框1所示;FF2同样存在stuck-at-1故障,因此在其第2次的访问中(如虚线框2),其数据输出与正确响应不同,故障信号R=1,计数器在counterclk的作用下第2次计数,因此导致其溢出信号ccarry为1,从而使得passbyline永久为0,该单元在之后的访问中将被永久旁路,如虚线框3和4所示。

第3个New MC的FF1存在stuck-at-0故障,FF2存在stuck-at-1故障,在其第1次访问时,应用的测试数据为0,因为其输出与response相同,因此R=0,Counter未做加法操作,如虚线框1所示;在第2次访问时,应用测试数据1,由于FF1存在stuck-at-0故障,因此其输出与response不同,R=1,Counter会在其时钟下降沿计数一次,从而其Qout从FF1转向FF2;在第3次访问中,测试数据为0,而FF2存在stuck-at-1故障,因此数据与响应不同,R为1,计数器会计数一次,溢出信号ccarry为1,如虚线框3所示;在之后的访问中,该单元将会被旁路,如虚线框4所示。

第4个New MC的FF1存在stuck-at-1故障,FF2存在stuck-at-0故障。在第1次访问时应用测试数据0,FF1的stuck-at-1故障与response不同,R为1,Counter计数一次,Qout转向FF2,如虚线框1所示;在第2次访问时,应用测试数据0,FF2存在stuck-at-0故障,其数据输出与response相同,R=0,其计数器将不会计数,如虚线框2所示;在第3次访问时,应用测试数据1,其stuck-at-0故障将导致R为1,因此计数器会计数一次,从而ccarry为1,如虚线框3所示;ccarry=1之后的访问中,该单元将会被旁路,如虚线框4所示。

Figure 8 Defects on multiple New MCs图8 多个MC产生故障容错仿真结果

第5个New MC的FF1存在stuck-at-1故障,而FF2为正确单元。第1次访问时,应用测试数据0,因此可检测出FF1的stuck-at-1故障,R=1,计数器计数一次,Qout从FF1转到FF2,如虚线框1所示;在第2次访问时应用测试数据0,第2个单元为正确单元,R=0,计数器不计数,如虚线框2所示;第3次访问时,应用测试数据1,该数据输出与response相同,R=0,计数器不计数,如虚线框3所示;第4次访问时,应用测试数据1,DFF为无故障单元,R=0,计数器不计数,如第4个虚线框所示。

从仿真结果来看,该结构能对MEDA芯片的菊花链进行测试、诊断和修复,并在修复不成功时,将该单元旁路。另外,New MC总的综合面积为2 012.34 μm2,小于微阵列单元的面积(2 500 μm2)[9],因此是满足设计要求的。

5 结束语

本文针对点阵数字微流控芯片的菊花链提出可自测试、诊断和容错的结构,该结构可实现对菊花链故障进行测试,有故障出现时,可进行自修复,修复失败时会将该单元旁路。本文还给出了电脑端的实时监测测试修复过程,通过该过程可以友好地在电脑端对菊花链的状态进行实时观测。仿真结果表明了该结构的有效性。