有机单晶电路的研究进展

林城策,彭博宇,李寒莹

(浙江大学高分子合成与功能构造教育部重点实验室,高分子科学与工程系,杭州 310027)

有机半导体材料具有易加工、成本低、质轻及柔性等优点,从面世起便受到了学术界和工业界的关注.有机半导体材料通过分子间相互作用形成聚集态.相比于无机材料中的离子键和共价键,有机半导体材料的分子间相互作用通常较弱,能通过溶液法加工,因此更适用于大面积薄膜的制备[1~3].加工条件和工艺的简化降低了设备和能源上的投入,使有机电路具有较低的生产成本.此外,与聚合物基底较好的兼容性(润湿性好,热膨胀系数相近等)使有机半导体材料成为制备柔性器件的首选[4~6].但与无机材料相比较低的迁移率使有机半导体难以应用于高频集成电路;此外,较差的溶剂耐受性和热稳定性也使其难以兼容传统的光刻技术,因而制约了高密度的集成.这些特点使得有机集成电路更适合应用于必须具备柔性、轻便及低成本等特性但对工作速度要求不高的场景,如柔性显示器[5,7,8]、射频识别标签(RFID)[9,10]、传感器[11~13]等.这些场景随着物联网、智能穿戴和生物化学传感等技术的发展变得越来越发重要与普遍.

与无定形或多晶有机半导体材料相比,单晶材料的显著优势在于长程有序的分子排列、较小的缺陷态密度及消除了晶界的影响,从而表现出更高的迁移率、稳定性和均一性[14~16].场效应晶体管(FET)作为集成电路中最小的工作单元,对于上述性能有非常高的要求:较高的迁移率意味着工作频率和运算速度的增加,可适应更广泛的应用场景;较好的稳定性可减少阈值电压漂移,降低对封装工艺和工作环境的要求[17,18];较好的均一性可简化电路设计,从而能够利用更少的FET 实现更多的逻辑功能.可见,有机单晶对于有机集成电路的发展和应用具有重要的意义.

本文将着重对近年来有机单晶在逻辑电路和集成电路中的研究进展进行综合评述,讨论其在发展中遇到的挑战和相应的应对方法,并对有机单晶电路未来的发展进行展望.

1 有机单晶门电路

以FET为基础的门电路是数字电路中最小的逻辑单元,也是研究集成电路过程中基础的一步.目前,关于有机单晶电路的研究大多数集中于门电路(特别是结构最简单的反相器,即非门),而关于更加复杂电路的研究则较少.因此本文将主要讨论有机单晶门电路的研究.

根据电路中沟道类型的异同,有机集成电路可分为单极性电路[19~21]和互补电路[22,23]2种.单极性电路中只存在一种沟道类型(如p型,即空穴型沟道),往往只由一种半导体材料构成;而互补电路中需要同时具备p型和n型(即电子型)两种沟道类型,可由一种或多种半导体材料组成.与单极性电路相比,互补电路具有更低的功耗和更好的电路稳定性,是有机电路发展的趋势.下面将以互补电路为例介绍常见逻辑门电路的基本结构和参数.

1.1 门电路基本结构

1.1.1 非门(反相器)非门是门电路中结构最简单的一种.它可以实现输入和输出之间高低电平的彩转换,因此也被称为“反相器”.反相器可由两个FET串联得到.互补反相器的结构如图1(A)所示.互补反相器的工作原理如下:假设p 型FET(p-FET)的阈值电压为Vth,p,n 型FET(n-FET)的阈值电压为Vth,n,并且│Vth,p│=Vth,n.只有当电源电压VDD>Vth,n+│Vth,p│时,反相器才能正常工作.当输入电压Vin<Vth,n时,│VGS1│<Vth,n,│VGS2│>│Vth,p│(其中VGS1为栅极G和S1之间的电压;VGS2为栅极G和S2之间的电压),此时n-FET截止,p-FET开启,n-FET的沟道电阻远大于p-FET的沟道电阻,n-FET分得VDD中绝大部分电压,即输出电压Vout≈VDD.当输入电压Vin>VDD-│Vth,p│时,情况相反,有Vout≈0.而在Vth,n<Vin<VDD-│Vth,p│的中间区域,n-FET与p-FET均处于导通状态.在此范围内,随着Vin的增大,n-FET两端的分压将发生剧烈变化,Vout出现由高电平至低电平的迅速翻转[图1(B)].

Fig.1 Structure of complementary inverter(A),transfer characteristic(black) and gain characteristic(red)of complementary inverter(B)

电压转移特性曲线转折区域的中点(Vout=VDD/2)对应的输入电压被称为反相器的阈值电压(VTH).此时,p-FET 和n-FET 同时开启且具有相同的内阻,经过反相器的漏极电流具有最大值.理想情况下,VTH=VDD/2,但由于两个FET的各参数存在差异,VTH往往会偏离理想值.有机互补反相器的VTH可以用下式进行计算:

式中:β为跨导参数,β=μCW/L,其中μ(cm2·V-1·s-1)为FET 迁移率,C(F)为FET 绝缘层电容,W(m)和L(m)分别为FET的沟道宽度和沟道长度[24~26].

电压增益(Gain)是反相器的关键性能参数,即Vout对Vin的一阶导数,用来量化输出电压翻转的速率.在电路应用中,较大的增益可提高反相器驱动后续门电路的能力,并提高反相器用于放大电路时的电压放大能力.通过提高栅绝缘层的电容值来降低晶体管的工作电压,或通过降低陷阱浓度来改善晶体管的亚阈值摆幅,均可有效提高反相器的电压增益[27].

噪声容限是反相器的另一个重要参数,反映了反相器对信号的抗干扰能力[28].假设在一个电路中有两个参数相同的反相器,前一级的输出即后一级的输入.此时只有前一级输出高电平的最小值(VOH,min)大于后一级输入高电平的最小值(VIH,min),才能使后一级正常输出低电平.此输出和输入高电平的差值,即高电平噪声容限:VNH=VOH,min-VIH,min.同理,前一级输出低电平的最大值(VOL,max)应该小于后一级输入低电平的最大值(VIL,max),才能使后一级正常输出高电平.此时输入和输出低电平的差值,即低电平噪声容限:VNL=VIL,max-VOL,max.噪声容限越大,器件越能在外界因素干扰下进行正确的逻辑运算,即器件具有越好的抗干扰能力.

1.1.2 其它门电路 为了实现更丰富的逻辑功能,除了非门外,数字电路中还需要用到与非门(NAND)、或非门(NOR)、与门(AND)、或门(OR)等门电路.NAND 由2个并联的p型晶体管和2个串联的n型晶体管组成,可以实现2个输入端A、B和输出端Y之间的与非逻辑关系[图2(A)];NOR由2个并联的n型晶体管和2个串联的p型晶体管组成,可以实现2个输入端A、B和输出端Y之间的或非逻辑关系[图2(B)];在NAND 和NOR 的输出端连接一个反相器,则可以实现输出电平的反转,即得到AND和OR[图2(C)和(D)].

Fig.2 Gate structures and the truth tables of NOR(A),NAND(B),OR(C),and AND(D)

综上所述,晶体管是逻辑门电路中的最基本的组成部分.晶体管性能的优劣,包括迁移率、阈值电压和亚阈值摆幅等,直接或间接地决定了对应逻辑门电路的性能表现.其中,较高的迁移率可提高逻辑电路的运行速度,较低的阈值电压有利于降低电路的功耗,较低的亚阈值摆幅则可以增大反相器的增益.因此,提高晶体管的各项性能指标是发展有机逻辑电路的重中之重,也是研究者致力于有机单晶场效应晶体管研究的一大原因.

1.2 有机单晶单极性电路

在有机半导体发展过程中,空穴传输材料凭借更好的环境稳定性和载流子传输性能,研究进展领先于电子传输材料[29~32].因此,多数关于有机单晶单极性电路的研究对象为空穴传输材料.

Jiang等[33]用物理气相传输法生长得到了p型的双(苯基乙烯基)蒽[DPV-ant)]片状单晶.这种单晶尺寸在几十微米左右,具有平整的表面和较好的柔性.用这种单晶制得的有机场效应晶体管(OFET)最高空穴迁移率可达4.3 cm2·V-1·s-1.通过机械转移单晶和电极的方法,Jiang 等制备了单极性的反相器.该反相器可在VDD为2.5~40 V的范围内工作,其最大电压增益为80左右.

Zhao等[34]提出了一种制备可转移电极的方法,可将沉积了金属电极、绝缘层等结构的柔性基底转移到各种复杂曲面上.他们以物理气相传输法生长得到的长条形红荧烯单晶薄片为半导体层,通过用探针将有机单晶转移到柔性基底上的方式,在各种曲面上制备了FET和单晶门电路[图3(A)和(B)].制得的FET最高空穴迁移率可达23.9 cm2·V-1·s-1.以此制备的单极性反相器表现出很好的工作稳定性(迟滞效应很小)以及较大的噪声容限.在VDD=-50 V的情况下,其电压增益可达23.5[图3(C)].此外,他们还采用相同的方法制备了与非门(NAND)和或非门(NOR)电路,得到的电压转移特性与相应的真值表之间有良好的一致性[图3(D)~(I)].

Fig.3 3D optical microscopy image(A),magnified optical image of an inverter(B),static voltage transfer characteristics and the corresponding signal gain of the inverter operated at VDD=-20 V(C),static voltage transfer characteristics at VDD=-20 V for NAND gate(D) and NOR gate(G),dynamic switching characteristics at VDD=-20 V for NAND gate(E)and NOR gate(H),logic truth tables for NAND gate(F)and NOR gate(I)[34]

早期的工作多采用手工转移单晶的方法来制备单晶门电路.这种方法虽然可以比较容易地将晶体转移到所需位置,但转移的精度和效率无法满足密度更大、结构更复杂的电路的需求.

Kang 等[35]在经过图案化处理的聚甲基丙烯酸甲酯(PMMA)牺牲层上,对旋涂得到的2,7-二辛基[1]苯并噻吩并[3,2-B][1]苯并噻吩(C8-BTBT)薄膜进行了溶剂蒸汽退火处理,获得了C8-BTBT棒状单晶阵列.用单根晶体制得的FET 的空穴迁移率可达2.91 cm2·V-1·s-1.在制备门电路时,通过设计PMMA牺牲层的图案化,可以控制沟道内单晶的数量,从而获得想要的器件沟道尺寸.利用上述方法,Kang等研究了反相器中负载晶体管不同沟道宽长比对电压增益的影响,发现减小负载晶体管沟道宽度(减少沟道内晶体的数量),即减小沟道宽长比,可以使反相器增益由1.31提升至1.86.该结果与电路模拟结果一致.

单极性有机单晶电路的优势在于,只需沉积一种半导体单晶(多数为p型)即可实现相应功能.考虑到n型有机半导体材料较难沉积,且较低的电子迁移率很难匹配较高的空穴迁移率,这种单极性有机单晶电路无疑是早期研究中较为理想的结构.但单极性电路的静态功耗较高,电极和绝缘层的制备流程也较复杂,制约了有机集成电路向低功耗、低成本和高密度方向的发展.

1.3 有机单晶互补电路

互补电路具有功耗小、占用空间小、实现功能所需的晶体管少、布线简单、系统寿命长等优点,是集成电路中重要的组成部分[1].为了实现互补功能,电路中需要同时有p型和n型沟道的晶体管,因此对半导体沉积工艺具有较高的要求.以最基本的互补反相器为例,若负载管和驱动管分别只能传输单一种类的载流子,则称为单极性互补电路;而若电路中只由同一种双极性沟道晶体管(根据栅极电压的不同,既可传输电子也可传输空穴)实现互补功能,则称为双极性互补电路.

1.3.1 单极性单晶互补电路 单极性互补电路中,晶体管只能传输特定一种载流子,所以采用2种单晶材料(分别为电子型半导体和空穴型半导体)构成互补电路是较直接的途径[36,37].

Briseno 等[38]通过物理气相传输法分别得到了p 型的四甲基并五苯(TMPC)单晶和n 型的N,N′-双(2,4-二氟苯基)苝-3,4,9,10-四羧酸二酰亚胺(PTCDI)单晶.随后,他们将2种有机单晶手动转移至目标基底上的特定位置,制得了底栅底接触结构的FET 和互补反相器.p 型晶体管的空穴迁移率可达1.03 cm2·V-1·s-1,而n型晶体管的电子迁移率仅为6×10-3cm2·V-1·s-1.互补反相器可以实现电压翻转功能,在VDD=30 V时,电压增益为4.2.较低的电压增益是由n型晶体管电子迁移率过低导致的电子和空穴迁移率不平衡造成的.

Tang 等[39]采用气相法制备了酞菁铜(CuPc)和十六氟代酞菁铜(F16CuPc)的单晶纳米线.通过纳米机械操纵转移方法,半导体纳米线和SnO2∶Sb 电极纳米线被精准转移到沉积有栅极和绝缘层的基底上,制得了底栅顶接触的OFET.其中,电子迁移率为0.65 cm2·V-1·s-1,空穴迁移率为0.1~0.61 cm2·V-1·s-1.使用2根半导体单晶纳米线、6根电极纳米线和2个独立栅极的组合,可以形成2个n型沟道和2个p型沟道.通过输入、输出端的选择,可以得到不同功能的门电路,包括非门、或非门、与非门及静态存储器(SRAM)等[图4(A)和(B)].得到的器件具有较低的工作电压和功耗以及较好的稳定性[图4(C)~(I)].

Fig.4 Schematic diagrams(A) and SEM image(B) of organic single crystal circuits assembled by using nanowires of CuPc,F16CuPc,and SnO2:Sb as building blocks,static voltage transfer characteristics and gain of an inverter at VDD=20 V(C),circuit schematic diagrams of NOR(D) and NAND(G) logic gates,transfer(E) and dynamic switching(F) characteristics of a NOR gate at VDD=10 V,transfer(H)and dynamic switching(I)characteristics of a NAND gate at VDD=10 V[39]

Park 等[40]提出了利用极性液体的毛细作用转移在模板中生长的单晶纳米线的方法(LB-nTM).在预先制备好的模块化聚合物模板中通过蒸发溶剂的方式使有机半导体结晶形成单晶纳米线,再利用极性液体的毛细作用将纳米线转印到目标基底上,即可制得想要的纳米线阵列.利用这种方法,Park等在聚合物基底上制备了FET和反相器等阵列.其中,由C60和6,13-双(三异丙基甲硅烷基乙炔基)并五苯(TIPS-PEN)单晶纳米线构成的互补反相器电压增益为10.采用同样方法转移得到的聚合物纳米线电极宽度仅为90 nm,其较低的电导率和较小的接触面积使制得的单晶OFET性能并不理想,两种沟道的迁移率并不平衡,这些原因导致了制得的反相器电压增益并不高.

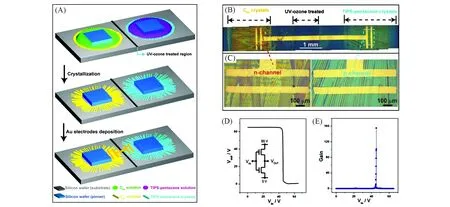

在上述工作的基础上,Park 等在LB-nTM 法的基础上结合喷墨打印的方法[41],提出了喷墨辅助纳米转印法(inkjet-NTP).通过向模板中喷墨打印半导体溶液,可以更好地控制溶液的分布和结晶,甚至可以在同一模板中得到不同种类的单晶纳米线[图5(A)~(C)].他们还改进了电极沉积的方法,利用喷墨打印的方式可以直接将银电极打印在特定位置,增大了电极和纳米线的接触面积.在此基础上,作者首次在单一基底上集成了由多种单晶纳米线构成的器件阵列,包括FET、互补反相器、p-n二极管及应变传感器等[图5(D)].其中各种晶体管的性能均有较大的提升,可达到正常单晶FET的水平.由C60和TIPS-PEN单晶纳米线构成的互补反相器可以得到较好的转移特性曲线,电压增益可达21[图5(E)].

Fig.5 Schematic illustration of the inkjet-NTP process(A),schematic illustration of an ink droplet filling the recessed nanochannels of a selected area of the mold through capillary-driven flow(B),schematic illustration of a liquid bridge formed by a polar liquid layer between the nanowires and a substrate(C),a photographic image of the integrated electronic devices composed of FET,inverter,and p-n diode arrays made of single-crystal organic nanowires(D),static voltage transfer characteristics and signal gain of a representative inverter composed of TIPS-PEN and C60 FETs(E)[41]

通过转移晶体制得的器件的性能往往因为晶体和基底之间的接触不够紧密而受到影响.相比之下,通过原位生长得到的晶体和基底之间一般具有更好的界面[3,42,43].Li 等[44~46]提出的液滴固定结晶法(DPC)可以在溶液中原位生长取向的高质量单晶阵列.用这些单晶制得的FET具有很高的载流子迁移率.Li等[47]用DPC法在被交联聚合物修饰过的硅片的不同区域(通过紫外臭氧处理被分隔开)分别生长得到了C60和TIPS-PEN 单晶,并分别将其用作互补电路的n型和p型传输层[图6(A)~(C)].在此基础上制得的互补反相器在VDD=60 V时最大电压增益高达155[图6(D)和(E)].

Fig.6 Schematic illustration of the DPC method and inverter fabricating process(A),a composite image from several optical microscopy(OM) images,showing the positioned regions of well-aligned C60 and TIPS-PEN crystals(B),the channels of the inverter(C),the static voltage transfer characteristics(D)and the corresponding gain of a inverter(E)[47]

除了采用电子型和空穴型两种有机单晶,单极性互补电路还可以通过单一种类半导体材料和不同的电极材料构建.使用不同功函数的材料作源漏电极,可以在同一种半导体中实现不同类型载流子的注入和传输,从而选择性获得p型或n型FET.

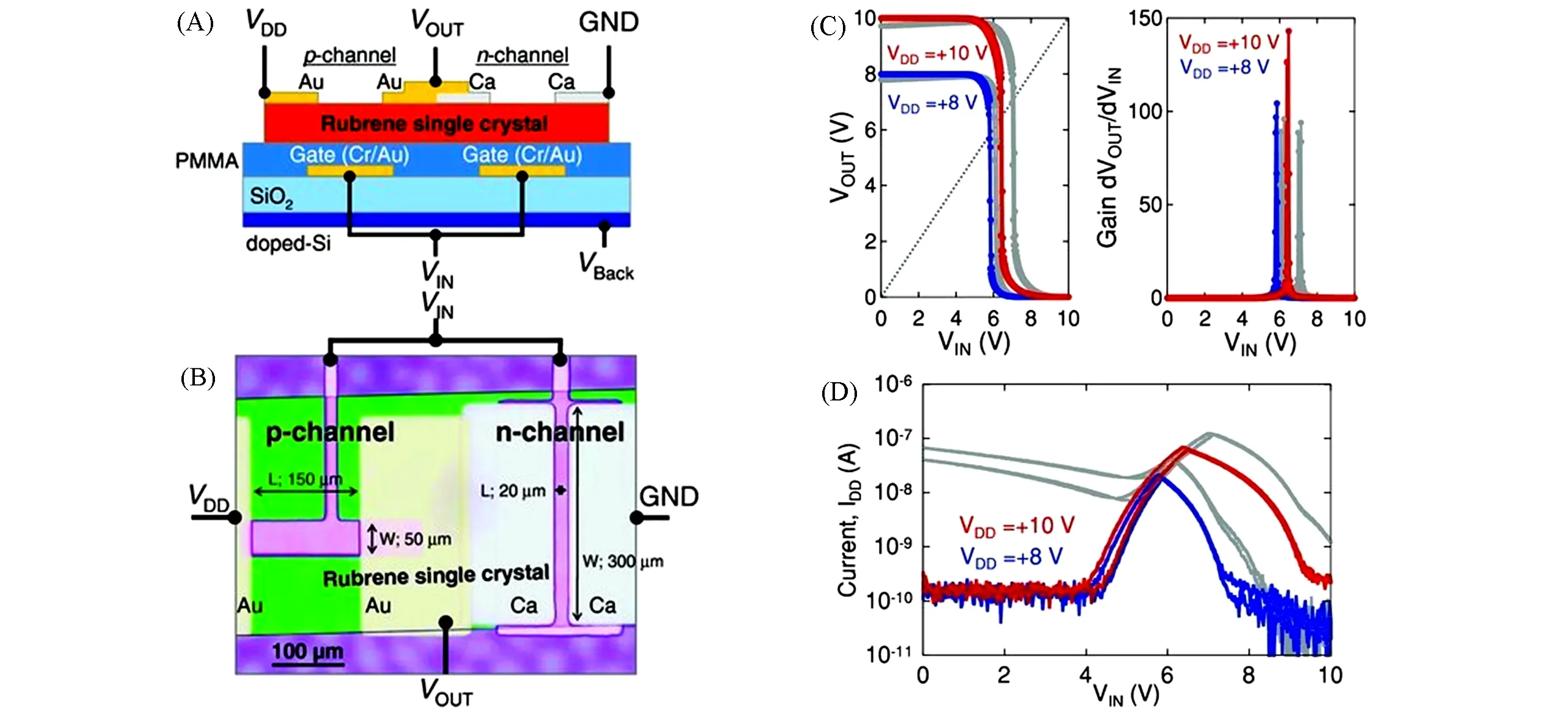

Uemura 等[48]使用金和钙两种电极,在宽带隙材料红荧烯单晶中实现了空穴和电子的注入与传输,从而用一种半导体材料制得了低功耗的互补反相器[图7(A)和(B)].通过施加“背栅电压”(back-gate voltage),可以很好地抑制沟道之间少数载流子的扩散,从而减小沟道的关态电流,使制得的互补器件工作功耗为微瓦级别,静态功耗低至纳瓦级别[图7(C)和(D)].

单极性互补电路可以根据不同类型沟道的传输性能,调节不同FET的宽长比,以实现空穴和电子传输之间的平衡,从而获得更好的电路性能.但对于单晶集成电路来说,同一基底的相邻区域选择性地沉积不同的单晶材料或不同的电极材料不但引入更多的沉积和图案化工序,还不利于简化电路结构和实现高分辨率图案化.在实际生产中,更多的工序不仅会提高生产的时间和物料成本,往往还意味着良率的降低.如果可以用同种FET(半导体和源漏极材料均相同)构成互补电路,将有利于有机单晶集成电路的进一步发展.

Fig.7 Schematic illustration of a monolithic complementary inverter using a rubrene single crystal(A),optical view of the typical device(B),voltage transfer characteristics of the inverter with applying a back gate voltage of +10 V(left),and corresponding DC values of inverter switching(right)(C),penetration current between the VDD and GND terminals at the switching(D)[48]

1.3.2 双极性单晶互补电路 双极性互补电路利用了同一种双极性FET 来实现互补功能.在双极性FET中,通过改变栅极电压的方向,可以实现不同类型载流子的传输[28,49~51].

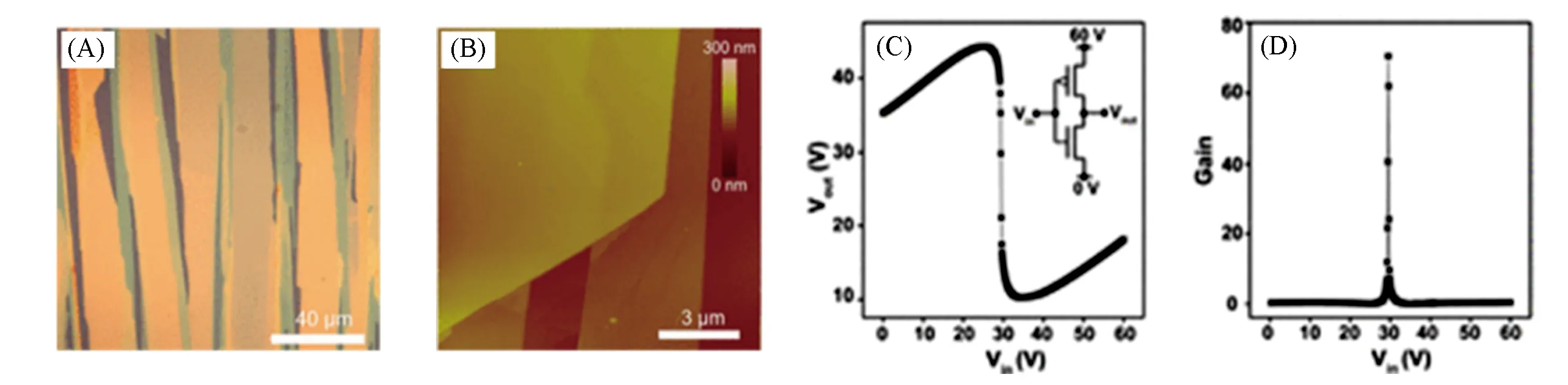

若FET的沟道由电子型和空穴型两种单晶材料共同组成,意味着其可以传输2种载流子.DPC方法不仅可用于单一有机半导体单晶的生长,还可以用不同半导体的混合溶液一步生长得到高质量的双层单晶[图8(A)和(B)],基于这种双层单晶的FET 可以表现出双极性传输的性质[52,53].Li 等[54]用这种方法制得的C60/C8-BTBT双层单晶FET具有较平衡的双极性,电子迁移率可达0.17 cm2·V-1·s-1,空穴迁移率可达0.16 cm2·V-1·s-1;得到的6,13-双(三异丙基甲硅烷基乙炔基)-5,7,12,14-四氮杂并五苯(6,13-bis-(triisopropylsilylethynyl)-5,7,12,14-tetraazapentacene,TIPS-TAP)/6,13-双(三异丙基甲硅烷基乙炔基)-四苯并卟啉(TIPS-BP)双层单晶FET的电子迁移率最高可达1.90 cm2·V-1·s-1,空穴迁移率最高可达1.02 cm2·V-1·s-1.基于后者的互补反相器在VDD=60 V下最大增益可达70[图8(C)和(D)].

Fig.8 An OM image of the bilayer TIPS-TAP and TIPS-BP crystals,showing the bilayer structure with wide ribbons crystals(yellow) and narrow ones(blue)(A),an AFM image of bilayer structure showing the top layer as wide crystals and the bottom layers as narrow crystals(B),the voltage transfer characteristics(C)and corresponding gain of an inverter(D)[54]

若使用本征双极性有机单晶作为载流子传输材料,则同一沟道内仅需沉积一种单晶即可.双极性有机半导体材料往往具有较窄的带隙,空穴和电子均能通过电极较好地注入半导体层[55].迄今,关于这一类型互补电路的研究多是基于有机半导体薄膜做出的[49,50],尚没有关于双极性有机单晶用于双极性互补单晶电路的研究报道.

双极性单晶互补电路因为无需在不同区域选择性沉积不同种类的半导体单晶,且一般仅使用同一种金属作为电极材料,所以制备起来更加方便,更容易提高电路集成时的分辨率.但双极性沟道晶体管往往具有较大的关态电流,这将导致电路较大的静态功耗[48,49,56,57].材料选择性较小是制备这种互补电路时存在的另一个问题.适合用于电路制备的高性能双极性材料较少,而用溶液法生长双层单晶时也对材料有一定的选择性.材料选择的局限性也限制了互补电路中p型和n型FET性能上的平衡,这对电路的最终性能将产生巨大的影响.因此,目前关于双极性沟道型互补单晶电路的研究报道并不多.

2 有机单晶集成电路的尝试

2.1 环形振荡器

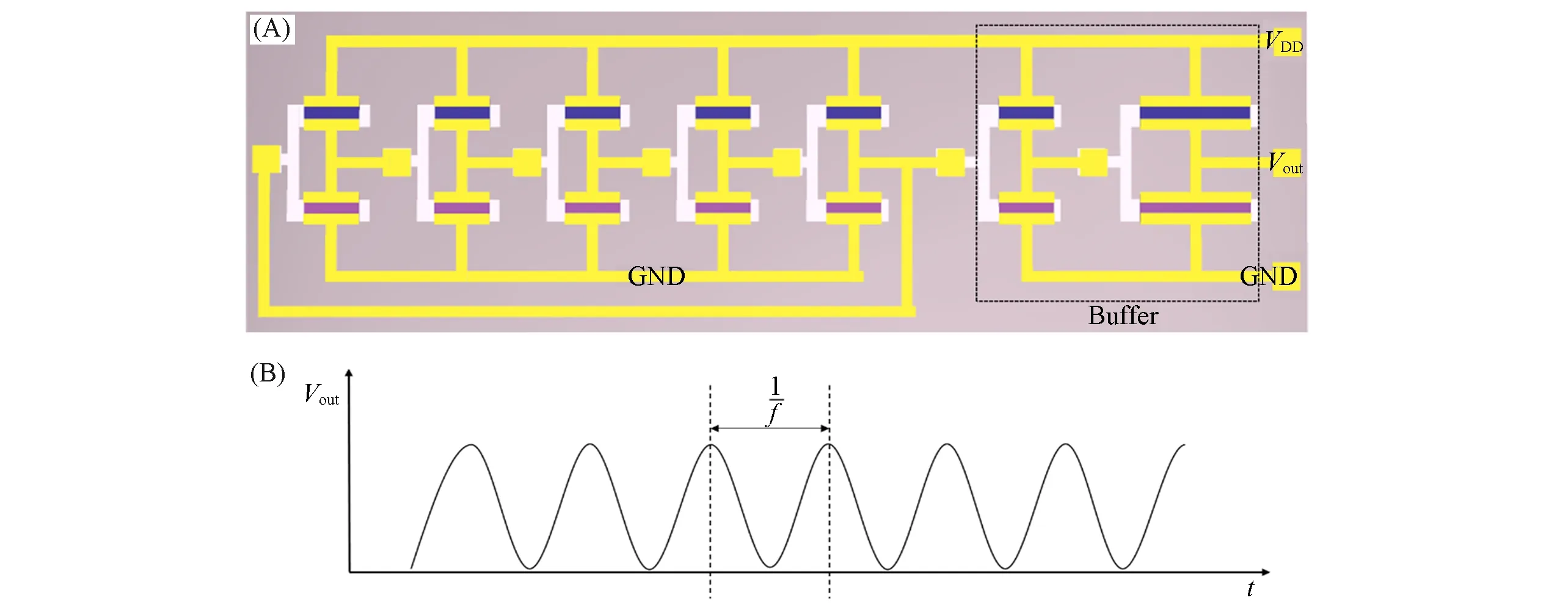

将奇数个反相器的输入端和输出端依次相连形成的环形电路被称为环形振荡器(RO)[19,58~60].环形振荡器可利用门电路的延迟负反馈产生具有一定频率的振荡信号(图9).在有机电路研究中,RO的工作可用于验证反相器驱动后级门电路的能力,也可用于表征器件工作时的传输延迟,根据振荡频率反推出的开关频率,即对应FET能够用于数字电路中的最高速度[60,61].此外,虽然RO结构较简单,但需要用到完整的集成电路制备工艺(如绝缘层、半导体层、金属电极等的沉积,以及通孔、杜绝层间串扰等工艺设计),可用于检验制备工艺的有效性和成熟性,因此成功制备RO意味着可以实现更高阶的逻辑电路[24].

Fig.9 Schematic diagram(A)and output characteristic(B)of 5-stage ring oscillator

振荡频率是RO 最重要的参数,在不考虑寄生电容和接触电阻的情况下,环形振荡器的振荡频率f(Hz)可由下式估算[62]:

式中:L(nm)为振荡器中的反相器沟道的长度;i为振荡器阶数.

由此可见,提高FET的迁移率和电源电压及减小沟道长度均可以提高振荡频率.与基于多晶或无定形有机薄膜的FET相比,有机单晶FET由于具有较高的迁移率,原则上更容易在集成电路上获得高的工作频率.但受寄生电容及接触电阻等因素的影响,有机单晶的优势目前还难以展现出来.在各种影响因素中,寄生电容对RO 振荡频率的影响最大.FET 栅极与源漏电极之间的覆盖面积和沟道间存在的导电路径是产生寄生电容的主要原因.减小电极覆盖面积及消除导电路径有利于减小寄生电容[27].

此外,测量过程也会影响实际测得的振荡频率[1,21~22,24~27,60].为了消除测量仪器的负载电容对器件频率的影响,RO的输出端一般会连接至少一级的缓冲级(Buffer,一般由环形循环外的反相器构成,具有按比例阶梯放大的宽长比).减小测量探针的电容及提高电极的导电性也有利于提高测得的振荡频率.

根据RO的振荡频率,可以用下式计算反相器在特定电压下的传输延迟时间ts,用于表征反相器的开关速度[62].延迟越小,表示反相器具有越大的开关速度:

Cai 等[63]用溶液法制备了9,10-双(苯基乙炔基)蒽(BPEA)纳米线单晶,这种单晶长度可超过100 μm,具有光滑的表面和均匀的形状,且可与基底界面紧密接触,比较适合用于FET 等器件的制备.经过优化后的底栅底接触FET的空穴迁移率可达3.2 cm2·V-1·s-1.在此基础上,他们制备了单极性互补反相器.通过调整负载管和驱动管的沟道宽长比,优化了反相器性能:在电源电压为60 V的情况下,最高电压增益可达92.随后,他们用一根单晶制备了一个5阶的环形振荡器.在电源电压为40 V的情况下,其振荡频率为512 Hz,振幅为38 V.虽然单晶材料展现了优良的迁移率,但是RO的振荡频率未能展现出有机单晶的优势,这是由接触电阻和寄生电容较大、且晶体管之间存在性能波动导致的.由此可见,要获得高性能的有机单晶环形振荡器,不仅对单晶质量有较高要求,更需要完善的电路制备工艺来减小接触电阻、寄生电容以及器件均匀性等问题造成的影响.

2.2 触发器和二进制计数器

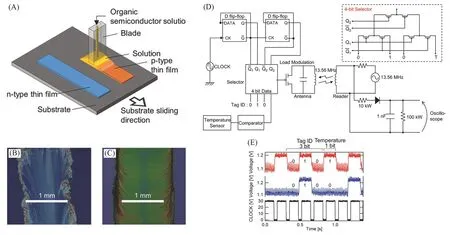

Yamamura 等[64]采用刮涂半导体和PMMA 混合溶液的方法制得了面积较大的连续单晶薄膜.如[图10(A)~(C)]所示,采用这种方法可以在同一基底上沉积不同类型的薄膜,用于制备互补器件与电路.他们用单晶薄膜依次制备了基于或非门逻辑的D-触发器和由两个D-触发器串联得到的二进制计数器,这些器件均可正常实现逻辑运算.在此基础上,作者将二进制计数器与一个4位数据选择器、一个温度传感器、一个比较器、一个负载调制晶体管及一个天线相连,制备了一个可用于检测温度且具有特定身份信息的RFID标签[图10(D)].其中,二进制计数器和数据选择器的组合可以将4位的并行输入信号转化为串行输出信号.输入的前三位“010”由输入端接地或接高电平产生,作为该标签的身份信息;输入信号的第四位由温度传感器产生:当检测温度高于50 ℃时,输入信号为1;当检测温度低于50 ℃时,输入信号为0[图10(E)].最后,该标签将产生的串行信号经过调制后无线发送给信号接收器.信号接收器接收信号,可获得关于该标签的身份和温度信息.

Fig.10 A diagram showing the present crystal growth method(A),photographic images of organic single crystalline films of p-type(B) and n-type(C) semiconductors,a schematic of the RFID prototype(left)and a circuit diagram of the 4-bit selector(right)(D)and the signal received at the reader oscilloscope at two different temperatures(E)

该工作将有机单晶电路的研究向实际应用推进了一步,也展现了有机单晶作为集成电路材料的优势.但是严格来讲,用这种混合溶液刮涂法得到的并非单晶,而是结晶度较高、晶粒尺寸较大的多晶薄膜.尽管如此,作者也为研究有机单晶电路提供了丰富而宝贵的经验:如根据p型和n型材料性能的相对高低选择合适的电路逻辑、根据电极向不同半导体材料注入载流子能力的不同适当选择电子或空穴注入层以帮助载流子的注入等.相信随着有机单晶制备方法的发展以及有机电路制备工艺的完善,越来越多的具有实际应用价值的高性能有机单晶集成电路将被制备出来.

3 挑战与展望

3.1 挑 战

虽然有机单晶电路的研究意义重大,但要实现其大面积集成应用还有很长的路要走,从材料分子到器件,许多制备和生产过程中都面临巨大的挑战.

从构成材料的分子层面看,虽然有机半导体分子种类已经很丰富,但兼顾稳定性、加工性能和载流子传输性能的材料较少.特别是对于n型材料,如何在保证高迁移率的条件下提高分子的稳定性是一个重要的问题.除了半导体材料以外,绝缘层材料和电极材料也是有机电路的关键组成部分.对于绝缘层而言,目前兼具柔性、耐击穿、易成膜、绝缘性能好、介电常数高、稳定性好等特性的综合性能优异的绝缘材料仍有待开发[65~68].

从聚集态形貌控制上看,目前仍然缺少连续制备均匀的大面积有机单晶薄膜或者取向单晶阵列的技术.一方面,有机半导体分子间较弱的分子间作用力使得晶体的成核、生长极易受到环境条件的干扰,难以得到大面积、均一性好的薄膜状单晶;另一方面,有机半导体分子结构的多样性使得各种分子在结晶性和合适的结晶条件方面存在着巨大的差异,难以用单一、简单的方式去涵盖.一些结构不对称的小分子和聚合物甚至无法制得单晶.鉴于大面积单一单晶难以获取,取向单晶阵列是制备单晶集成电路的另一个选择.载流子的传输过程发生在特定的沟道范围内,因而只需在电路的特定位置覆盖有机半导体层即可实现完整的电路逻辑功能.通过电路设计和单晶阵列的沉积,可以实现大面积的单晶电路的集成.但如何控制晶体在特定位置的成核与生长,以制得厚度均一、取向一致的高质量单晶阵列仍是一个难题.大面积单晶或取向单晶在制备上的挑战是限制有机单晶集成电路发展的一个主要因素.

从器件制备工艺上看,与有机半导体、聚合物绝缘层等兼容的短沟道、高集成度制备工艺有待开发.传统的光刻技术虽然能制得高分辨率的电路,但由于需要经历前烘、显影、去胶等涉及加热、溶剂洗脱的过程,容易破坏绝缘层或半导体层,难以与有机电路的集成很好地兼容.另外,有机单晶集成电路制备过程中的各种工艺,如晶体生长、电极沉积、通孔制备等还未标准化,难以用统一的标准进行评价和生产.开发出适用于有机电路的高分辨率集成技术,统一电路制备工艺标准,是实现有机电路实用化生产的另一个重要前提.

3.2 展 望

随着科技的发展,柔性显示器、物联网技术、智能穿戴设备、生物化学传感器等已经进入了我们的生活,而有机集成电路具有的柔性、轻便、可大面积溶液加工及生产成本低等优点为这些技术的发展提供了物质保障.在实验室中,许多功能复杂、集成度高的有机集成电路系统,如RFID标签、盲文识别器[69]及无线电力传输系统[70]等早已被制造出来.有机电路的性能也有了长足的进步,如目前基于有机FET 的反相器增益可达103水平[71];RO 中的单级传输延迟时间可达几十纳秒的级别[72].更进一步地,基于有机单晶半导体的逻辑电路,以基础的反相器为例,有望进一步将晶体管的迁移率提高至大于10 cm2·V-1·s-1,增益接近并达到104水平,噪声容限达到40%VDD,单极延迟接近10 ns(对应工作频率为100 MHz).当有机逻辑电路的性能达到上述指标时,有机集成电路将会被广泛用于柔性显示、射频通讯、生物传感、物联网等应用场景,有机集成电路大规模应用于日常生活、生产的时代即将来临.