一种3.5 GHz频段双通道射频前端设计*

吴学富,程 方,刘浩东

(重庆邮电大学 通信与信息工程学院,重庆 400065)

0 引 言

近年来,第五代移动通信(5G)已经成为我国“新基建”的重点工程,也是推动我国向数字化、智能化经济转型的核心动力,国内的5G网络建设和发展具有巨大的潜能。工信部发布相关文件,规划3 300~3 600 MHz和4 800~5 000 MHz为我国5G通信系统的工作频段。与4.9 GHz频段相比,3.5 GHz频段信号波长更长,穿透能力更强,覆盖更广,单位面积内基站建设所需成本也更低[1],我国将主要部署3.5 GHz频段。5G网络建设的快速推进离不开相关测试设备的支持。韩国和美国作为最早开通了5G商用的国家,在实测中均出现了不同程度的问题[2]。为保障我国5G商用的有序推进,需要在商用之前使用5G终端模拟器做好全方位的测试和有效的评估。

长期以来,中高端通信测试仪器仪表的关键技术仍由是德科技(Keysight)、思博伦(Spirent)、罗德与施瓦茨公司(R&S)等所主导。射频前端作为5G终端模拟设备的核心之一,研发出具有自主产权的新型射频前端对于填补我国中高端通信测试仪器的空白具有重要的意义。5G新技术的使用对射频前端设计提出了更加严格的要求,例如更多的通道、更小的尺寸、更低的功耗以及更好的通信性能[3-4]。这就需要不断跟进最新标准,设计出满足5G终端模拟器的收发射频前端。设计人员通过对射频前端的多通道结构设计,可以将其很方便地组成大规模阵列,以适用大规模多输入多输出(Multiple-Input Multiple-Output,MIMO)系统[5-6],但这也大大地增加了器件数量和收发机的尺寸。常用的射频前端结构有超外差和零中频两种,针对单频段收发的射频前端可以采用零中频结构,相比于超外差结构省去了设计中的变频部分,从而降低了电路的复杂度和前端的尺寸[7]。互补金属氧化物半导体(Complementary Metal-Oxide-Semiconductor,CMOS)和GaAs工艺器件的快速发展,大大提高了射频前端重要器件的性能,同时也让其尺寸和功耗得到了有效的降低[8-9]。而高性能、集成式收发器芯片的应用,则使射频前端更加地趋向于高集成化、小型化,设计人员在频段和结构设计等方面也有了更多的选择[10]。ADI公司生产的高集成收发器ADRV9009最大支持200 MHz带宽,在支持两收两发的基础上各自增加了一个观测器,芯片大小仅为12 mm×12 mm。该芯片包含自动增益和衰减控制功能,从而在动态范围上具有更大的灵活性,其良好的性能更好地支持终端模拟器的通信。

鉴于此,本文综合考虑射频前端的工作频段、收发性能、尺寸和功耗等因素,结合收发器ADRV9009设计并实现了一种适用于5G终端模拟器的3.5 GHz频段双通道射频前端,在满足收发性能的前提下减少了器件数量,降低了设计复杂度。实测结果表明,该射频前端性能良好,满足设计要求,可用于5G终端模拟器的设计。

1 系统方案设计

1.1 射频前端整体方案设计

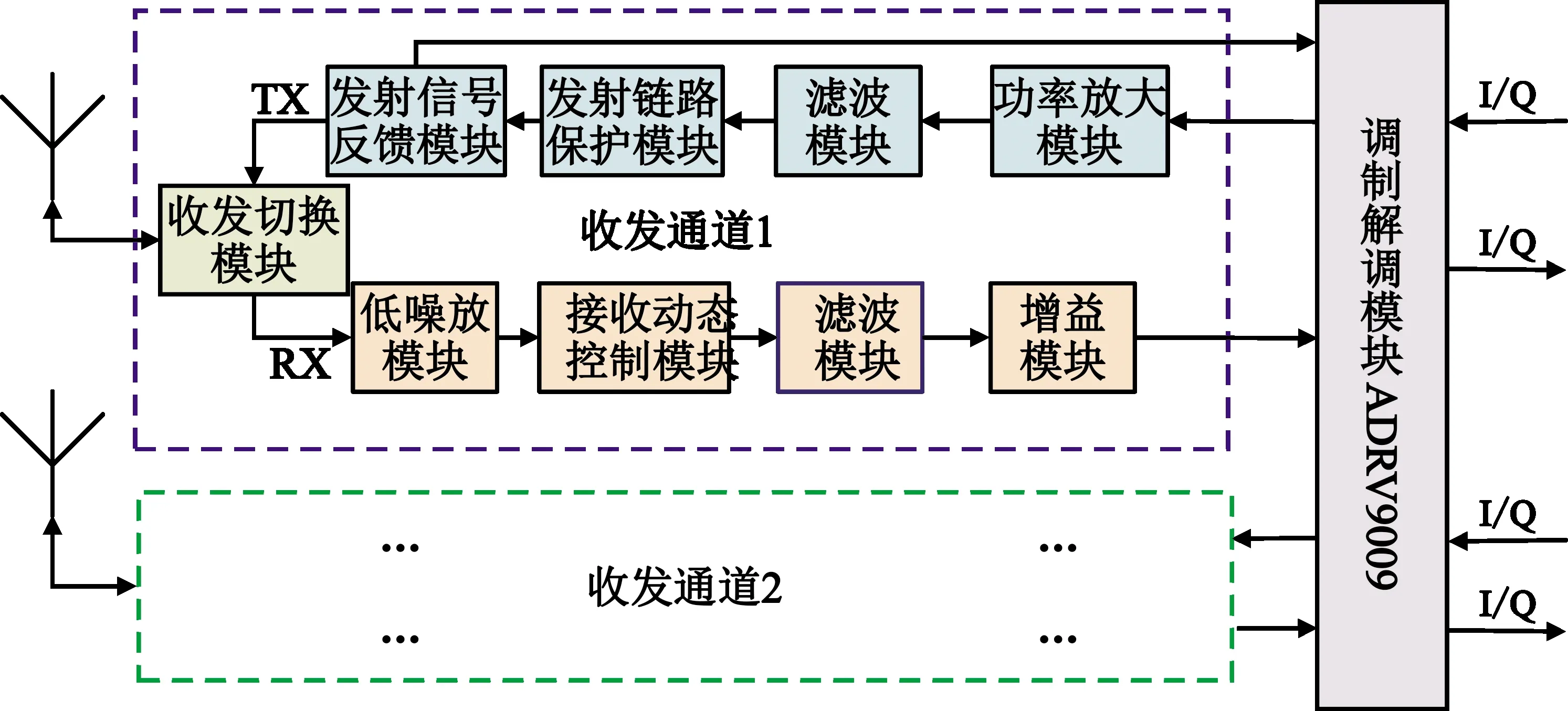

射频前端结构常用设计方案有超外差结构和零中频结构。由于本设计中射频前端为3.5 GHz单频段信号的收发,相比于超外差结构,零中频结构设计更为简便,省去了变频模块,无需镜像干扰抑制滤波器,减少了系统成本和尺寸,有利于单片集成,更适合本方案的设计。本方案结合了ADRV9009收发器设计了具有双通道的射频前端,两通道设计相同,每个通道包括了发射链路和接收链路两部分。

从天线端接收的信号经过收发切换模块后进入接收链路,依次经过低噪放、滤波和增益等模块进行信号功率放大,并对信号噪声和带外杂波进行抑制;接收动态控制模块将根据接收信号功率的大小进行相应的衰减和放大,以保证接收信号处于最佳的接收状态;最后信号进入调制解调模块ADRV9009进行I/Q解调输出给基带。处于发射模式时,由调制解调模块ADRV9009产生的信号经过功率放大模块和滤波模块进行功率放大后,最终从天线端口输出。其中部分发射信号将通过反馈模块输出给ADRV9009,以保证发射信号的动态可控。此外,发射链路还额外设计了保护模块,以增加发射链路的安全性。射频前端的整体设计结构如图1所示。

图1 收发机设计结构框图

1.2 射频前端链路设计

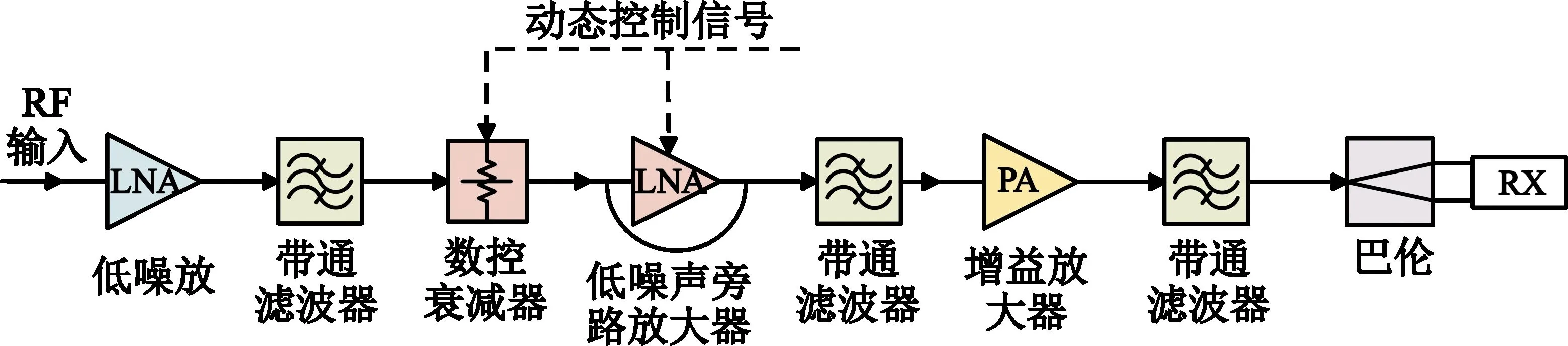

信号首先经过低噪声放大器进行功率放大,同时,低噪声放大器可使前级电路噪声系数控制在一个较小的范围之内。由于ADRV9009本身的动态范围不足以满足5G终端模拟器对接收动态范围较大的需求,故接收动态模块设计了低噪声旁路放大器和数字衰减器进行搭配,并根据接收信号的功率大小进行链路的增益调节,保证后端调制解调模块处于最佳接收性能。信号最后经过第三级增益放大器进行放大,保证了接收机最大接收灵敏度时对小信号的良好接收。最终信号经过巴伦转换进入调制解调模块ADRV9009后输出给基带。接收链路设计如图2所示。

图2 接收链路设计图

射频前端处于发射模式时,初始的小信号通过功率放大模块合理的增益分配进行二级放大以达到射频前端最大发射信号的功率指标。分别在驱动放大器前级和末级功率放大器后级搭配了射频开关和隔离器两个保护模块,该射频开关在保护驱动放大器的同时也确保了收发链路间的切换同步,后级的隔离器则是为了防止发射信号回波损毁功率放大器。发射信号反馈模块由耦合器和衰减器组合而成,部分发射信号耦合给ADRV9009的观测器,以保证后端对发射信号功率的可控,而衰减器则可保护ADRV9009的观测器不被损毁。发射链路设计如图3所示。

图3 发射链路设计图

1.3 系统技术指标

接收机的主要技术指标:工作频段为3 300~3 600 MHz;接收灵敏度为-85 dBm;接收动态范围大于60 dB;噪声系数小于3 dB;带内增益平坦度小于1 dB;接收端信号功率为0 dBm时杂散信号电平小于40 dBm。

发射机的主要技术指标:最大输出功率为20 dBm;带内增益平坦度小于1 dB;256QAM调试方式下误差向量幅度(Error Vector Magnitude,EVM)小于3%。

2 电路关键模块设计

2.1 低噪放模块设计

射频前端的接收对信号的噪声指标尤为敏感,若系统由多个器件级联而成,可通过各个器件噪声系数Fi和各个器件功率增益Gi来计算系统总的噪声系数:

(1)

要保证接收机对高接收灵敏度的指标要求,就必须针对小信号进行大增益放大,但这样就不可避免地使小信号的信噪比恶化。因此,在设计接收链路时,第一级放大器要选择噪声系数较小且增益足够高的低噪声功率放大器。设计采用QORVO公司的QPL9503集成式、低噪声放大芯片,该放大器在提供20 dB以上有效增益的同时可将噪声系数控制在1 dB以内,其高达19 dBm的1 dB压缩点也保证了接收信号的高线性度。

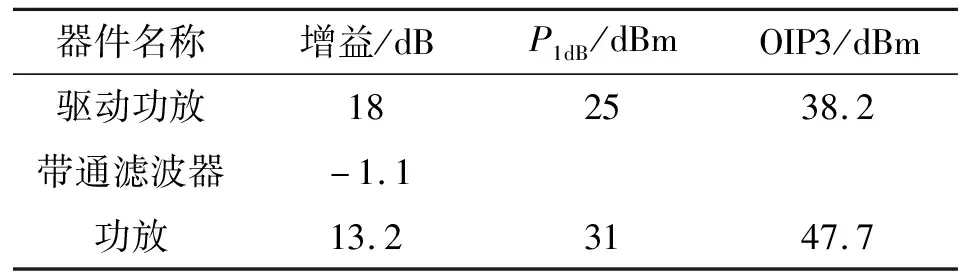

为达到设计要求,对前端电路的增益和噪声系数进行预算分析,数据均来自各器件数据手册。表1为前级电路器件工作在3.5 GHz时的主要设计指标,由式(1)计算结果得前级电路噪声系数为1.72 dB,达到设计要求。

表1 前级电路器件主要指标

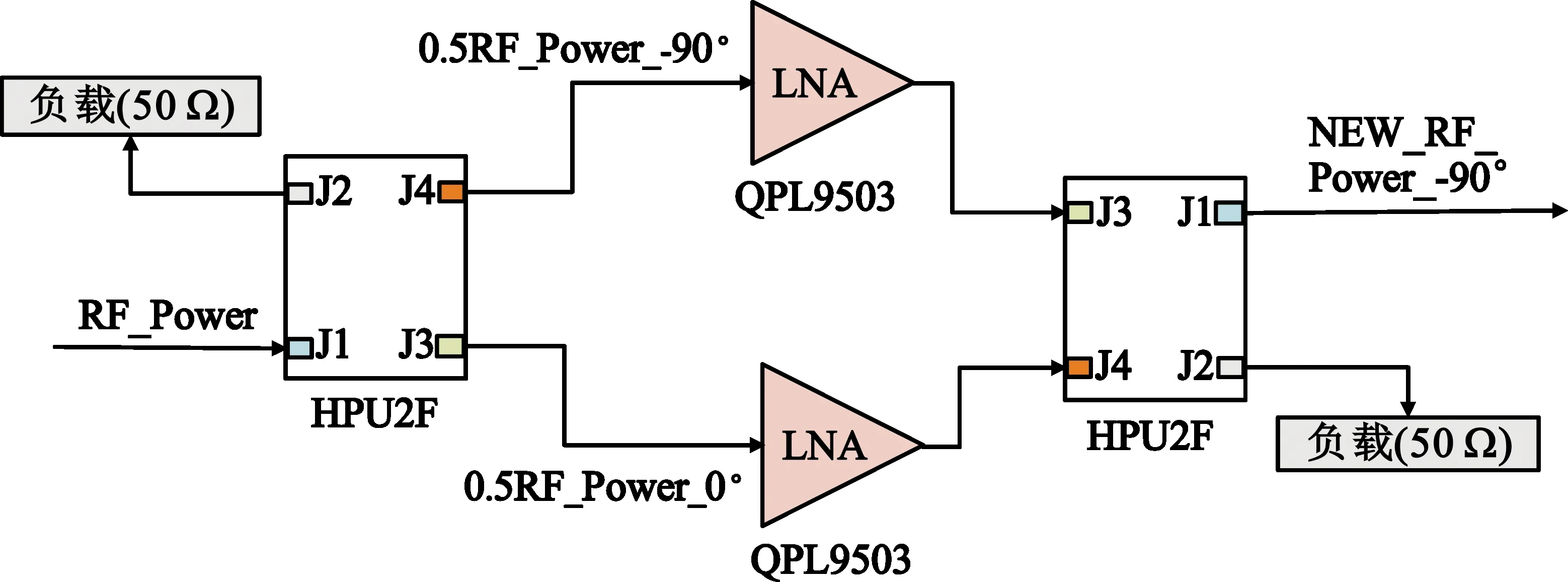

由于前级低噪声放大电路对接收链路极为重要,因此,为保障前级电路工作的稳定性,采用3 dB平衡电桥的设计方式搭建前级低噪声放大电路。设计选用EMC Technology公司的90°混合耦合器HPU2F作为电桥,J2端口接50 Ohm负载,端口J1与J4的相移特性为-90°,与J3无相位差。射频信号经过HPU2F被分为两路,每一路信号功率为原来的一半,经低噪放QPL9503放大,最终两路信号合路为一路信号送至后级电路,此信号与初始信号相位相差90°。当电路中的某一路低噪声放大器损坏,虽然射频信号功率会损失一半,即电路的增益损失3 dB,但电路的另一低噪放仍能正常工作。此设计大大增加了前级电路的稳定性,同时还可使电路匹配性更好。前级低噪声放大电路如图4所示。

图4 前级低噪声放大电路

2.2 接收动态模块设计

ADRV9009自身动态范围仅有30 dB,无法达到射频前端接收动态范围大于60 dB的设计指标,因此采用Mini-Circuits公司的低噪声旁路放大器TSS-53LNB+与ADI公司的HMC1122数字步进衰减器搭配。TSS-53LNB+包含有内部控制开关,接收前端可根据接收信号功率大小来控制放大器是否旁通,此时器件的增益表现为1.5 dB的插损值。当接收小信号时,器件为直通模式,此时增益值约为16.5 dB,而噪声系数为1.4 dB。HMC1122数字步进衰减器最大衰减值为31.5 dB,其最小控制步进为0.5 dB,很好地保证了对接收信号增益的控制精度。接收增益控制范围为-33~16.5 dB,计算上后级ADRV9009内部包含的30 dB可调范围,接收机总的接收动态范围达80 dB,满足设计指标要求。

2.3 功率放大模块设计

为满足射频前端最大发射功率的指标要求,功率放大模块设计了两级放大器。前级驱动放大器使用QORVO公司的QPA9842,对小信号的增益为18.7 dB。该器件采用内部平衡放大设计,可提供非常好的输入输出驻波比。末级的功率放大器最为关键,本设计采用Avago公司的高线性放大器ALM-31322,通过使用0.25 μm的GaAs工艺制成,信号增益为13.2 dB。该器件具有良好的线性性能,达47.7 dBm的输出三阶截点(Out Third-order Intercept Point,OIP3)和31 dBm的1 dB压缩点,在信号峰均值比(Peak-to-Average Power Ratio,PAPR)为12 dB时,也可保证发射信号良好的线性度。

发射机对信号的质量有严格的要求,功率放大器需工作在线性区内,否则其非线性会造成信号失真,使发射信号指标恶化。OIP3和1 dB压缩点都是衡量器件或系统线性度的重要指标。在设计发射链路时,需要对两者进行严格把控。链路的OIP3级联公式表达式为

(2)

式中:OPI31、G1为最后一级器件的参数。由式(2)可以看出,接收链路中,发射链路级联输出三阶截点的主要影响因素为末级功率放大器的参数。为保证链路各器件均能保持良好的线性度,对功率放大模块的主要参数进行计算分析。表2为功率放大电路器件工作在3.5 GHz时的主要设计指标,计算可得功率放大模块总增益为30.1 dB,链路级联OIP3为46.16 dBm,输出1 dB压缩点为30.24 dBm,达到了设计要求。

表2 功率放大电路器件主要指标

3 收发链路仿真

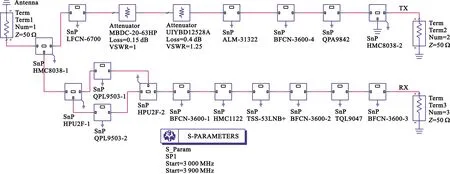

为了更好地验证方案设计的可行性,通过仿真软件ADS2017对射频前端的收发链路进行仿真。按照系统设计方案添加器件的S参数模型,模型数据来自器件厂商和测试数据。系统ADS仿真原理如图5所示。

图5 系统ADS仿真原理图

仿真结果如图6所示,其中,图6(a)为接收链路增益和噪声系数仿真结果。当接收信号为-85 dBm时,此时链路增益为最大,其值约44.5 dB,带内增益平坦小于1 dB,噪声系数约为1.65 dB。图6(b)为发射链路增益仿真结果,链路增益约为26 dB,带内增益平坦小于1 dB,满足预算指标和设计要求。

(a)接收链路增益与噪声系数

4 系统测试

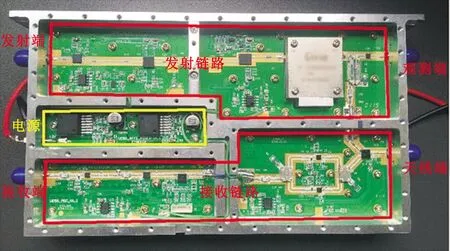

在实现过程中,针对收发机前端进行了腔体设计及分腔处理,以达到较好的隔离度,防止收发通道串扰及电源对链路信号的干扰。最终完成了射频前端整体实物设计,整机尺寸为170 mm×90 mm×25 mm,射频前端实物内部结构如图7所示。通过相应仪器进行测试,测试环境如图8所示。

图7 射频前端实物内部结构图

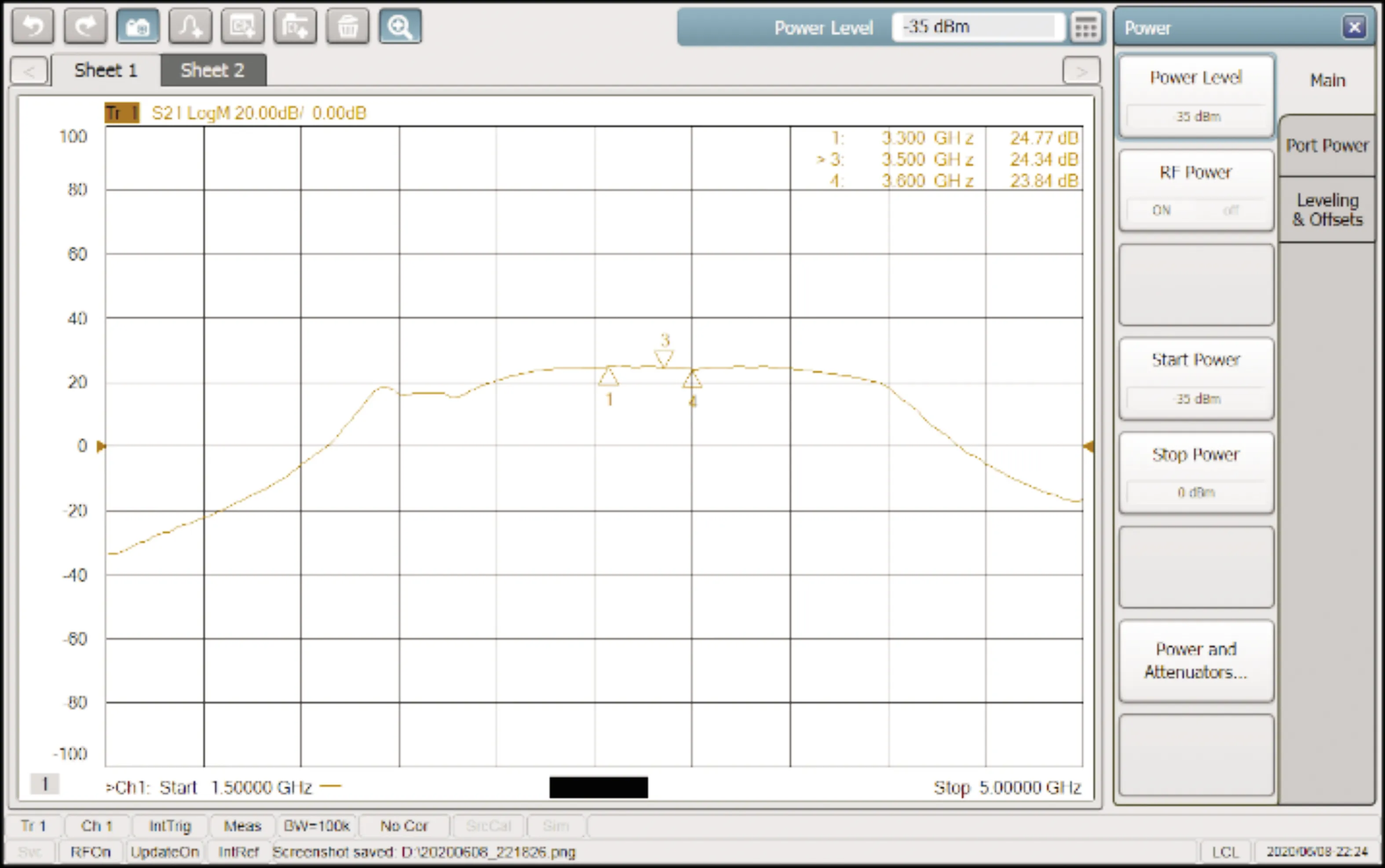

4.1 发射链路测试

根据指标要求分别对发射链路的增益、误差矢量幅度及杂散电平抑制进行测试,结果如图9所示。

(a)发射链路增益

由图9(a)可知,发射链路增益约为24.34 dB,与仿真数据约有2 dB误差,考虑到测试时接线所用同轴电缆的线损,测试结果与预期相符,通道内增益平坦度小于1 dB。图9(b)所示发射机在256QAM调制下,EVM为1.43%,符合指标要求。为保护仪器,发射机输出端接20 dB衰减器,测试时,需将腔体盒盖扣上,否则受外界干扰影响,信号的杂散测量结果会较差,从而影响测量数据的真实性。图9(c)所示的测试结果表明,发射信号功率为0 dBm时,即发射机达最大发射功率20 dBm,发射机杂散信号电平小于-40 dBm,抑制效果较好。由图9的测试结果可知,发射链路达到设计指标。

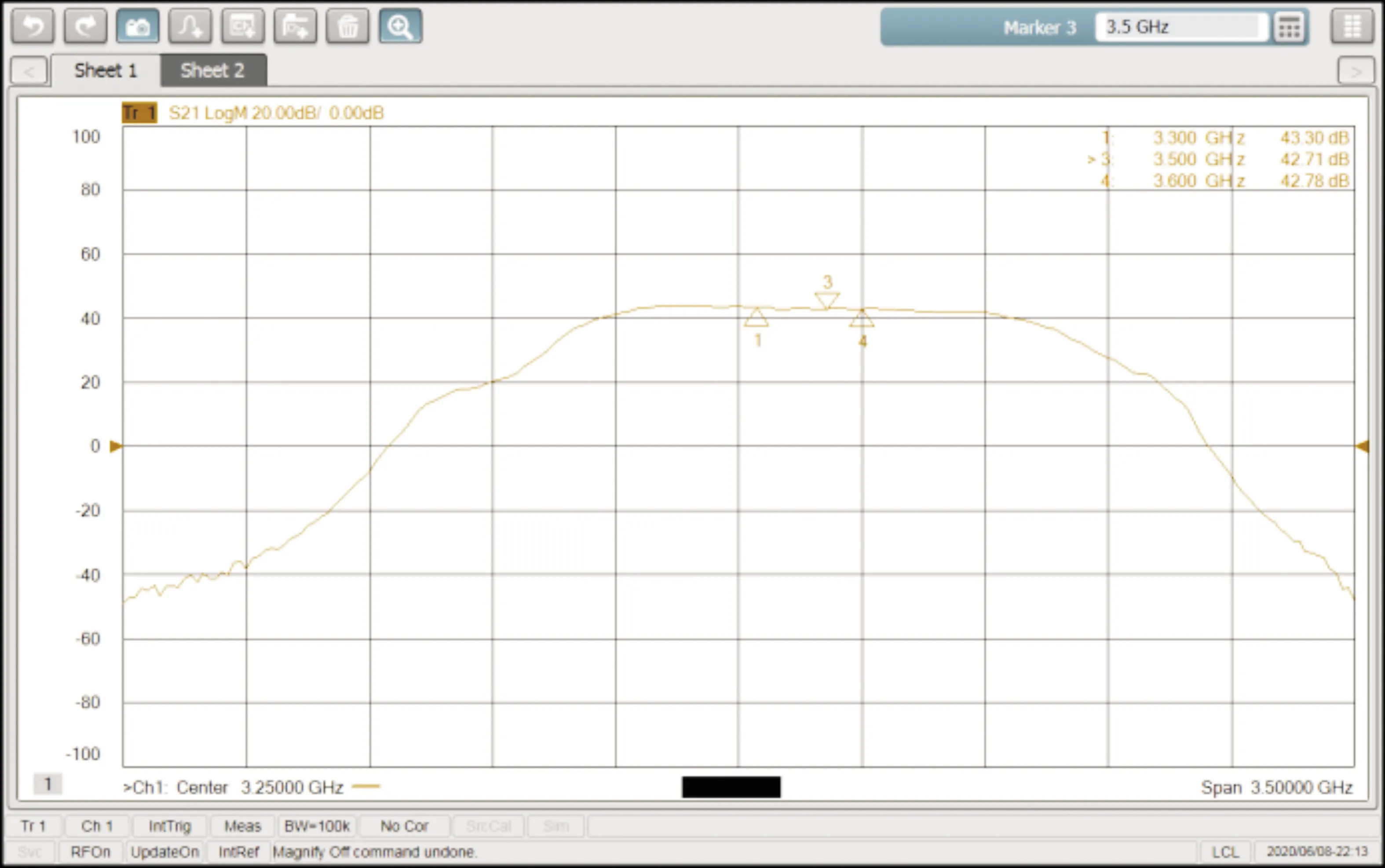

4.2 接收链路测试

接收链路对信号的噪声要求较高,主要对链路增益、噪声系数及杂散电平进行测试,图10为测试结果。如图10(a)所示,接收链路3.5 GHz处实际测试增益约为42.71 dB,与仿真结果约有1.79 dB误差,考虑到器件连接和测试线损的影响,测试结果符合预期要求,带内增益平坦度小于1 dB。如图10(b)所示,测量杂散时将腔体盒密封,接收端信号为0 dBm时,杂散电平小于-50 dBm,符合设计要求。如图10(c)所示,仪器输入端接入10 dB衰减,以保护仪器,手动控制动态模块将接收链路增益调至最大,测得链路真实噪声系数小于2.6 dB,比噪声仿真结果大1 dB左右,但仍在设计要求的3 dB以内。可通过降低低噪放模块前级的射频开关等器件的插损,从而进一步减小噪声系数。由图10的测试结果可知,接收链路测试达到设计要求。

(a)接收链路增益

5 结 论

针对5G终端模拟器中的射频前端,本文设计了应用于3.5 GHz频段的双通道射频收发前端。设计方案结合ADRV9009芯片,分别针对接收链路的噪声系数和动态范围以及发射链路的发射功率和线性度进行了设计和分析,并通过ADS对收发链路的主要参数进行了仿真。实测结果显示,收发链路的各参数性能均达到了设计要求,验证了方案的正确性和合理性。该射频前端对5G相关测试仪表的研发具有重要意义。