芯片物理指纹的可用性评估*

钟 杰,雷颜铭,郑 力,潘亚雄,何 琛

(中物院成都科学技术发展中心,成都 610200)

0 引 言

随着通信技术的飞速发展,物联网技术已广泛应用于管理、生产、生活的各个领域。物联网通信终端通常无人看守,因此也面临着独特的网络安全问题。如何实现对物联网通信终端的可信认证是实现物联网安全的重点,加密技术的应用是实现物理网可信体系的有效手段。传统的可信体系是一种基于证书认证、接入控制和密码服务的安全防护体系,具有高安全系数,但由于对安全策略及安全强度的需要通常会对通信带宽、计算能力等整体资源开销提出较严苛的要求。除此之外,由于物联网通信终端通常无人值守使得终端具有丢失的可能性,一旦发生密钥泄露将对整个通信网络带来安全隐患。芯片是广泛应用于各类物联网通信终端的重要元器件,受生产工艺中不可控制的随机因素影响,任意两个芯片都是相互独立的,具有不可复制的差异性和随机性,对这种特性进行提取可形成芯片独有的物理指纹,也称物理不可克隆函数(Physical Unclonable Function,PUF)。利用芯片物理指纹结合现有的加密技术构建新型可信认证体系,具有不需要存储密码资源、不要求复杂运算能力、协议简单、通信量小、安全性高的优势,同时由于无需本地存储密码资源,降低了设备丢失后的失密风险[1-4]。

1 芯片物理指纹的提取、认证要素

1.1 芯片物理指纹的提取

目前,国内学者已开展关于芯片物理指纹的研究工作,研究类型主要包括存储类物理指纹和延时类物理指纹。典型的存储类物理指纹电路结构有静态随机存取存储器(Static Random Access Memory,SRAM)PUF结构和触发器PUF结构。这类PUF结构通过采集芯片上电时的不确定性特征生成芯片独有的物理指纹,其物理指纹比特和PUF电路资源一一对应,属于弱PUF类别,通常用于对物理指纹容量要求不大的场景。典型的延时类物理指纹电路结构有仲裁器PUF结构、蝴蝶PUF结构、环形振荡器(Ring Oscillator,RO)PUF结构。这类PUF结构通常具有强PUF或中强PUF特性,在消耗一定芯片资源的情况下通过组合逻辑可以获得大量的芯片物理指纹。

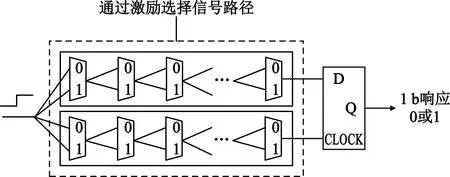

从强PUF或中强PUF电路结构提取的芯片物理指纹通常以激励响应对的形式进行管理和使用,物理指纹中的激励通过服务器端向通信终端发送,用于对指纹提取电路分布、电路中可配置逻辑进行选择,通常1个基本单元的指纹电路能够生成1 b的响应。如图1和图2所示,在RO电路和仲裁器电路中,分别通过激励信号选择RO比较组与信号路径,生成1 b响应。激励的位数和取决于PUF基本电路结构的资源数以及激励位的组合方式,通过重复性构建基本单元可以对响应位数进行调节。

图2 仲裁器电路基本单元结构示意图

1.2 芯片物理指纹的认证要素

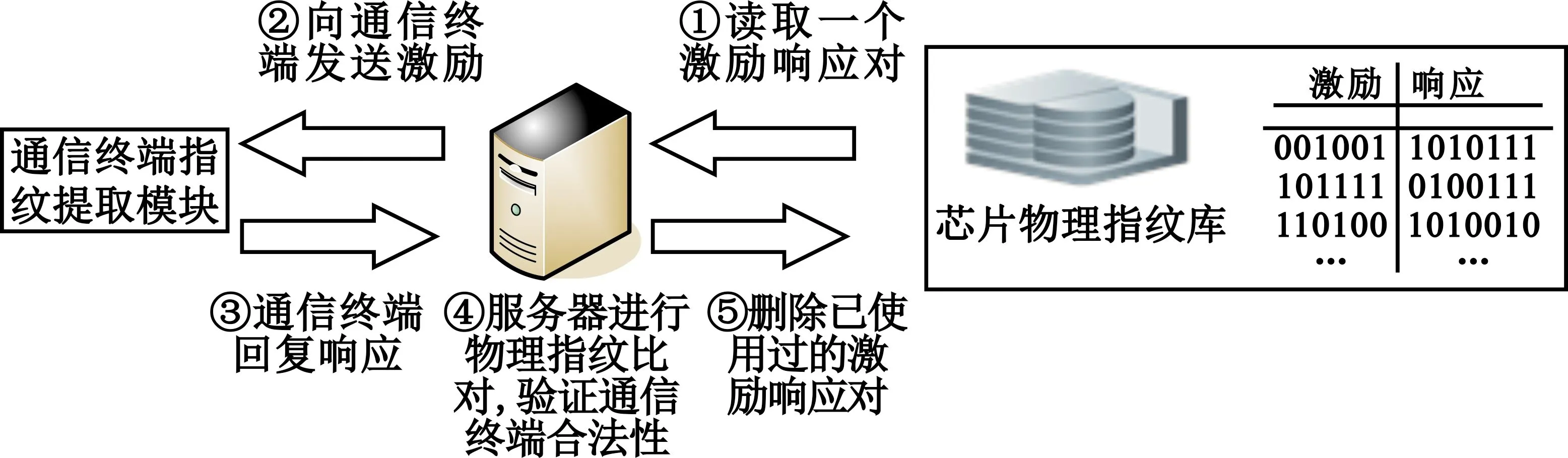

芯片物理指纹的应用包括两个步骤:第一步,采集芯片物理指纹并录入指纹库;第二步,认证管理服务器将通信终端返回的响应比特与芯片物理指纹库记录比特进行比对,当两者一致时,则通信终端通过可信认证。强PUF或中强PUF类电路结构能够实现大量的物理指纹提取,认证过程中随机选择芯片物理指纹库中的指纹用于认证,使用过的物理指纹将从芯片物理指纹库中删除不再使用,如图3所示。

图3 认证过程示意图

随机性是影响芯片物理指纹可用性的关键参数,芯片物理指纹通过提取芯片制备过程中随机性误差用于实现硬件层面的认证。例如在RO电路结构PUF中提取的是不同电路单元的延时比对信息,这种信息应是对其随机性工艺误差的表征。但是在芯片制备过程中,不可避免会出现氧化、光刻、刻蚀、掺杂等不均匀的情况,这种不均匀情况将导致不同区域电路单元的延时出现差别,而这种差别通常是具有规律性的,尤其在同批次的芯片中较为明显,这种规律性的误差是系统误差。相比于系统误差,工艺误差引起的延时量一般较小,所以系统误差将会弱化芯片物理指纹的随机性,使得芯片物理指纹的响应将可被预测。在芯片物理指纹电路设计中,可通过增加补偿电路设计对批次芯片的系统误差进行抵消或弱化。

稳定性也是芯片物理指纹的关键参数。在芯片物理指纹提取过程中,受到温度、振动、电压等环境因素的影响,电路单元的延时会出现波动,可能使得芯片物理指纹的响应出现不稳定的情况,尤其在两个比对电路单元延时差不大的情况下这种波动特别明显。因此在芯片物理指纹读取阶段需要对指纹的稳定性进行测试,选择符合稳定性要求的指纹录入芯片物理指纹库。稳定性将直接影响到可用于认证的芯片物理指纹数量以及匹配通信终端的认证成功率。由于芯片物理指纹的实现机理除涉及基础的理论性科学,也具有实验性科学特性,芯片物理指纹的延时特性具备随机性和不可控特征,要解决物理指纹比对一致性要求和芯片资源限制引起的对立问题,认证协议的设计与执行就成为流程中的关键。

2 芯片物理指纹的可用性评估

2.1 可用性评估方案设计

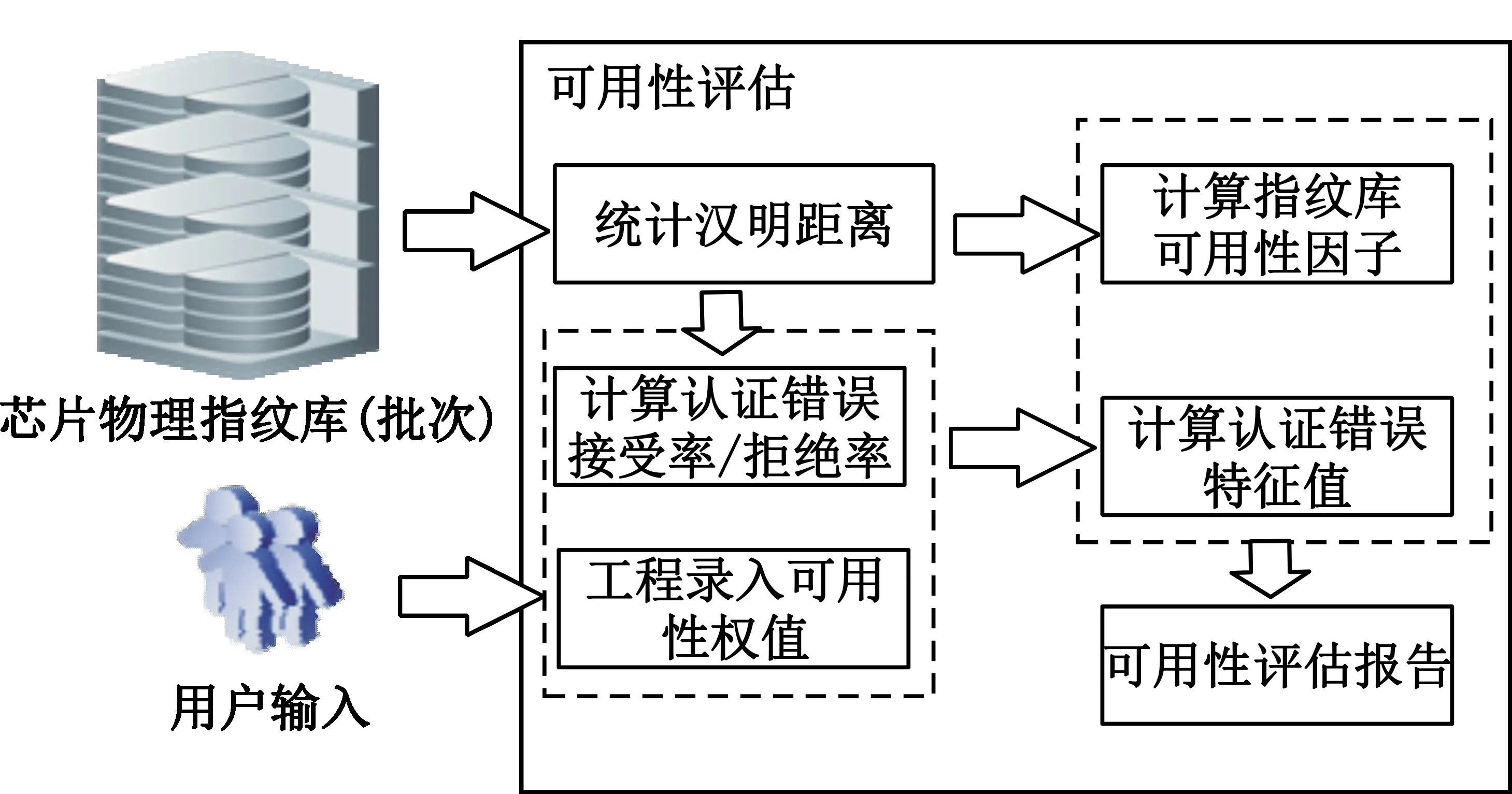

随机性和稳定性直接影响了对通信终端的认证准确率,也是评估一个芯片物理指纹库工程应用效能的基础特性参数。目前关于芯片物理指纹的研究主要集中在芯片物理指纹的电路设计和基于芯片物理指纹的身份验证方法上,关于芯片物理指纹认证应用性能评估的研究较少。本文将以强PUF类型的芯片物理指纹为例,通过引入汉明距离、指纹库可用性因子、认证错误接受率、认证错误拒绝率、可用性权值、认证错误特征值等概念,对芯片物理指纹的可用性进行量化表征与评估[5-7]。图4为芯片物理指纹的可用性评估流程示意图。

图4 可用性评估流程

根据汉明距离的定义,在本文中表示任意2条物理指纹之间的相异比特数。由于本文中考虑的应用场景为通过服务器端发送指定激励给匹配通信终端和非匹配通信终端,相同激励情况下才具有可比较性,所以也可以理解为2条物理指纹中响应的相异比特数。

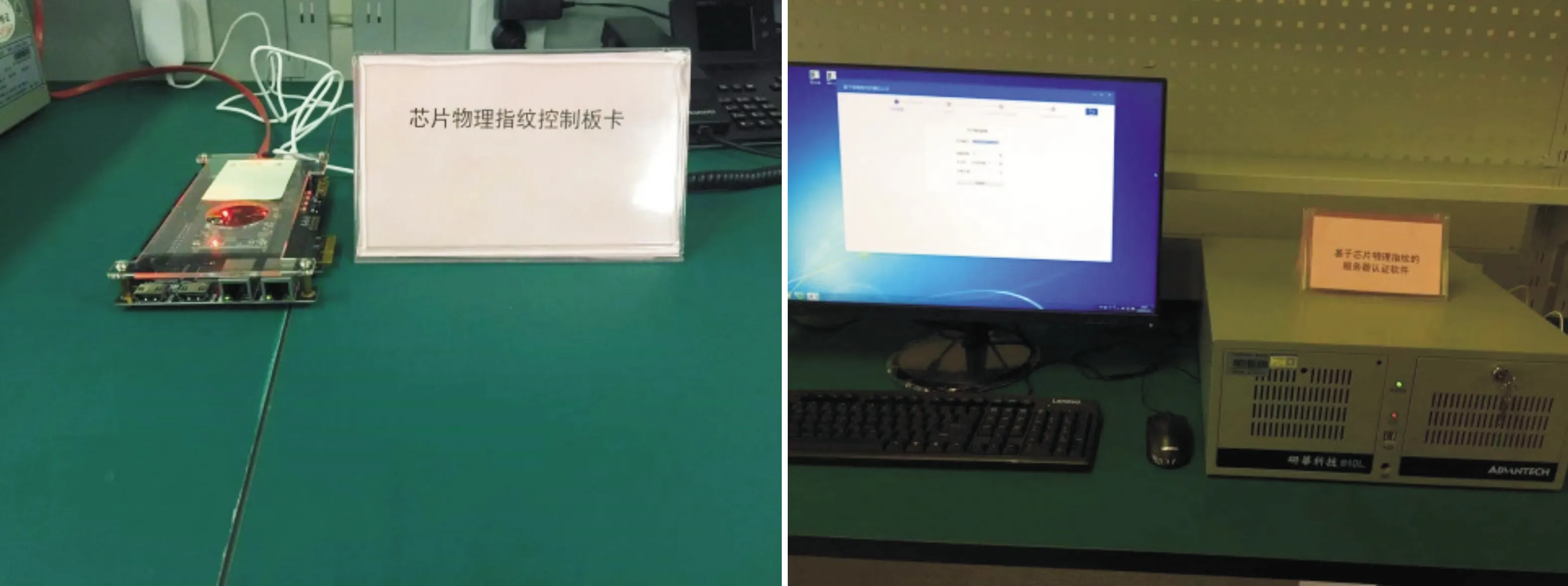

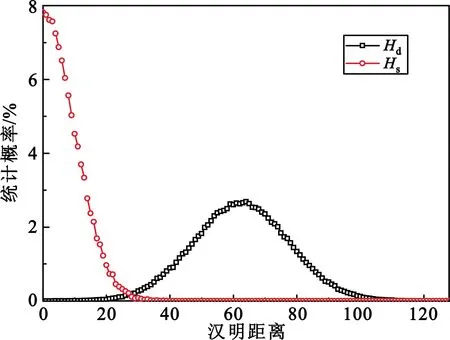

待评估指纹库中由同一芯片对同一激励产生响应的汉明距离数列为Hs,由不同芯片对同一激励产生响应的汉明距离数列为Hd。图5所示的实验中,设计了8块基于相同RO电路结构的芯片物理指纹板卡并对其指纹进行提取,测试数列Hs的值主要集中在[0,10]区间。为了更清晰地表述研究思路及方法,本文对数列Hs与Hd的值进行扩展,同时在实测数据的基础上加入随机性的波动模拟更多样本的芯片物理指纹提取模块。示例数据来源于4组芯片物理指纹,每组指纹采集于100个模拟芯片物理指纹提取模块,设置了50个128 b的激励集合,每条激励重复测试20次并对响应进行记录。

图5 芯片物理指纹提取测试环境

2.2 计算可用性因子

如图6所示,为测试中第1组芯片物理指纹的数据,数列Hs与Hd的分布情况反映了芯片物理指纹的随机性和稳定性特征,理想状态下Hs的值应是0,在足够大的样本条件下Hd均值应是64。

图6 第1组指纹库汉明距离-统计概率分布

可以对指纹库可用性因子R进行计算,表示为

(1)

式中:ΔHs、VHs分别表示数列Hs的均值与方差,ΔHd、VHd分别表示数列Hd的均值与方差,Hmax表示响应位数,σ为正态分布修正值。σ是基于数列Hs、Hd分布情况的一个经验参数,计算出的R可用于对指纹库的可用性大致判断,R的值越大,可用性一般越好。

2.3 计算认证错误特征值

本文采用了一种基于认证阈值的认证协议,当认证时激励产生的响应与指纹库中对应响应的相异比特数小于认证阈值A时,认为通信终端通过认证。认证错误接受率表示服务器将激励发送给非匹配通信终端但被判定为认证通过的情况,认证错误拒绝率表示服务器将激励发送给匹配通信终端但被判定为认证不通过的情况,因此认证错误接受率FA和认证错误拒绝率FR可以通过下面的表达式进行表示:

(2)

(3)

(4)

(5)

(6)

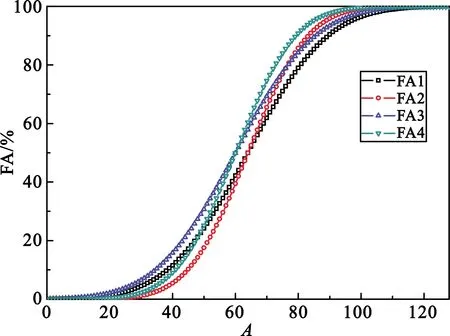

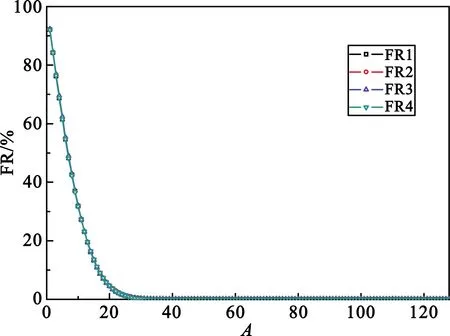

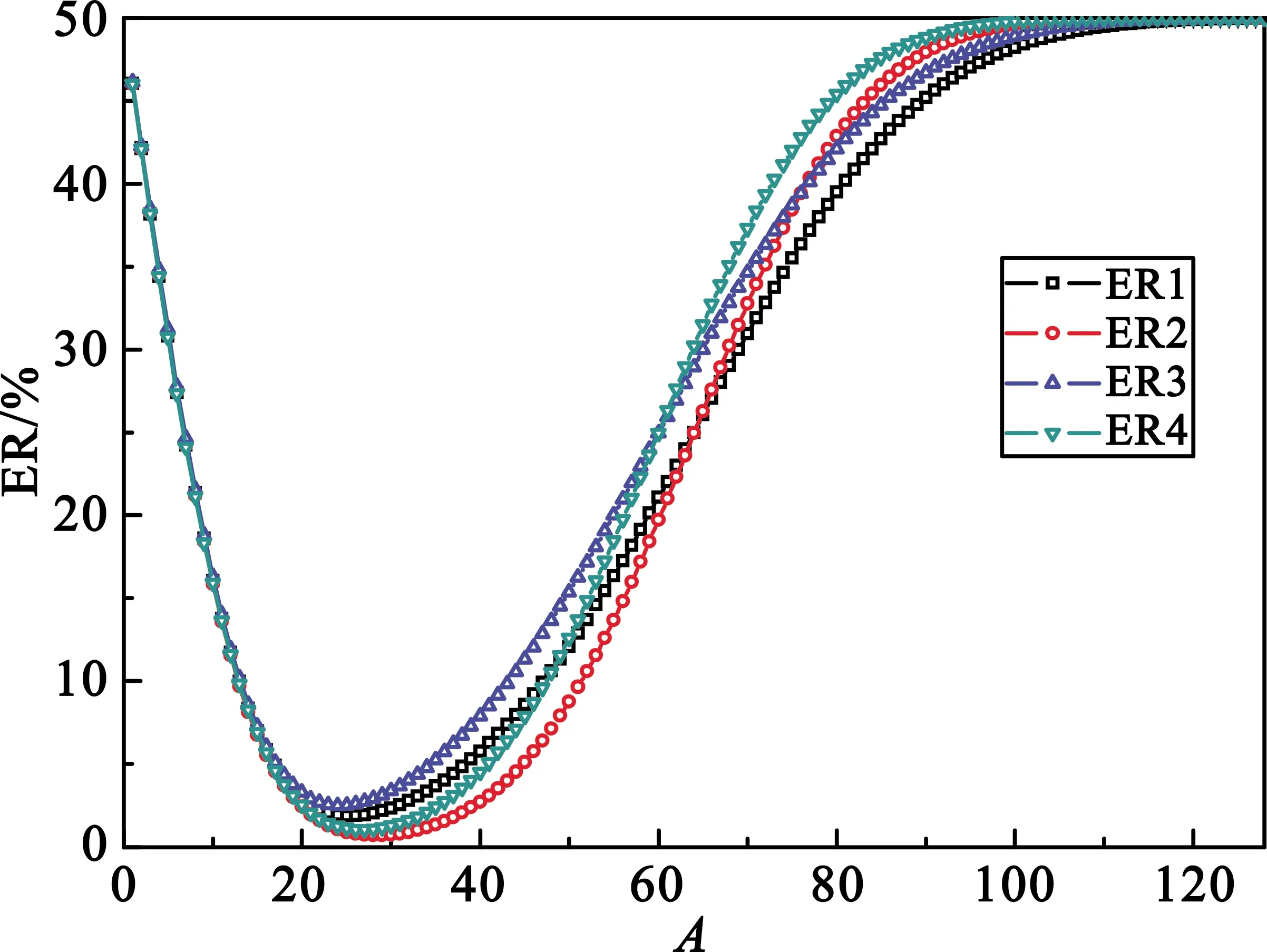

式中:P为待评估芯片的个数,K为每条激励对每个芯片测试的次数,HD(rm,i,j,rn,i′,j)指第i个芯片的第j次激励的第m次响应和第i′ 个芯片的第j次激励的第n次响应的汉明距离,认证阈值A由实验人员根据实际安全强度需求进行设定。图7和图8分别为测试中认证错误接受率和认证错误拒绝率的分布情况,认证阈值越大,认证错误接受率越高,认证错误拒绝率越低。

图7 第1~4组指纹库认证阈值-认证错误接受率分布

图8 第1~4组指纹库认证阈值-认证错误拒绝率分布

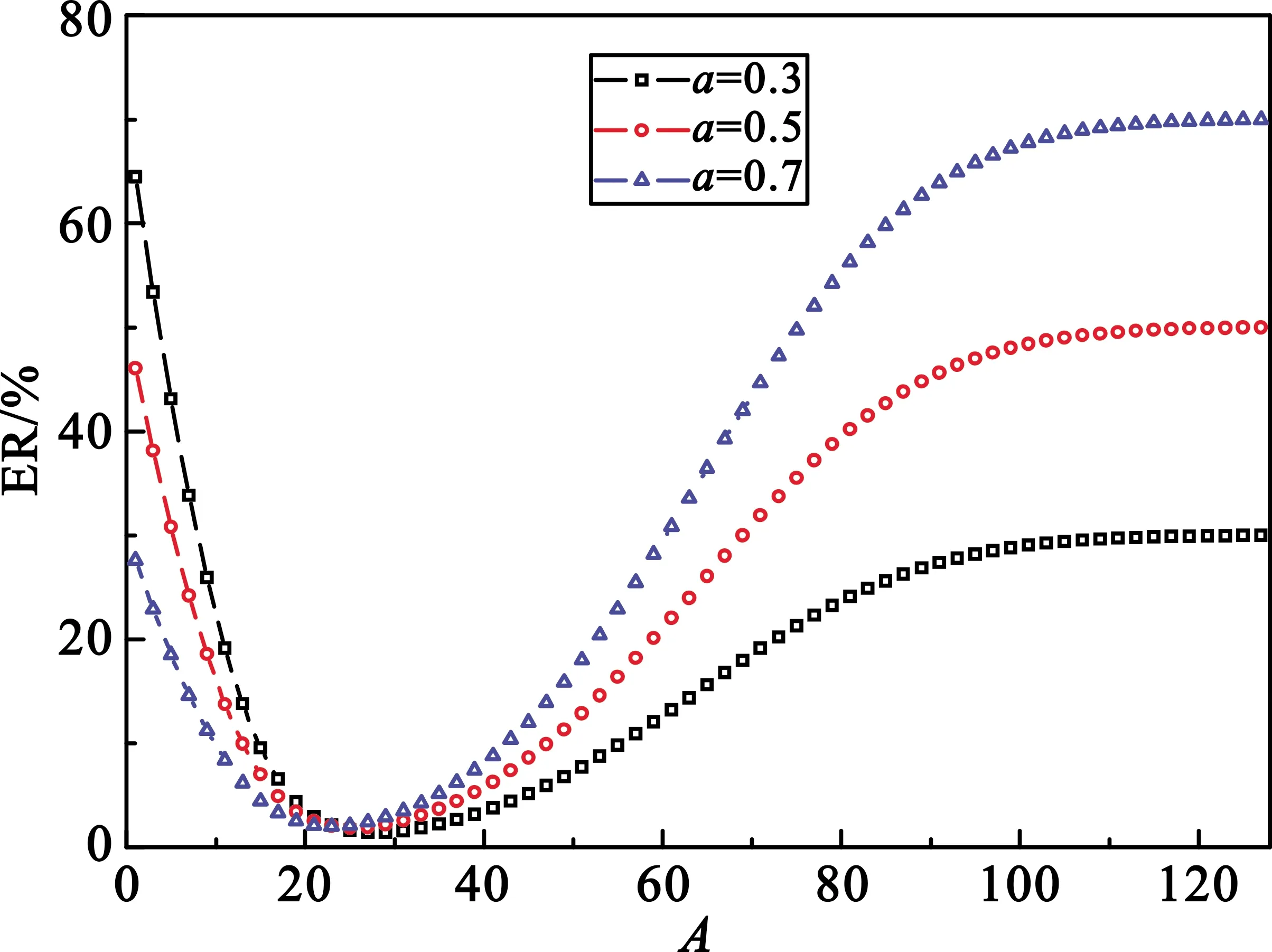

不同的应用场景对认证错误接受和认证错误拒绝具有不同的容忍度,例如在安全强度要求较高的场景中认证错误接受具有更大的危害,在业务效率要求较高的场景中人们更希望获得更低的认证错误拒绝率。为了综合表示两种典型的认证错误属性,本文提出了认证错误特征值的概念。认证错误特征值ER可以表示为

ER=αFR+(1-α)FA。

(7)

式中:α为实验人员预设的可用性权值。如图9所示,在认证应用中通常选取认证错误特征值取最小值时对应的目标认证阈值。

图9 第1~4组指纹库认证阈值-认证错误特征值分布(α=0.5)

如图10所示,当α=0.3时,ERmin=1.44%,此时A=28;当α=0.5时,ERmin=1.92%,此时A=25;当α=0.7时,ERmin=2.02%,此时A=23。由此可知,最小认证错误特征值ERmin和目标认证阈值A与预设可用性权值α的设置有关。在工程应用中,可用性权值α基于应用场景特性来确定,目标认证阈值A是由工程人员来进行设置,其目标是为了获得最小认证错误特征值ERmin。

图10 α取不同值时第1组指纹库认证阈值-认证错误特征值分布

3 结束语

通过指纹库可用性因子可以对待评估芯片物理指纹库的分布情况进行一个大致的判断,通过计算最小认证错误特征值可以获得待评估芯片物理指纹库可用性因子的值并对工程应用中认证阈值的选择提供指导。通过技术调研获知,国外已将芯片物理指纹技术应用于对电气类表具以及特种装备的管理,而目前我国还未有成体系的芯片物理指纹产品,因此,除对芯片物理指纹硬件模块进一步优化外,对于工程化应用的标准化、体系化建设还需要完善。

本文分享了一种关于芯片物理指纹的可用性方法研究,希望能够和更多的研究人员进一步交流,加快推进我国芯片物理指纹领域的工程化应用体系建设,为我国各类物联网安全需求提供技术以及应用支撑。