基于非对称耦合线的小型宽带阻抗匹配器设计与实现

魏曦东,肖灯军

(1.中国科学院空天信息创新研究院,北京 100190;2.中国科学院大学电子电气与通信工程学院,北京 100049)

阻抗匹配是微波电路设计中的重要环节,随着微波电路向宽频带和小型化的方向发展,对尺寸小、带宽大的阻抗匹配器的需求日益增大。阻抗匹配器通常存在相对带宽小、电路尺寸大等问题。耦合线因其设计参数多,设计自由度大,基于耦合线的元件开发成为近几年的研究热点[1-6]。有学者提出采用对称耦合线设计阻抗匹配器[7],以减小电路尺寸,增大匹配带宽。对称耦合线由于具有对称的特点,因而在分析和设计上相对容易,但也使电路性能受到限制。有学者进一步提出采用非对称耦合线来设计阻抗匹配器[8-13],在设计上引入更多自由度以提高性能。通过设计耦合线奇偶模阻抗和端接负载即可实现阻抗变换,完成阻抗匹配。当负载以反馈环节的形式连接耦合线端口时,如图1所示,可以为反射系数提供更多零点以实现宽带匹配。

图1 耦合线阻抗匹配器示意图Fig.1 Schematic diagram of coupled line impedance matcher

Barik等提出采用终端短接耦合线串联传输线的方法实现阻抗变换,所设计的阻抗变换器阻抗变换比为5,回波损耗20.36 dB,相对带宽38%[8]。Amin等提出采用耦合线结合5段四分之一波长传输线设计阻抗匹配器,其变换比为4,但电路尺寸较大[10]。Ang等采用耦合线实现的阻抗变换器,阻抗变换比为3.4,相对带宽为20%[14]。Zhurbenko等提出可以设置两段阻抗不同的传输线以补偿因非均匀介质引起的耦合线电长度的差异,使匹配器反射系数的极小值点均匀分布[13]。本文在其工作的基础上增加了两段传输线,试图在设计上增加自由度来减小所需的耦合线长度,减小电路尺寸。同时,本文尝试采用集总元件对传输线进行等效,一方面可以进一步减小电路尺寸,另一方面也增强了电路的可调试性。

目前,关于匹配器的文献大多以纯阻性负载进行试验。本文以混频器HMC553进行试验更加接近实际情况,可用于改善射频链路中的级间匹配。

1 设计与仿真

1.1 设计原理

非对称耦合线阻抗匹配器电路可以等效为二端口网络,如图2所示。其中,[Z]为非对称耦合线阻抗矩阵,[Z"]为任意负载阻抗矩阵,Zg为源阻抗,ZL为负载阻抗,[Z̍]为二端口网络整体阻抗矩阵。通过对[Z]和[Z"]进行设计,即可实现ZL和Zg在特定频带内的匹配。

在1端口处的反射系数可以由式(1)计算:

图2 非对称耦合线阻抗匹配器结构图Fig.2 Structure diagram of impedance matcher based on asymmetric coupled line

根据耦合线的阻抗矩阵和2,4端口处的边界条件,可以分析出1端口处输入阻抗Zin的表达式为

式中:

非对称耦合线阻抗矩阵[Z][13,15]和反馈环节阻抗矩阵[Z"]的推导结果请参见附录A与附录B。

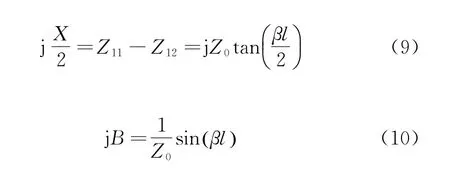

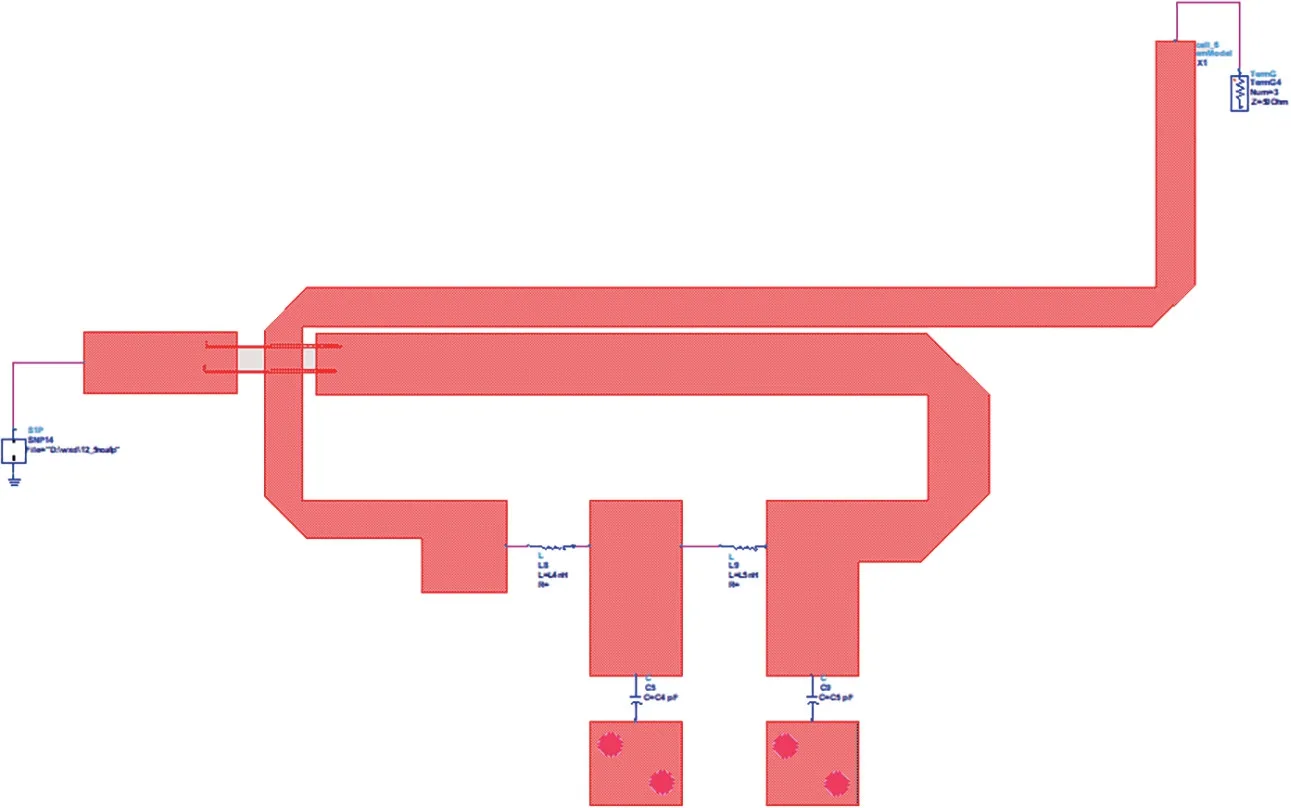

短距离传输线可以等效为T型网络[12],如图3(a)所示。一段特性阻抗为Z0,电长度为βl的传输线,其阻抗矩阵为

根据T型网络的阻抗矩阵可计算出各元件值

当βl<π/2时,串联元件呈感性(X=ωL>0),并联元件呈容性(B=ωC>0),可以计算出对应的电容和电感值。若βl<π/4,则可以进一步近似为

当Z0较大时,C≈0,等效电路如图3(b)所示;当Z0较小时,L≈0,等效电路如图3(c)所示。因此,控制电感和电容元件的取值可以等效为控制传输线的长度和宽度,以达到灵活设计、方便调试的目的。等效前后的原理图如图4所示。

1.2 设计方法

本文所设计匹配器的设计目标如表1所示。

由于设计公式复杂,设计参数较多,所以难以通过分析的方法计算出相应参数,可以采用ADS的参数优化功能自动计算出满足设计目标的参数值,仿真原理图如图5所示。

表1 设计目标Tab.1 Design target

图3 传输线等效模型Fig.3 Equivalent model of transmission line

图4 原理图Fig.4 Schematic diagram

图5 ADS仿真原理图Fig.5 ADSsimulation schematic diagram

各元件优化后的参数值如表2所示,优化结果如图6所示。

表2 优化后参数值 Tab.2 Optimized parameter value mm

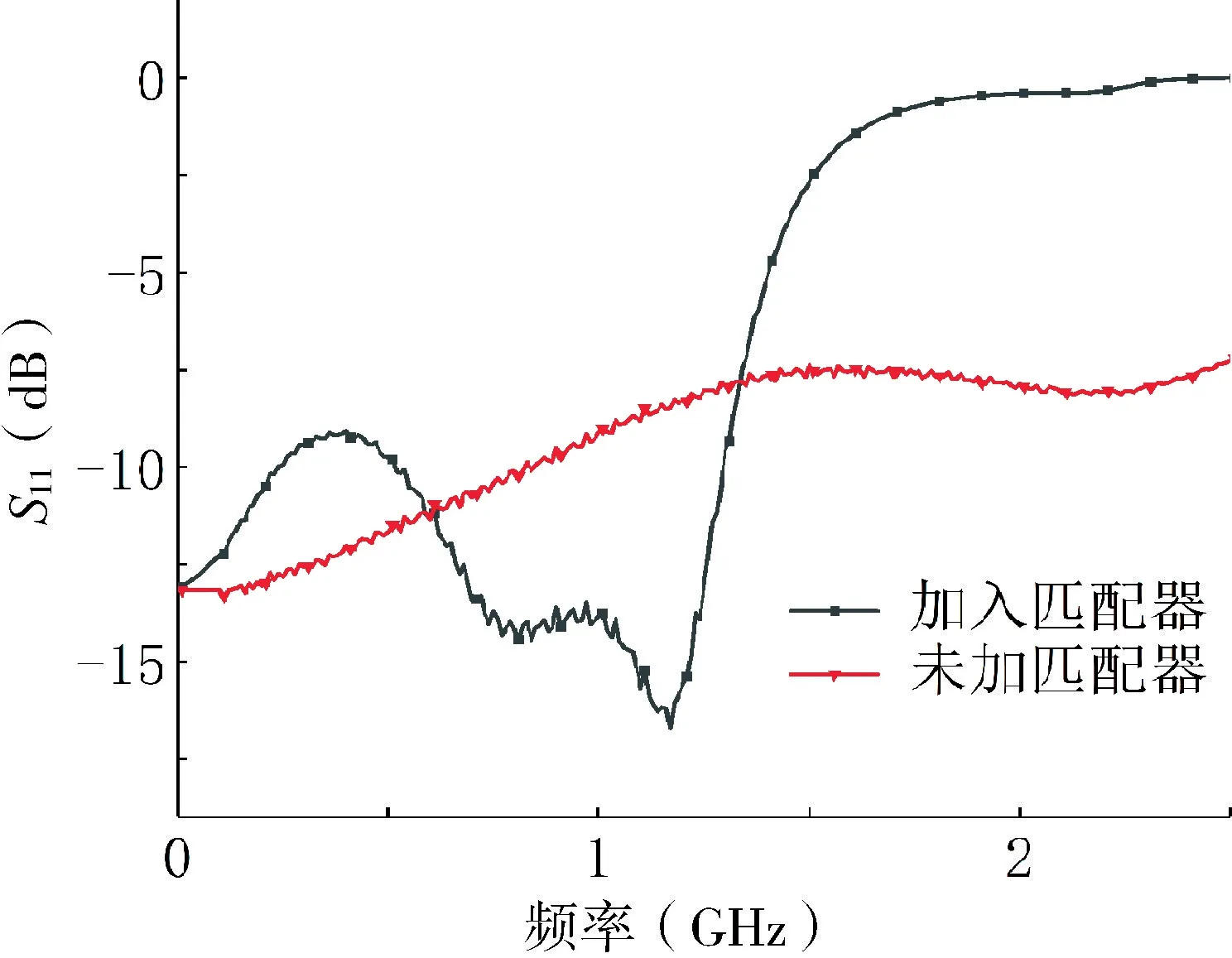

根据优化得到的传输线参数可以计算出对应的电容和电感值,并对传输线进行替代,如图7所示。替代之后的仿真结果如图8所示,二者较为吻合。

由于上述仿真是在理想情况下进行,并没有考虑实际电路中因焊盘、走线、耦合、引线等因素带来的影响,因此需进行原理图-版图协同仿真,如图9所示。仿真结果如图10所示,电路的S11参数有所恶化。

图6 原理图仿真结果Fig.6 Schematic simulation results

图7 集总元件替代之后的原理图Fig.7 Schematic diagram after replacement of lumped components

图8 集总元件替代前后的仿真结果Fig.8 Simulation results before and after lumped element replacement

2 测试结果与分析

针对上述原理和设计方法,本文进行了实物验证。实际电路采用Rogers RT6010基板、ATC 射频电容和绕线电感,通过微组装技术装配而成,实物照片如图11所示。

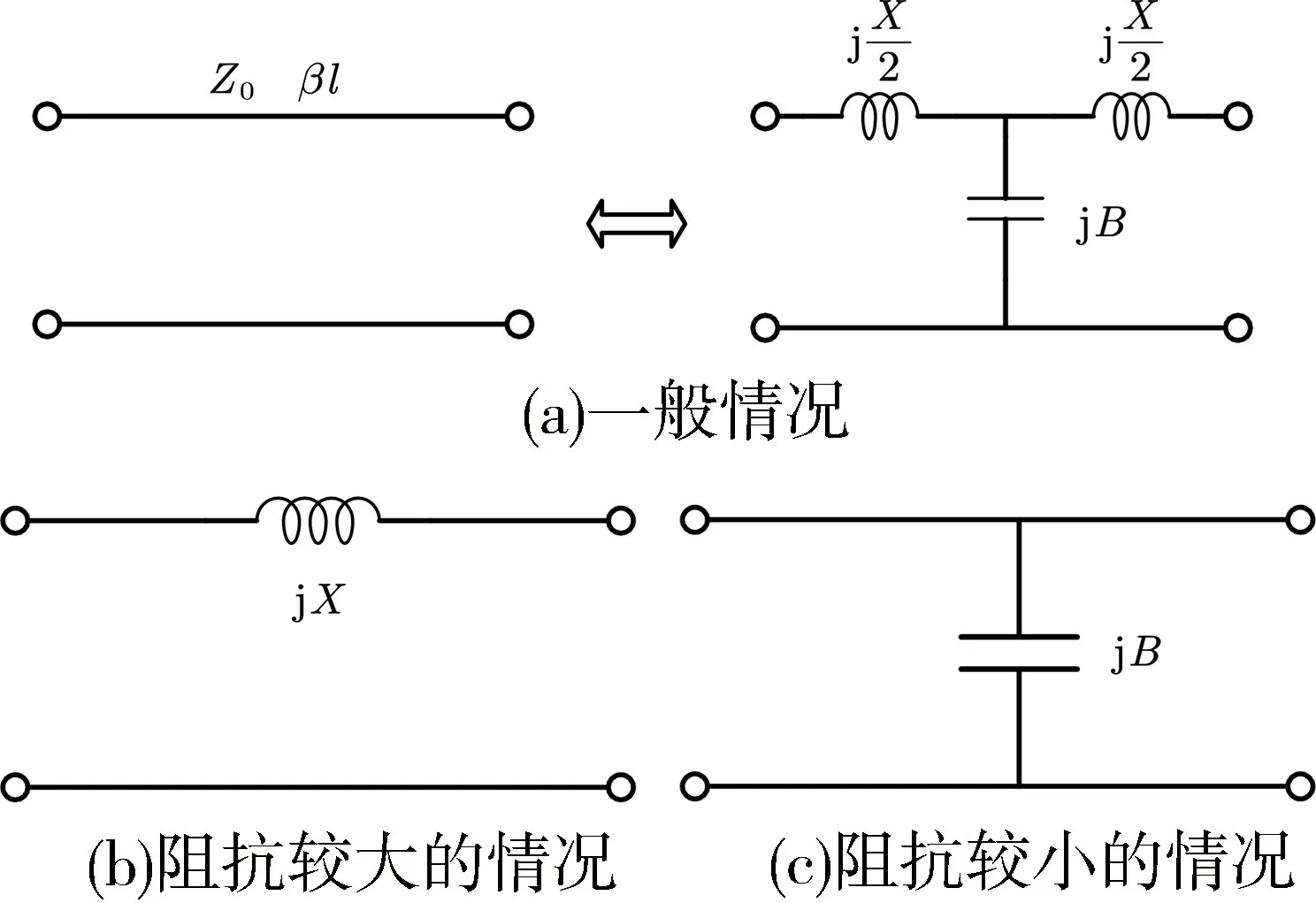

首先测量混频器中频端口的S11参数,测试方法如图12所示。其次,在中频端口加入匹配器测量S11参数。

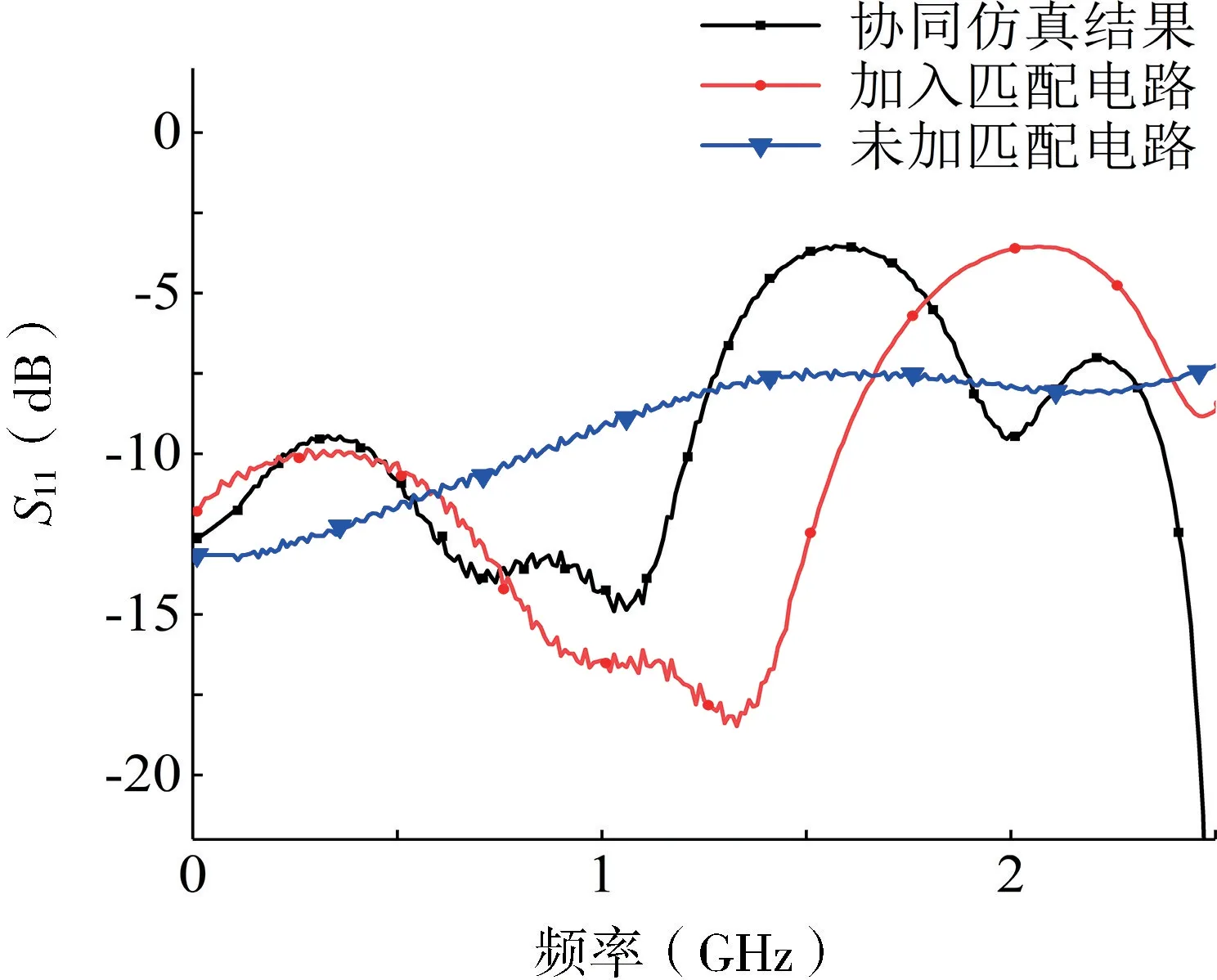

测试结果如图13所示,由图可见,所设计的匹配器在850 MHz~1.45 GHz频段中可将混频器中频端口的回波损耗改善6 dB。通过对比可以发现,实际测试结果较仿真结果仍存在150 MHz的频率偏移,但匹配带宽有所增大,对S11的改善也更为明显。这是由于调节电容电感可以灵活改变通带内的S11曲线形状,使实际测量结果尽可能地接近仿真结果,但对频率的调节比较有限。匹配器的匹配频率范围主要与耦合线以及与其相连的微带线的参数有关,匹配器存在频率偏移的原因可能与微带线的加工误差或其寄生效应有关。通过进一步仿真发现减小耦合线长度l,增大耦合线宽w1可在一定程度上减小频率的偏移。

图9 协同仿真图Fig.9 Co-simulation diagram

图10 协同仿真结果Fig.10 Co-simulation results

图11 实物照片Fig.11 Practical photos

图12 混频器中频端口S11参数测试方法Fig.12 Test method for S 11 parameter of mixer IF port

图13 S 11参数测试结果Fig.13 S 11 parameter test results

匹配电路插入损耗的测试方案如图14所示。

图14 混频器射频-中频端口S 21参数测试方法Fig.14 Test method for S 21 parameters of mixer RF-IF port

测试结果如图15所示,由图可见,所设计的匹配器插入损耗为0.2~0.5 dB。

图15 S 21参数测试结果Fig.15 S 21 parameter test results

表3列出了其他文献中设计的阻抗匹配/变换器的相应参数。对比可知,本文所设计的阻抗匹配器具有尺寸小、相对带宽大、易于调试以及可以匹配复杂阻抗的特点。

表3 阻抗匹配/变换器参数对比Tab.3 Comparison of impedance matcher/transformer

3 结论

本文提出了一种基于非对称耦合线的小型宽带阻抗匹配器的设计方法,相对带宽可达50%以上,尺寸仅为7 mm×10 mm,插入损耗为0.2~0.5 dB。区别于前人的设计方法,本文提出采用集总元件对传输线进行等效,缩小了电路尺寸,提高了匹配器的可调节性。最后,本文以混频器HMC553为例进行试验,验证了此方法的可行性,测试结果与仿真结果一致。由于微带线和耦合线的加工误差与寄生效应,实际测试结果较仿真结果存在频率偏移。本文为阻抗匹配器的设计和改善射频链路中的级间匹配提供了一种新思路。