Si基Ga N 射频器件研究进展

房柏彤,朱广润,张 凯,郭怀新,陈堂胜

(南京电子器件研究所,江苏 南京 210016)

第三代半导体氮化镓(GaN)材料具有禁带宽度大、电子饱和速度及电子迁移率高、击穿场强高等特性[1],使GaN HEMT器件拥有高频率、高功率、耐高温高压、抗辐射等优点,在射频领域有广阔的应用前景,得到了美国Cree等半导体巨头公司的关注[2-4],国内也有北大、西电[5]以及中国电科等单位进行长期的研究。

碳化硅(SiC)材料的热导率高,晶格匹配性优异,由其外延得到的GaN 薄膜结晶质量是最优的,然而SiC衬底的价格高昂,晶圆尺寸小(3~4英寸为主),不利于GaN射频器件的产业化。硅(Si)材料的价格低廉、晶圆尺寸大(≥6英寸)、热导率良好,若能解决Si CMOS工艺与GaN制备工艺的兼容问题,即可低成本、大规模地生产GaN射频器件,进而推动5G通信及其他新兴技术的普及应用。此外,除了传统的单一射频芯片或功率器件外,还可利用Si工艺平台实现GaN射频器件与功率器件的单片集成,以及与Si器件的异质异构集成等,大幅提升电路性能与集成密度,推动智能前端芯片技术发展。因此Si基GaN 技术正受到国内外科研院所与产业界越来越多的关注[6-8]。

本文主要调研了近年来国内外关于Si基GaN 射频器件在材料、工艺与电路上的研究进展,剖析了相关技术难点与存在问题,并展望了Si基GaN 射频器件未来的优化发展方向。此外还基于射频损耗较低的高阻Si上AlGaN/GaN HEMT 材料,报道了研制的0.25μm及0.4μm工艺下的Si基GaN射频器件,经测试在C波段及X波段下工作性能优异,揭示了Si基GaN射频器件在5G 应用及低成本雷达等领域的独特优势和应用前景。

1 国内外研究现状

自20世纪90年代初,Khan等[9]在蓝宝石衬底上率先制得了AlGaN/GaN 结构,随后AlGaN/GaN HEMT的直流及微波特性相继被报道[10-11],关于GaN HEMT器件的研究逐渐成为热点。由于GaN 单晶难以制备,GaN HEMT器件一般由异质外延生长得到,所使用的衬底材料有SiC、蓝宝石、Si三种。半绝缘SiC材料由于具备良好的晶格匹配性和优良的热导率,一直是GaN HEMT外延衬底的最佳选择。然而,SiC作为衬底存在着晶圆尺寸小、成本过高的问题,严重限制了GaN器件的推广应用。而对于蓝宝石衬底,其晶圆尺寸较大且价格较为便宜,但其硬度太高、热导率极低且晶格失配大,不利于后续加工与应用。相较之下,Si衬底上GaN技术不仅具有较好的热导率和最低的衬底成本,而且晶圆尺寸大,起点6英寸且易升级到8英寸以上,并可与Si工艺线兼容,具有显著的成本优势和规模化生产能力。下面将介绍近年来国内外关于Si基GaN射频器件的研究进展。

1.1 Si基GaN射频材料优化生长

Si与GaN之间存在的较大晶格失配和热失配是制约Si基GaN技术发展的主要瓶颈,由失配产生的位错与应力会严重影响结晶质量,并恶化器件性能。因此如何消除各外延层之间的应力,探究出有效的应力调控技术,是改善Si基GaN 射频器件各项特性的基础。此外,与电力电子器件不同,Si基GaN射频器件由于高阻Si晶圆难以制备,且衬底与成核层界面处易形成导电层,导致器件在高频工作状态下存在射频损耗,限制输出功率和效率。因此,如何优化衬底及外延结构,抑制射频损耗,是实现Si基GaN 射频器件大规模高效应用的关键。

2019年,Tzeng等[12]在8英寸Si衬底上分别制备了Al组分渐变AlGaN 缓冲层和AlGaN/GaN 超晶格缓冲层两种结构的GaN HEMT 器件,如图1所示。经TEM、XRD、拉曼光谱、AFM、EPD、直流特性以及频率特性等系统地测试分析比较两种结构对器件各项性能指标的影响,发现采用AlGaN/GaN 超晶格缓冲层结构的器件无论是结晶质量还是直流特性或频率特性均展现出更优的测试结果,在0.17μm 栅长下测得fT和fmax分别达到41.6 GHz和126.46 GHz。同年Yang等[13]设计了Si掺杂的AlGaN背势垒层以及C掺杂的GaN缓冲层得到了漏电小、耐击穿且电流崩塌效应低的Si基AlGaN/GaN HEMT 器件。2020 年,Xia等[14]分析了GaN 和SiN 两种不同帽层结构对AlN/GaN HEMT器件性能退化的抑制效果,发现带有3.5 nm原位钝化SiN帽层以及4.5 nm AlN势垒层结构的Si基GaN HEMT器件具有最低的薄层电阻、最高的二维电子气浓度(Two-Dimensional Electron Gas Density)以及最好的稳定性。

图1 采用组分渐变AlGaN的缓冲层结构(a)和AlGaN/GaN超晶格的缓冲层结构(b)[12]Fig.1 Structure of stacked Al x Ga1-x N buffer(a)and AlGaN/GaN superlattice buffer(b)[12]

2017年,Luong等[15]采用HLH Temperature的生长模式在高阻Si衬底(104Ω·cm)上外延出100 nm的AlN缓冲层,得到的GaN HEMT 有效抑制了因AlN/Si之间晶格失配所产生的张应力,从而降低极化电场强度,减小射频损耗。通过对长度为1 mm 的共面波导(CPW)测试,10 GHz下射频损耗仅0.4 dB/mm,40 GHz下的射频损耗低于1.2 dB/mm,材料结构及测试结果如图2所示。同年,Cordier等[16]采用NH3-MBE技术,在高阻Si衬底(104Ω·cm)上生长了0.2μm的AlN 成核层和0.5μm 的GaN 缓冲层,此生长模式相较于MOCVD 更易控制AlN/Si间的界面态,且其低温生长特性能在抑制界面态漏电的同时保证高结晶质量。经测试35 GHz下的射频损耗低于0.3 dB/mm,且70 GHz下的射频损耗低于0.5 dB/mm,并对比了不同Al N生长温度对射频损耗的影响,如图3所示。此外,Chiu等[17]利用绝缘衬底上硅(SOI)制备了AlGaN/GaN MISHEMT,采用SOI 衬底的HEMT器件具有低寄生电容、低射频损耗、高衬底绝缘度等适用于射频器件的优点,经测试0.25μm 栅长下fT和fmax分别达32.1 GHz和51.9 GHz。

可以看出合理的帽层、势垒层以及缓冲层等结构设计不但能够调控应力提高结晶质量,还能使器件具备优异的直流特性和频率特性,与此同时要优化衬底及成核层结构以求降低射频损耗,一方面可以提高AlN的结晶质量并抑制AlN/Si间的界面态,另一方面应从缓冲层及Si衬底入手,提高器件绝缘度,减小漏电。

图2 高低阻Si衬底上外延100 nm HLH AlN的射频损耗[15]Fig.2 RF loss of 100 nm HLH AlN on HR or LRSi substrate[15]

1.2 无金的Si基GaN工艺技术

现有的Si基射频GaN 器件制造工艺几乎都是基于有金(Au)工艺完成的。Au是传统GaN器件欧姆接触工艺中的必备金属之一,采用Ti/Al/X/Au(X 可为Ti、Ni、Mo、Pt等)结构合金的接触电阻可达到0.3 Ω·mm 左右,且性能稳定。然而,含Au的GaN 制备工艺存在着成本高以及与传统CMOS工艺不兼容等问题,提高了Si基GaN 射频器件的生产成本。实现无Au工艺的关键是做到源漏金属的无Au化,对此已有Ti/Al/TiN、Ti/Al/Ti/TiN、Ti/Al/W、Ti/Al/Ti/TiW、Ti/Al/Ni/Pt、Ti/Al/NiV 等方案提出,所获得的欧姆接触电阻一般在0.5~1.0Ω·mm,尽管这些方案能够一定程度地满足电力电子功率器件的需求,然而面对射频器件对寄生电阻的严格要求仍存在较大的差距。

图3 不同温度下采用NH3-MBE技术生长GaN/AlN缓冲层的射频损耗对比[16]Fig.3 RF loss of GaN/AlN buffer layers grown by NH3-MBE at different temperatures[16]

2017年,Ferreyra等[18]采用脉冲激光烧蚀技术(PLD),在Si衬底上制备了表面光滑且形貌良好的n+-GaN,并在其上淀积Hf/Al/Ti(20/200/20 nm)形成无Au欧姆接触,此外Hf金属的功函数(3.5 e V)低于Ti(4.1 eV)与TiN(4.7 eV),故更适合作为欧姆接触的电极,经测试得到接触电阻为0.17Ω·mm,比接触电阻可达10-7Ω·cm2量级。2018 年,Zhang等[19]在Si衬底上经势垒层刻槽处理后,采用Ti/Al/Ti/TiN(2.5/100/20/60 nm)的无Au欧姆接触工艺制备了AlGaN/GaN HEMT器件,退火后的结构如图4所示。其中底层金属Ti的厚度仅为2.5 nm,既能够形成厚度适宜的TiN 层让Al与TiN 发生固相反应生成AlN,又不会因Ti太厚而阻止两者反应,使接触电阻大大降低,在550℃下合金得到的接触电阻与比接触电阻分别为0.21Ω·mm和1.16×10-6Ω·cm2。

可见采用二次外延高质量n+-GaN、势垒层刻槽以及无Au欧姆接触等技术,能够得到较低的接触电阻和比接触电阻并改善表面形貌。此外无Au的欧姆接触工艺也为实现无Au的Si基GaN技术,降低生产成本提供了保障。

图4 Ti/Al/Ti/TiN在550℃退火后的HR-TEM 图[19]Fig.4 HR-TEM images of Ti/Al/Ti/TiN after 550℃annealing[19]

1.3 复合钝化的Si基GaN工艺技术

为了解决Si基GaN 射频器件的电流崩塌问题,一般需要在器件表面淀积SiN 钝化保护层,其能够有效抑制表面态对电子的俘获效应,从而抑制电流崩塌,但是与此同时沟道的电子浓度也会提高,短沟道效应也随之加剧,恶化输出特性和关断特性。此外SiN钝化层通常由PECVD低温生长得到,此工艺会导致SiN薄膜中H离子杂质过多且致密性较差,钝化效果不理想。并且由于Si衬底的绝缘度远不如SiC衬底,漏电问题也严重制约着Si基GaN 射频器件的性能。因此探究高水平的先进钝化工艺是有效抑制电流崩塌和表面漏电的关键技术方案。LPCVD不同于PECVD,是一种高温钝化SiN 的工艺,通常在器件工艺开始前完成,生长得到的钝化层致密性好、质量高。原位钝化MOCVD是一种在GaN生长结束后继续生长SiN保护层的方法,能够有效避免器件表面受到外界环境的污染,故钝化效果良好。

2019年,Zhang等[20]采用LPCVD 技术在GaN表面生长了一层20 nm 的SiN 钝化层,经CV 测试分析发现由LPCVD 生长的钝化层相较于PECVD 具备更好的致密性,并且能够有效抑制表面漏电。2020年,Chen等[21]采用原位钝化MOCVD 技术在势垒层上生长了3 nm的SiN作为栅介质,制得0.7μm 栅长的AlGaN/GaN MISHEMT器件性能良好,电路开关比达106,电流退化率为18%,测得fT和fmax分别为12.5 GHz和15 GHz。为了比较PECVD、LPCVD复合钝化以及原位钝化MOCVD对电流崩塌以及表面漏电的抑制作用,Huang等[22]用上述三种不同的方式在同种器件结构上制备了三种SiN钝化层,钝化效果对比如图5 所示,可以看出LPCVD 复合钝化层(Bilayer)的曲线波动是最小的,说明该种钝化方式对电流崩塌和表面漏电的抑制效果最好。

为在抑制电流崩塌的同时减小漏电,并改善PECVD钝化带来的致密性差、H 离子杂质多等问题,可采用原位钝化MOCVD以及LPCVD生长高质量的钝化层。然而致密性过高的钝化层难以刻蚀,会影响后续器件工艺开展,对此可采用复合钝化的办法,在一层较薄的原位钝化MOCVD SiN 或LPCVD SiN 上通过PECVD继续生长SiN,最终形成的高质量复合钝化层既有很好的保护作用又便于后续器件工艺的进行。

图5 三种钝化层的效果对比[22]Fig.5 Comparison of three different passivation[22]

1.4 Si基GaN射频器件与电路设计

伴随着材料结构设计和器件制备工艺的持续改进,Si基GaN射频器件及其电路的性能也不断刷新着行业记录。

在微波毫米波频率特性方面,早在2004年法国GaN研究中心(IEMN)的Minko等[23]率先在电阻率为20 kΩ·cm的高阻Si衬底上制备了栅长为170 nm,且AlGaN势垒层厚度为30 nm的GaN HEMT射频器件,当源漏电压为10 V,栅电压为1 V 时,输出电流为0.55 A/mm,fT和fmax分别为46 GHz和92 GHz;并在2013年Bouzid等[24]将AlGaN势垒层的厚度降低到12.5 nm,栅长缩短到90 nm,当源漏电压为5 V,栅电压为-2.1 V 时,测得fT和fmax分别提高到100 GHz和206 GHz。2009 年,瑞士联邦理工学院(EPFL)与苏黎世联邦理工学院(ETH)合作[25],采用17.5 nm Al0.26Ga0.74N 势垒层,栅长为100 nm,源漏电压为2.5 V,栅电压为-2 V 时,输出电流为0.75 A/mm,fT和fmax分别为101 GHz和128 GHz;2015年Marti等[26]采用3.5 nm 厚的AlInN 作为势垒层,制备了栅长为50 nm 的AlIn N/GaN HEMT器件,源漏电压5 V,栅电压2 V时,输出电流为1.6 A/mm,fT和fmax分别提升至141 GHz和232 GHz。新加坡南洋理工大学(NTU)在大尺寸硅基GaN 材料外延与器件制备方面也进行了大量的研究,2012年Ng等[27]基于8英寸Si晶圆制备了栅长为0.3μm的Si基GaN射频器件,源漏电压为10 V,栅电压为-2 V 时,测试得到fT和fmax分别为28 GHz和64 GHz;接着在2014年Ranjan等[28]又报道了基于高阻Si衬底的T 型栅AlGaN/GaN HEMT器件,其采用了厚度仅为8 nm的AlGaN势垒层,栅长为0.15μm,经测试fT和fmax分别达到了63 GHz和128 GHz,击穿电压为132 V,Johnson品质因子高达8.32 THz·V。此外,在2018年他们还与MIT合作[29]报道了40 nm 栅长的I型栅In AlN/GaN HEMT器件,测得fT和fmax分别达到250 GHz和60 GHz。同年,南京电子器件研究所与苏州纳米所合作[30]报道了55 nm 栅长的T型栅AlGa(In)N/AlN/GaN HEMT器件,经测试fT和fmax分别为145 GHz和220 GHz,可与国外先进研究成果相媲美。

在微波功率方面,日本OKI公司的Shinichi等[31]在2009年就有相关研究成果报道,在源漏电压为70 V,工作频率为2.14 GHz时,测试高阻Si基GaN射频器件功率特性,得到输出功率密度(Pout)达12.88 W/mm,最大功率附加效率(PAE)达64%,测试结果表明Si基GaN在射频应用方面存在巨大潜力;同年,瑞士联邦理工学院的Sun等[25]基于9 nm 厚的AlInN势垒层,研制了栅长为100 nm的Si基GaN HEMT器件,在源漏电压为15 V,工作频率为10 GHz时测得Pout为2.5 W/mm,PAE 达23%;2012 年,Chang等[32]采用斜场板结构研制的Si基AlGaN/GaN器件在8 GHz下Pout达到了5 W/mm;2014年,日本瑞萨电子的Yasuhiro等[33]制备了栅长为0.16μm 的T型栅AlGaN/GaN HEMT器件,源漏电压为30 V,工作频率为14 GHz时,Pout为3.82 W/mm;同年,首尔大学的Lee等[34]报道了研制的Si基AlGaN/GaN HEMT器件在8 GHz下的功率性能,脉冲输出功率达8.1 W/mm(脉宽为100μm,占空比为10%),功率增益为8 dB,PAE达39%,总功率接近30 W。

在毫米波功率方面,法国IEMN 的Medjdoub等[35]于2012年在4英寸高阻Si衬底上制备了AlN/GaN HEMT器件并展示了首个40 GHz频率下的功率测试结果,得到Pout为2.5 W/mm,器件结构及IDVGS曲线如图6所示;2013年Medjdoub等[36]又将40 GHz下的Pout提高到3.2 W/mm;2015 年ETH 的Marti等[26]报道了国际上首个W 波段Si基GaN 射频器件,工作频率为94 GHz时,Pout达1.35 W/mm。

图6 IEMN制备的毫米波器件结构及其I D-V GS曲线[35]Fig.6 Millimeter wave device structure and its I D-V GS characteristic designed by IEMN[35]

在产品方面,近年来在5G 通信技术和先进低成本相控阵雷达得到越来越广泛应用的大背景下,OMMIC、MACOM、IMEC 以及MIT 等海外巨头公司和机构纷纷加大投入,在器件性能、成本和技术等方面展现出卓越的市场竞争实力,其中代表公司有MACOM 和OMMIC。

MACOM公司自2014年起着力研究Si基GaN技术,并逐渐将重心从SiC基GaN芯片转移过来,截至目前已经开发了多代Si基GaN射频器件,向通信、军事以及其他应用领域的客户提供了上百万件基于Si基GaN技术的产品。采用标准的0.5μm HEMT工艺制程制备的分立及集成放大器,能够在直流到6 GHz的超宽频带范围内工作,同时产品的增益、增益平坦度、效率以及稳定性均处于行业领先水平,如NPTB00004A型宽带GaN晶体管在28 V工作电压以及2.5 GHz频率下的线性增益达14.8 dB,Pout为5 W,且PAE超过55%,凭借其超宽的工作频率范围可应用于L/C波段雷达、无线通信以及航空航天等领域。此外MACOM公司还于2018年宣布了与意法半导体(ST)的合作计划,由ST协助MACOM 生产晶圆,显著提升了Si基GaN射频芯片的产能以及国际竞争力。

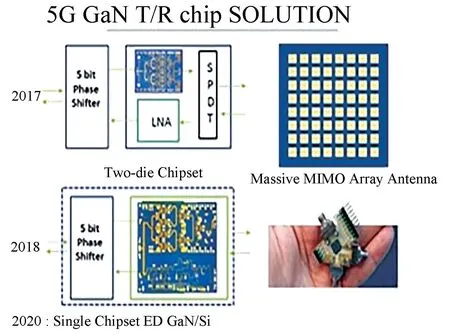

OMMIC公司于2006年开始Si基GaN 毫米波功放的研究,并于2015年开发出100 nm 制程下的Si基GaN器件制备工艺技术(D01GH),在30 GHz时,Pout达3.3 W/mm,40 GHz下的噪声系数为1.5 dB,已接近SiC基GaN 器件性能。紧接着在2016年公布了首个基于Si基GaN技术的高性能T/R芯片,能够在37~43 GHz频率范围内工作,40 GHz下的总输出功率达10 W,且PAE达30%,实现了低噪放、功放以及开关的单片集成,可较好地应用于雷达、通信以及航空等领域。目前OMMIC公司已具备全球领先的6英寸Si基GaN 生产线,并且制程推进到60 nm(D006GH),未来将继续向下开发40 nm 线宽的Si基GaN制程,并向市场提供功放、低噪放、开关以及移相器完全集成,且兼容增强型和耗尽型器件的T/R芯片单片化方案,其T/R芯片的发展路线如图7所示。

可见尽管Si基GaN 器件在性能方面与SiC 基GaN器件相比还存在差距,但是随着材料生长技术和器件制备工艺的逐渐成熟,Si基GaN器件的截止频率和功率密度等主要参数都在逐步提高,未来达到与SiC基GaN相媲美的性能指日可待。同时微波毫米波频段下基于Si基GaN 射频器件的产品也陆续得以发布,展现出了巨大的竞争潜力,相信在未来将逐步占据更大的市场份额。

图7 OMMIC公司发布的0.1μm Si基GaN收发芯片Fig.7 0.1μm Si-based GaN T/R chip published by OMMIC

2 Si基GaN射频器件研制

图8为制备的0.25 μm 和0.4 μm 栅长的Si基GaN材料与器件结构示意图,本结构的外延层总厚度仅有2μm左右,既能满足典型28 V电压下的正常射频工作,又可确保材料具备较低的热阻,同时对GaN缓冲层进行一定浓度的C掺杂后测得射频损耗(0.72 dB/mm@4 GHz)已接近SiC基GaN材料的结果(0.54 dB/mm@4 GHz),此外还采用了基于难熔W 金属的叠层V 型栅结构,以得到更大的击穿电压和更高的频率。

图8 Si基GaN射频材料与器件结构示意图Fig.8 Cross sectional view of Si-based GaN RF material and device structure

经Load-Pull连续波功率测试,0.4μm 器件在频率为4 GHz,电压为28 V 下的线性增益高达17 dB,PAE约为50%,Pout为4.5 W/mm。图9显示了0.25 μm器件在10 GHz的测试结果,源漏偏置电压为20 V,线性增益为12.3 dB,Pout为3.6 W/mm,PAE约为45%。

图9 10 GHz时Si基GaN器件的功率特性Fig.9 Power characteristics of Si-based GaN device at 10 GHz

此外,还将0.25μm 工艺Si基GaN 射频器件在10 GHz左右的功率特性分别与国外研究成果进行对比,如表1所示,可见研制的Si基GaN射频器件功率特性良好,达到国际先进水平。

表1 Si基GaN射频器件在X波段下功率特性对比Tab.1 Power characteristic of Si-based GaN RF devices at X-band

3 总结与展望

通过对Si基GaN 射频器件在材料生长、器件制备以及器件性能等方面的调研分析,介绍了改善Si基GaN材料结构缺陷并优化器件制备流程的可靠途径。材料方面,超晶格缓冲层、背势垒层、C 掺杂GaN层、高质量成核层、GaN帽层以及高绝缘度衬底等结构设计,均有助于改善晶格失配、漏电及射频损耗等问题,而面向于射频领域的Si基GaN 材料结构还应控制外延层厚度以获得较低的热阻;工艺方面,为最大降低成本,无Au工艺是必要选择,对于无Au欧姆接触工艺,结合二次外延n+-GaN以及势垒层刻槽等技术有助于提升表面形貌并降低接触电阻,同时结合PECVD、原位钝化和LPCVD的复合钝化工艺在对表面的保护和漏电的抑制方面均表现出良好的效果。

低成本、批量化的生产Si基GaN射频器件是5G通信、射频源等应用实现的重要保障。尽管目前国内外各研究机构在Si基GaN 射频材料外延与器件性能方面取得了一定进展,但是性能上与SiC衬底GaN相比仍然存在较大差距,而且可靠性未得到长期验证,离产业化尚存在较大距离。未来,通过提高外延材料质量,开发兼容CMOS的大尺寸制造工艺,提高Si基GaN器件与电路芯片性能,降低生产成本,有望推动GaN射频技术在各类民生领域的普及应用。