基于互连线插值的时间数字转换器结构设计

周郭飞 杨 宏

(公安部第一研究所 北京 100044)

时间数字转换器(Time-to-Digital Converter,TDC)是一种将时间变换成数字信号的转换器,已广泛用于核物理和高能物理实验以及与时间测量相关的领域[1]。随着一种全数字锁相环(All-digital Phase Locked Loop,ADPLL)的出现[2-3],TDC替代了传统锁相环中的鉴频鉴相器和电荷泵成为了数字锁相环中关键模块。在全数字锁相环中,TDC用于测量数控振荡器(Digitally Controlled Oscillator,DCO)输出的高速时钟边沿和低速的参考时钟边沿之间的时间差,从而获得这两个时钟的分数相位差。TDC是一个模拟量到数字量转换的功能模块,在数字量化过程中所产生的量化误差会引入ADPLL的带内噪声,进而对环路的相位噪声产生影响。因此为了获得好的相位噪声性能,就必须提高分辨率,尤其是在系统频率较高的情况下。

TDC的时间分辨率决定了相位的测量精度,分辨率越高锁相环的相位噪声特性越好[2]。结构简单的门延时链已广泛的用于高分辨率TDC的实现,其延时单元的延时决定着TDC的测量分辨率。减少延时单元的延时是提高分辨率的有效办法[2-3],例如采用特殊的电路结构[4-5],采用更先进的工艺[6],而插值是提高其分辨率的另一种方法[7]。在集成电路中,无源的互连线很容易实现数皮秒及以下的延时,因此可采用互连线构成等延时线以提高TDC的分辨率[7-8]。但由于因工艺偏差、电源电压等因素,基于互连线插值等延时线结构输出信号的延时差很难保持一致。为此本文在对互连线特性分析的基础上,提出了一种工艺偏差不敏感的基于互连线插值的TDC设计方法。

本文首先给出了传统门延时链的工作原理和其分辨率对ADPLL的相位噪声特性的影响。然后,通过对互连线的理论分析,提出了一种利用互连线实现等延时的设计方法,并给出了基于互连线插值的环形TDC版图设计方案。最后利用仿真对本文提出的方法进行验证。

1 TDC分辨率对ADPLL的影响

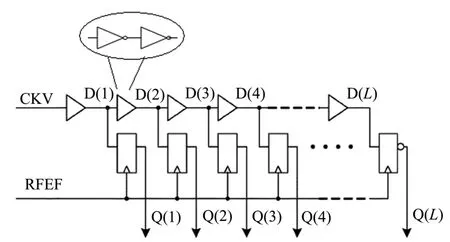

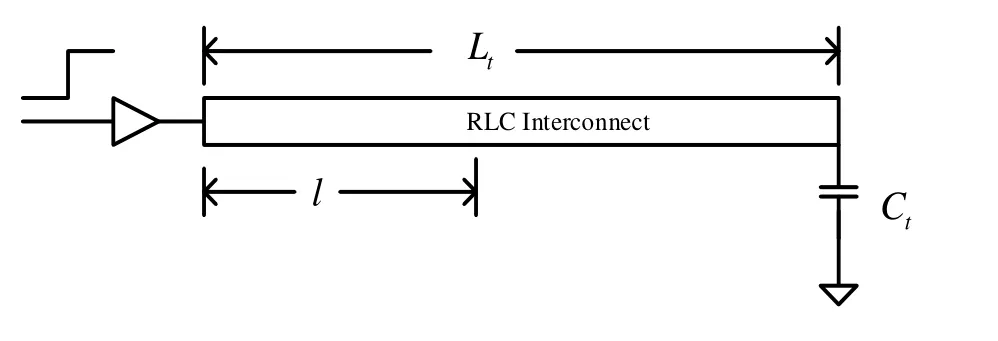

TDC是ADPLL的重要模块,用于测量其输出高速时钟(The Variable Clock,CKV)和低速参考时钟(The Frequency Reference,FREF)之间的分数相位差,其基本结构如图1所示,由延时链路和D触发器组构成的采样电路组成。当高速时钟CKV通过延时链后,会形成延时矢量,再通过D触发器用低速时钟FREF将数据采出。该数据是准温度计码,通过对该码字简单处理就可以得FREF上升沿与高速时钟CKV上升沿和下降沿的时间差。显然,延时单元的延时越小TDC时间的测量精度也就越高,时间分辨率为ΔtTDC越小。TDC时间量化误差引起的ADPLL输出信号相位噪声功率谱[9]如下:

式中:ΔtTDC为TDC的时间分辨率;TCKV为ADPLL输出的高速时钟周期;fREF为参考信号的频率。从式(1)可知:1)TDC的分辨率越高,即ΔtTDC越小,因其引起的ADPLL输出信号的相位噪声越小;2)ADPLL的输出频率越高,那么为了保证相位噪声性能,就必须选择分辨率越高的TDC。为了提升TDC的测量分辨率,本文提出了一种对工艺偏差不敏感的环形互连线插值的TDC结构。

图1 基本TDC结构Fig.1 Diagram of a basic TDC structure

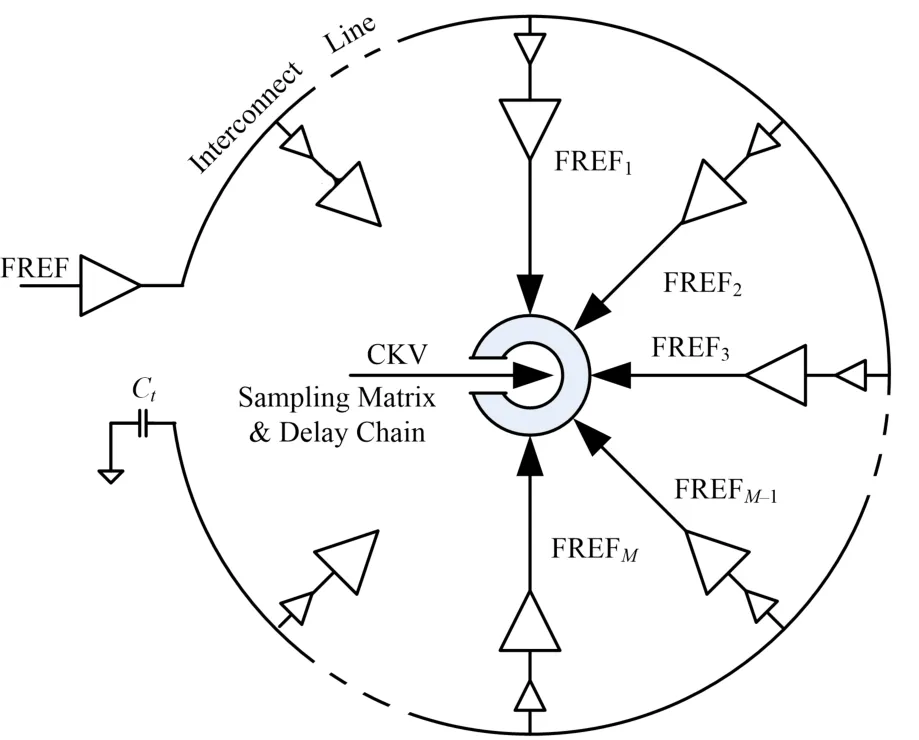

2 基于互连线插值TDC系统架构

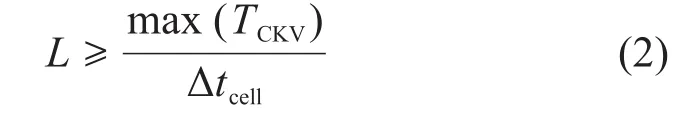

为了方便对基于互连线插值TDC系统工作原理的介绍。首先假设,互连线可以提供数皮秒量级的等延时。基于互连线插值TDC系统由三部分构成:延时链、采样矩阵和提供等延时的互连线系统,如图2所示。延时链采用传统的延时链,即延时单元由两个反相器构成,其分辨率为Δtcell;延时单元的长度为L,并满足式(2):

式中:TCKV为时钟CKV的周期。这是为了保证被测信号在延时链中形成的矢量能包含一个完整的CKV周期的信息。

图2 基于互连线插值的TDCFig.2 Diagram of TDC based on interconnect interpolation

采样矩阵是规模为L×M的D触发器构成的,每行使用同一个时钟,且每行中D触发器的输入接在延时链的对应位置上。互连线系统是由负载电容和互连线构成,参考时钟FREF经过互连线,形成M个时钟。而且,相邻时钟之间的延时是相等的Δtline,且有:

式中:Δtline为TDC的分辨率;而N表示通过插值可以将分辨率提高的倍数。为了可以通过采样矩阵的中的数值对N进行估计,在参考时钟FREF的延时链上需要出现两次上升/下降沿的变化,因此M需满足以下不等式:

式(5)可以确保上升沿和下降沿从第一次采样到最后一次被采样,至少经历过一个完整的延时单元。这样做的目的在于可以通过采样矩阵输出的矢量对参数N进行估计,以弥补因为电源电压、工艺偏差等因素导致N的偏差。下面将以一个实例来说明这种结构TDC的工作原理。

图3是一个基于插值TDC的例子,其中L=10、N=4且M=9。输出是一个10×9的矩阵。假设CKV是一个占空比为50%的信号,从行向量Q(i)可知,半周期有时为三个“1”,有时为两个“1”,导致这种现象的原因就是CKV的半周期2Δtcell< Tv< 3Δtcell,如果不进行插值,那么TDC测量分辨率为Δtcell。对时钟FREF进行延时后可采样获得一个矩阵,时间差测量是不仅可以利用每行本身的信息,还可以利用每行在纵向变化所表示的信息。

图3 互连线插值的TDC的工作原理Fig.3 The principle of interconnect interpolation in TDC

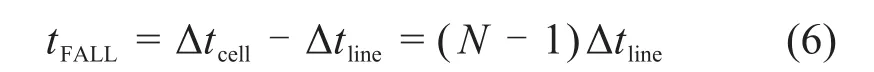

首先分析下降沿从第一次采样到最后一次采样,在延时链路中的整个行进过程。从Q(1)可知FREF1的上升沿离CKV最近的下降沿时间小于“1”个Δtcell。经过时间Δtline后,从Q(2)可以看出,第一个延时单元的输出由“1”变为“0”。这表明此时下降沿已经完全通过了第一个延时单元进入第二个延时单元,而且可推断下降沿距FREF1的上升沿时间为:

从Q(5)和Q(6)的数据可知,下降沿在FREF6上升沿时刻,已经完全通过了第二个延时单元。结合Q(1)和Q(2)的数据还可以知道,下降沿在第二个延时单元的时间为4Δtline,于是可以估算出N=4。最终由式(6)可知,下降沿距FREF1的上升沿时间:

接下来用同样的分析方法由QL×M可以得到CKV上升沿和FREF1上升沿的时间差:

于是将式(7)和(8)相减后取绝对值,可得CKV的半周期为:

式(10)所得结果和图3相符。通过插值的方式可以将TDC的分辨率提高为Δtline,是不插值的N倍。

在上面的例子中,为了讲述方便N是个整数,而在实际使用中N可以不是整数。这主要有两方面原因:一方面,在实际电路中由于没有使用类似DLL的校准的机制,所以不能保证Δtcell是Δtline的整数倍;另一方面,TDC系统在使用过程中,N也会因为电源电压、温度等因素发生变化。本文提出的基于互连线差值的TDC考虑了N值的变化。当TDC满足不等式(5),由前面例子可知,我们可以从已经获得的QL×M数据去估算出N。此外,还可以借鉴文献[8]的方法对N进行长时间平均以实现更精确的估计。

3 基于等长互连线段实现等延时的方法

采用互连线进行插值的前提是通过互连线能实现相邻节点间延时差相等,即实现等延时。为此,在本节将对互连线进行分析,具体探讨如何利用互连线实现等延时的方法。忽略互连线上引出时钟时负载对互连线特性的影响,那么互连线系统就可以简化为图4所示。

图4中长度l和其对应的delay(l)是一个单调递增函数,但服从非常复杂的函数关系[10],一般不是线性关系。理论上,利用非线性的互连线函数关系构建等延时也是可行的。但这会带来两个问题,一是等延时对应的相邻互连线长度Δli之间互不相同,这加大了版图设计难度;二是不同长度的Δli会增加工艺偏差对延时的影响。为了解决上述问题,本文提出了在图4所示的架构中寻找线性区域,在线性区域来构建等延时的方法。所谓互连线的线性区,满足或近似满足延时的增加和长度l的增加成线性关系,即延时对长度l求导为常数或接近常数。在该区域造等延时最大好处是:实现等延时的线长Δli是相等的。

图4所示的互连线系统看似简单,但是对其延时的分析却是十分复杂的,通常很难得到延时和线长的闭合公式。在文献[10]对互连线延时特性进行了深入的研究,提出了一种基于RLC延时的估算模型。本文利用这个模型对互连线进行仿真分析后,发现对于一个长度为Lt的互连线在不同的负载下,l和线上的延时有以下关系:1)当电容负载较大时,不存在线性区,如图5(a)所示;2)当电容负载较小时,有很窄的线性区,如图5(b)所示;3)只有当电容负载合适时,能实现相对较宽的线性区,如图5(c)所示。因此,对于一个互连线可以通过选择合适的负载,增加线性区的范围。在线性区,可以用等长度的间隔来实现相等的延时。

图4 电容负载的互连线系统Fig.4 Interconnect line system with capacitive load

图5 不同负载下互连线延时特性 (a)负载较大,(b)负载较小,(c)负载合适Fig.5 Delay characteristics of interconnect lines under different loads(a)Too large load,(b)Too small load,(c)Appropriate load

4 环形结构互连线插值TDC版图设计方案

图2是基于互连线插值的TDC基本结构,电路实现时仍有三个主要问题需要解决:1)D触发器阵列的时钟端口均接在互连线上,该端口上的负载对互连线延时特性会产生影响;2)时钟CKV利用延时链路形成的一组信号,经过不同长度的互连线后形成CKVi[1:L]分别输出给不同的D触发器组Di,由于不同的CKVi[1:L]对应的互连线长度不同因此延时也有所不同,进而引入TDC测量的系统误差;3)互连线本身尺寸较大增加了版图布局对互连线的延时特性的影响。

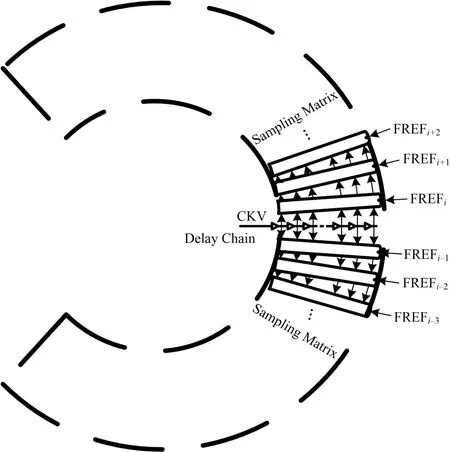

为了解决上述问题,本文提出一种环形的版图设计方案,如图6所示。整个布局由外环电路、环间电路和内环电路三部分组成。外环电路的主要功能是产生等间隔延时,由一段接近环的弧形互连线、FREF信号的驱动放大器和端接负载Ct等三部分组成。为了提高信号的驱动能力,需选择大尺寸的反相器来实现FREF的驱动放大。为了减少外围电路的影响,互连线采用具有上下两个地平面的带状线结构实现。沿互连线打上过孔以屏蔽外部电路引入的串扰。环间电路的主要功能是从互连线上引出等间隔的FREFi信号,放大后沿径向输出给内环的采样网络。这种沿径向传输的方式可以减少因布局引入的FREFi间额外的延时偏差。此外,为了减小buffer的负载对互连线的影响,设计中将采用两种方法:1)均匀地将互连线分成多段并都接上buffer,而实际供给采样矩阵的FREF信号仅是那些处于线性区的信号;2)采用两级反相器实现buffer的功能,其中第一级使用最小尺寸的反相器以减少输入负载,而第二级使用相对较大尺寸的反相器以增强对L个D触发器的驱动能力。内环电路的主要功能是在FREFi信号作为时钟的条件下对经过延时链后的CKV信号进行采样,该部分电路主要由采样矩阵和延时电路两部构成,布局如图7所示。在环形结构中,采样矩阵是在面积较小的内环中实现,D触发器组Di之间的物理位置距离相对较小,因此因位置不同引入CKVi[1:L]间的延时偏差也较小。

图6 环形结构的TDCFig.6 TDC with ring structure

图7 环形TDC的内环布局Fig.7 Internal ring structure of TDC

5 仿真结果

本文采用SMIC0.18工艺库实现TDC中的各电路模块,采用Verilog-A语言实现采样矩阵相关数据的处理,以对本文提出设计方法进行验证。仿真验证使用的仿真工具为HSPICE2016,使用的计算机参数如下:主频为3 GHz,内存为8 G,Win10操作系统。

5.1 仿真1

为证明图5所示不同负载下互连线延时的趋势,对长度为1 mm的互连线在不同电容负载下进行仿真。每隔0.1 mm接一个由两级反相器构成的buffer,并将延时信号整形后输出。buffer中的第一级反相器使用的是SMIC0.18工艺库中最小尺寸的标准反相器,其输入端接电容为4.6 fF。电路基本结构如图8所示。其中,互连线上的分布参数:单位长度上的电阻r=600 kΩ∙m-1,单位长度上的电感lin=246 nH∙m-1,单位长度上的电容c=176 pF∙m-1。

图8 仿真1的互连系统Fig.8 Interconnect line system of simulation 1

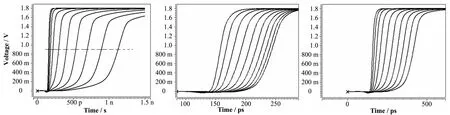

图9(a)是Ct=0.8 pF时的仿真结果,可以看出,由于端接负载太大,随着l的增加,单位长度的延时越来越大;图9(b)是Ct=0.1 pF时的仿真结果,可见,由于端接负载太小,在互连线中部区域有一个很窄的线性区;图9(c)是Ct=0.3 pF时的仿真结果,从node 7到node 8、node 8到 node 9以及 node 9到node 10的延时均为34 ps,这表明从0.7 mm处到负载Ct这个区域,延时和l的增加基本上呈现线性关系。因此,可以得出这样一个结论:集成电路中互连线通过合理设计,可以得到一个较宽的线性区,并且在这个区域中可以用等长的互连线实现相等的时间延时。

5.2 仿真2

下面将利用长度为1 mm的互连线,实现数皮秒的等间隔延时。将互连线均匀分为40段,接一个由两级反相器构成的buffer,并将延时信号整形后输出。buffer中的第一级反相器使用的是SMIC0.18工艺库中最小尺寸的标准反相器,其输入负载电容为4.6 fF。电路基本结构如图10所示。其中,互连线上的分布参数:单位长度上的电阻r=300 kΩ∙m-1,单位长度上的电感lin=246 nH∙m-1,单位长度上的电容c=176 pF∙m-1。负载Ct=0.4 pF。由式(5)可知,如果N=4的话,M=9才能满足要求,因此仿真2将输出9个等间隔的时钟。

从图11可知,互连线系统从节点16到25处于线性区,因此从节点16开始,引出9个信号作为采样矩阵的时钟,时钟的波形如图12所示。这些时钟的平均间隔5.35 ps,最大偏差0.35 ps。因此在互连线线性区,通过合理选择参数等长线可以实现数皮秒的等延时。文献[11]采用0.13 μm CMOS工艺实现的时间精度为57 ps。

图9 不同负载下互连线延时的仿真结果 (a)负载较大,(b)负载较小,(c)负载合适Fig.9 The simulation results of interconnect delay with different loads(a)Too large load,0.8pf,(b)Too small load,0.1 pf,(c)Appropriate load,0.3 pf

图10 仿真2的互连系统Fig.10 Interconnect line system of simulation 2

图11 互连线不同节点上的延时Fig.11 Delay on different nodes of the interconnect

图12 互连线输出的时钟信号上升沿Fig.12 Rising edge of clock signal output from different nodes of the interconnect

6 结语

为了提升TDC的测量分辨率,本文提出了一种对工艺偏差不敏感的互连线插值的TDC结构,并给出了环形结构的版图布局方案。在该结构中,对采样时钟FREF进行延时形成一系列等延时间隔的时钟,利用这些时钟对延时链中的矢量进行采样。然后通过对获得数据分析,得出需要的时间信息。本文采用Verilog-A语言和SMIC0.18工艺库在HSPICE中对上述算法进行了仿真实验。实验结果表明使用该方法即使是在0.18 μm CMOS工艺下也能将TDC的分辨率提高至皮秒级。