一种采用时域比较器的低功耗逐次逼近型模数转换器的设计

张蕾, 杨晨晨, 王兴华

(北京理工大学 信息与电子学院,北京 100081)

随着无线传感器网络、可穿戴设备、医学可植入器件等新兴、低能耗器件系统的应用需求越来越迫切[1-4],对系统中模数转换器等核心器件提出了更高的要求. 相比于快闪型(flash)、流水线型(pipeline)和∑-Δ型(Sigma-delta)等类型的模数转换器,逐次逼近型模数转换器结构简单、模拟电路少、功耗低、尺寸小、输出数据不存在流水延时等优点,而且其制造工艺与现代数字CMOS工艺的兼容性好,易于在较低的工艺成本下实现等特性,得到了广泛的应用[5-8]. 近些年,降低整个SAR ADC系统功耗的新型电路结构不断涌现. 例如,通过优化开关电容阵列的电平转换能效[9];采用分段式电容减小电容阵列的总电容,进而降低功耗[10];基于信号活跃性的采用低位开始的逐次逼近方法[11];采用低功耗的动态比较器[12];半动态SAR控制逻辑[13]等等电路.

本文提出了一种适用于便携可穿戴设备的10位低功耗SAR ADC. 电路采用时域比较器有效降低了整体电路的静态功耗,减小了共模偏移对比较器的影响. 同时,采用分段式电容阵列以及部分单调式电容阵列电压转换方式,有效减小整体电路的总电容和功耗.

1 SAR ADC整体结构

本文设计的基于时域比较器的SAR ADC结构如图1所示,主要模块包括栅压自举开关、时域比较器、数模转换电路(DAC)、时钟产生电路和逻辑控制单元. 与传统电压模比较器不同,本文采用时域比较器,将不同的输入电压信号转化为对电容的放电速率的不同,进而转换为时间信号,通过鉴相器检测出有不同输入信号产生的延时差异. DAC电路采用分段式二进制加权的电容阵结构,大大降低了所需单位电容的数目. 实现10位的转换精度,传统的并行二进制加权电容阵列结构需要1 024个单位电容,本文通过分段式电容阵列降低总电容,进而降低整个电容阵列功耗,如图1所示,电容阵列分为高5位与低5位DAC,中间通过桥接电容Cs连接,整体只需128个单位电容即可实现10位DAC的功能,单位电容为200 fF. 整体电路采用全差分结构有效抑制了衬底和电源噪声,提高了电路精度.

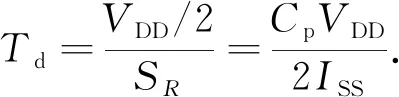

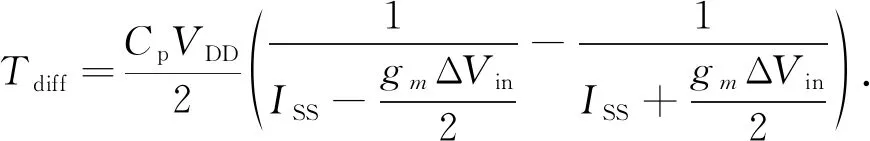

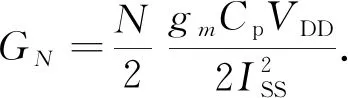

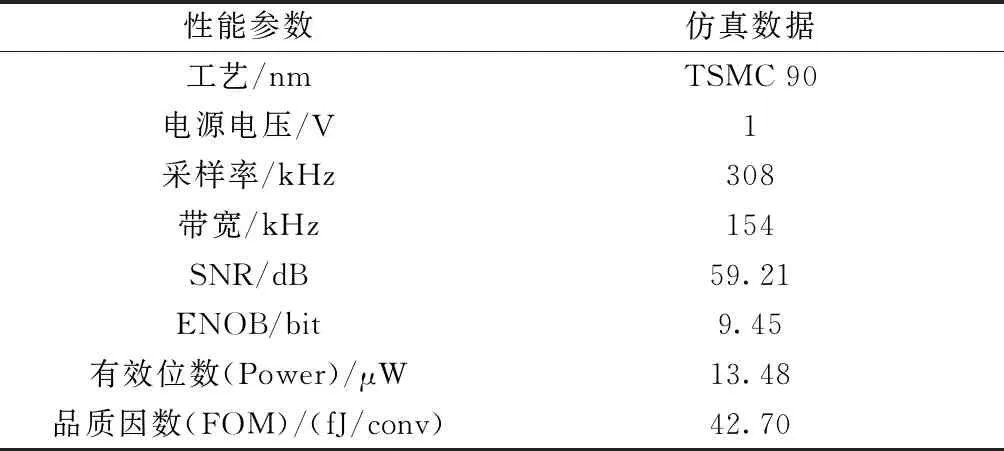

电路在初始状态最高位电容的下极板接地电位,其他位电容的下极板接参考电压电位VREF. 栅压自举开关对输入信号进行采样并将采样后的电平保持在DAC的上级板,比较器对采样信号进行第一次比较,如果Vp 在SAR ADC中,采样保持电路对输入信号进行采样,其性能对整体信噪比、线性度和直流失调等有重要影响. 在采样阶段,开关导通电阻和采样电容构成了一个RC网络,限制了带宽. 自举开关的栅-源电压为一定值,导通电阻恒定,不随输入信号的变化而变化,极大地提高了开关地线性度,改善了采样保持电路地性能. 传统自举开关采用电荷泵的方式,实现开关管的高栅压,本文采用改进型自举开关,如图2所示,减小了大电容的使用,大大减少了开关的功耗,同时有效节省了芯片面积. 时钟信号CLK为低电平时,M3和M4构成的反相器输出高电平使M6导通,电容C下极板接地,M8和M9栅极为高电平导通,M8漏极接低电平,M5导通,电容C被充电到VDD,M1导通,故M7栅极接高电平而截止,开关M11处于断开状态;当时钟信号为高电平时,M6和M9截止,M2导通,M7栅极接在M6漏极,即M7的栅源电压为-VDD,管子导通,其漏电压为高电平,M10导通,开关管M11的栅电压升至VDD+Vin,开关处于导通状态,栅源电压为VDD,实现栅压自举功能. 本文提出的时域比较器(time domain comparator, TDC),由两个电压控制延时线(voltage control delay line, VCDL)和一个鉴相器(phase detector, PD)组成,如图3所示. 电压控制延时线相当于比较器的预放大电路,由多级电压控制型延时单元组成,如图4所示. 输入信号inn和inp控制对寄生电容的充放电时间,从而控制从输入时钟到输出时钟的延时时间,对于NMOS控制的延时级,控制电压inp越大,输出节点的放电电流越大,延时时间越小;对于PMOS控制的延时级,控制电压inn越小,输出节点的充电电流越大,延时时间越小. 对任意一个电压控制延时线来说,inp越大,inn越小,由比较器时钟CLK到输出OUT的延时时间越小,因此差分输入对两个延时线的延时时间影响是相反的,两个延时线的输出IN1和IN2之间存在着相位差. 对于每一级延时电路来说,假设其压摆率恒定,如式(1)所示. SR=ISS/Cp. (1) 式中:ISS为充放电电流;Cp为每一级输出节点的寄生电容,则该级的延时时间Td为 (2) 由两级延时电路构成的延时线的延时与差分输入信号ΔVin=Vinp-Vinn有关,可表示为 (3) 化简为 (4) 其中gm为输入管工作时的跨导,因此由N级延时电路构成的延时线的电压-时间增益可表示为 (5) 从式(5)看出,可以通过增加级数或提高寄生电容的方式增大电压控制延时串的电压-时间增益. 延时电路的功耗主要包括由漏电流引起的静态功耗和电路翻转时的动态功耗,其中对寄生电容进行充放电造成的动态功耗占整体电路的主要部分,因此N级电压控制延时电路的总功耗可以表示为 (6) 基于RS锁存器结构的鉴相器鉴别IN1和IN2间的相位差,得出比较结果. 初始状态IN1和IN2都为0,L1和L2均被拉至VDD,输出OUT保持之前的状态,当Vinp>Vinn时,IN1的延时时间小于IN2的延时时间,即IN1超前IN2上升至高电平,L1先于L2被拉到底,导致L2受正反馈作用变为VDD,OUT输出为1;反之当Vinp 初始状态IN1和IN2都为0,L1和L2均被拉至VDD,输出OUT保持之前的状态,当Vinp>Vinn时,IN1的延时时间小于IN2的延时时间,即IN1超前IN2上升至高电平,L1先于L2被拉到底,导致L2受正反馈作用变为VDD,OUT输出为1;反之当Vinp 控制逻辑单元根据比较器输出结果,控制DAC电容阵列中每一位电容电压的切换,实现其输出电压与输入信号的逐次逼近. 传统的单调式开关电容切换是在每一位均采用下拉模块,即转换时将下极板由VREF切换至地,因此共模逐渐从Vcm下降至接近0的电位,共模偏移非常大. 部分单调切换策略要求上拉和下拉模块同时存在,最高位使用上拉模块,剩下9位使用下拉模块,这样最终共模电平停留在Vcm附近. 上拉模块和下拉模块电路结构如图6所示. 当时钟为低时,与非门输出为“1”,置位端Ci接地;当时钟上升沿到来时, 由触发器将结果输送到反相器输入端,如果比较结果为“1”,经过反相器变为“0”, Ci保持不变,若比较结果为“0”,经过反相器变为“1”,与非门输出“0”,置位端Ci接VREF,完成上拉动作. 下拉单元功能与上拉单元功能相反,其在比较结果较大的一端向下置位,即时钟为低时,与门输出为“0”,置位端Ci保持输出VREF;当时钟上升沿到来时,若比较结果为“0”,即该位值较小,与门输出“0”,置位端保持VREF不变,当比较结果为“1”时,与门输出变为“1”,置位端Ci将接地,完成下拉动作. 本文采用同步控制时序,完成一次转换过程需要12个时钟(CLK)周期,其中2个CLK为采样时钟周期(CLKS),10个时钟周期完成电压转换,比较时钟(CLKC)由CLK及延时单元产生. 采用部分单调式开关策略,电容阵列需要切换9次,因此只需9个控制切换电容阵的开关以及控制开关的时钟CLK1~CLK9,控制时序如图7所示. 在Cadence仿真软件环境下,采用TSMC90工艺,对SAR ADC整体电路并进行仿真. 在电源电压为1 V,参考电压VREF为1 V,输入信号频率为153.9 kHz,幅度为0.9 V,采样率308 kHz,有效位数为9.45 bit,具体各项性能指标,如表1所示. 输入信号频率从9~154 kHz频率下ADC的性能曲线,如图8所示. 整体SAR ADC的版图,如图9所示. 表1 SAR ADC性能总结Tab.1 Performance summary of proposed SAR ADC 论文设计了一种适用于低功耗系统要求的SAR ADC,采用时域比较器替代传统比较器的实现方式,减小了共模偏移对比较器的影响和静态功耗,具有较强的实用价值. 同时结合SAR ADC的结构特点,采用部分单调式的电容阵列电压转换过程,进一步有效减小电容阵列总电容及其功耗. 仿真验证结果表明,该结构可以在保证10 bit转换精度的要求下有效降低整体电路的功耗,有着重要的实际意义.2 电路设计

2.1 栅压自举开关

2.2 时域比较器

2.3 控制逻辑单元及时序

3 仿真结果与分析

4 结 论