GaN 基LED 中V 形坑缺陷的研究进展

刘青明,尚 林,邢茹萍,侯艳艳,张 帅,黄佳瑶,马淑芳,许并社,2

(1.陕西科技大学前沿科学与技术转移研究院 材料原子·分子科学研究所,陕西 西安 710021)

(2.太原理工大学 新材料界面科学与工程教育部重点实验室,山西 太原 030024)

1 前言

氮化镓(GaN)作为第三代宽禁带直接带隙半导体,具有耐高温高压、抗腐蚀、高电子饱和漂移速率、结构稳定等优点,被广泛应用于发光二极管(LED)、激光二极管(LD)、光探测器(PD)、场效应晶体管(FET)等光电子和微电子器件中,极大地推动了半导体照明、移动通讯、高分辨显示、深紫外探测等领域的发展[1-8]。近年来,GaN 基光电器件发展迅速,发光波段逐渐由蓝光向高铝(Al)含量的深紫外和高铟(In)含量的黄光乃至红光波段发展[9-11];类型由发光二极管向外延结构更复杂的边发射、垂直腔发射激光器发展[12,13];应用领域由照明源向高分辨显示、可见光通讯、杀菌消毒医疗技术等发展。然而,GaN 基LED 中依然存在诸多悬而未决的基础性问题,如V 形坑缺陷、极化、高效p 型掺杂、光提取效率等问题[14-17]。异质衬底上生长的GaN 基LED 外延层的位错密度高达108cm2,而内量子效率却超过了50%,这与传统的砷化镓(GaAs)基光电器件显著不同。GaN 基LED 高位错密度下高发光效率的物理机制一般可通过局域态屏蔽位错理论和V 形坑屏蔽位错理论进行解释[18-21]。前者认为在外延InGaN/GaN 多量子阱时,由于In 掺杂不均匀而形成富In 区,因此注入有源区的载流子被限制在势能的谷底,避免被位错处的非辐射复合中心捕获,从而使LED 具有较高的发光效率;后者认为外延InGaN/GaN多量子阱时,穿透位错处会形成具有侧壁量子阱的V 形坑,侧壁量子阱的In 含量较低、禁带宽度较大、势垒较高,此高势垒可阻挡载流子被非辐射复合中心捕获。

自2005 年Hangleiter 等[20]提出V 形坑屏蔽位错理论以来,V 形坑中侧壁量子阱的特殊载流子调控机制引起了科研人员的重视。特别是随着外延技术和表征手段的发展,近年来有关V 形坑及其附近区域量子阱的载流子传输机制和发光特性、通过V 形坑调控器件光电性能的相关研究逐渐丰富起来。基于此,本文从V 形坑形成机理、V 形坑附近区域量子阱的发光特性、V 形坑对LED电学特性的影响和通过V 形坑调控LED 光电性能4 个方面进行综述。

2 V 形坑的形成机制

本文所介绍的V 形坑存在于具有纤锌矿结构的GaN基LED 的多量子阱中,形状为倒金字塔状,有6 个侧面,每个侧面为面,侧面与c面的夹角均为62°,其结构示意图如图1a 所示[22]。图1b 为高分辨电子透射显微镜(HRTEM)下观察到的V 形坑形貌照片[20],V 形坑中侧壁量子阱的周期数与c面量子阱的相同,厚度约为c面量子阱的1/3,且其厚度会因生长条件的不同而产生波动。而且,在后续生长高温p-GaN 时,V 形坑可以被填平。由利用三维原子探针获得的V 形坑中In 原子和Ga 原子的成分分布图(图1c)可以看出,侧壁量子阱中In 原子层的厚度较薄且分布不均匀[23]。V 形坑中侧壁量子阱屏蔽位错处非辐射复合中心的示意图如图1d 所示,由于V 形坑一般在穿透位错处形成,且侧壁量子阱的In 含量较低,因此在穿透位错周围形成了较高的势垒,此高势垒可以阻挡载流子被位错处非辐射复合中心捕获[20]。

关于V 形坑的形成机制多数观点认为,生长InGaN/GaN 多量子阱时,量子阱/垒间的晶格失配使c面量子阱内存在较大应力,以及其较低的生长温度使量子阱表面原子迁移率降低,从而形成了V 形坑。但是,V 形坑的主要形成原因是面内应力还是原子迁移率,亦或是两者共同作用,尚存在争议。

图1 V 形坑的结构示意图(a)[22];InGaN/GaN 多量子阱(MQWs)中V形坑的HRTEM 照片(b)[20];V 形坑中Ga,In 原子的成分分布图(c)[23];V 形坑屏蔽位错处非辐射复合中心的示意图(d)[20]Fig.1 Structural schematic diagram of V-shaped pit (a)[22];HRTEM image of a V-shaped pit in InGaN/GaN MQWs (b)[20];composition distribution map of In and Ga in a V-shaped pit (c)[23];schematic diagram of V-shaped pits screening non-radiative composite center of dislocations (d)[20]

Mahanty 等[24]通过固定量子阱总厚度,改变InGaN 阱层和GaN 垒层的厚度来研究V 形坑的产生机制。结果表明,V 形坑的出现与多量子阱中InGaN 的总厚度有关,固定In 含量为12.6%(原子数百分数,下同),当InGaN 总厚度超过临界厚度25 nm 时,V 形坑开始出现,且随着InGaN 总厚度的增加,V 形坑的尺寸也逐渐增加。然而,在InGaN 的总厚度不超过临界厚度的情况下,适当降低阱层的生长温度,V 形坑也并未出现。因此,他们认为V 形坑的出现主要是由InGaN 和GaN 间晶格失配所产生的应力导致的,当InGaN 总厚度超过临界厚度时,量子阱中的面内应力通过表面粗糙化的方式进行释放,即形成V 形坑。Lin 等[25]的结果也支持上述理论,通过增加In 含量来增加多量子阱中的应力,结果表明V 形坑密度随In 含量的增加而增加,并认为InGaN 与GaN 间失配应力的增加是V 形坑密度增加的主要原因。Sharma 等[26]认为低温下较低的Ga 原子迁移率是形成V 形坑的主要原因。他们在n-GaN 上依次生长了5 个周期的InGaN/GaN 多量子阱,在多量子阱中可以清晰地观察到V 形坑。然而,后续生长高温p-GaN 时,V 形坑逐渐被p-GaN 填平。他们认为在低温生长多量子阱时,(0001)面Ga 原子的迁移能力较弱,破坏了GaN 的二维台阶流生长模式,因此形成了V 形坑;而后续生长高温p-GaN 时,Ga 原子迁移率增加,又将V形坑填平。Kim 等[27]则认为InGaN 和GaN 间的失配应力和原子迁移率降低都是V 形坑形成的主要原因。他们在不改变阱垒厚度比的条件下,通过增加量子阱的In 含量和周期厚度来研究V 形坑的产生机制。结果发现,当In 含量为13%、多量子阱的周期厚度为5 nm 时,V 形坑未出现;而当In 含量超过20%、多量子阱周期厚度大于8.4 nm 时,V 形坑出现了。这是由于较高的In 含量和较大的周期厚度使量子阱中的应力增加。另外,他们还通过对比分子束外延生长(MBE)和金属有机气相外延生长(MOCVD)两种方法来研究V 形坑的形成机制。结果表明,使用MBE 技术生长的InGaN 单层在生长温度更低、In 含量更高、厚度更厚(温度为500~600 ℃,In 含量约为20%,厚度约为150 nm)的情况下,并没有出现V 形坑,而以MOCVD 技术生长的样品在温度更高、In 含量更低、厚度更薄(温度约为700 ℃,In 含量约为6%,厚度约为100 nm)的条件下,却形成了V 形坑。这可能归因于采用MBE 技术生长样品时,通过射频等离子体使NH3分解,活性N 原子的原子迁移率更高,抑制了V 形坑的出现。

3 V 形坑附近材料的发光特性

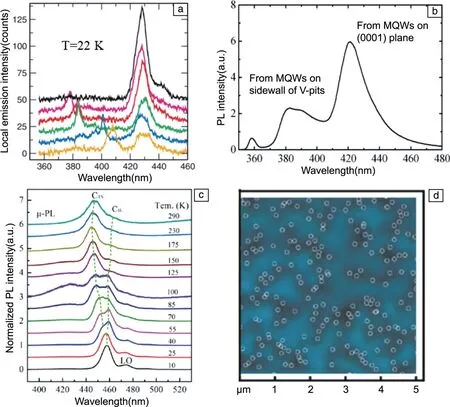

图2 多量子阱(MQWs)的光致发光(PL)行为:(a)穿透位错附近不同纳米尺度区域的低温发射光谱[28];(b)V 形坑中侧壁和c 面量子阱(QWs)的PL 图谱[29];(c)不同温度下侧壁和c 面量子阱的PL 图谱[30];(d)MQWs 阱的PL 显微照片[31]Fig.2 Photoluminescence (PL) behaviors of MQWs:(a) low-temperature emission spectrum of different nm-sized areas close to threading dislocations[28];(b) PL spectra of sidewall and c-plane QWs in V-shaped pits[29];(c) PL spectrum of sidewall and c-plane QWs under different temperatures[30];(d) PL microscopy image of MQWs[31]

Hangleiter 等[28]在22 K 下测试不同V 形坑中侧壁量子阱的发光峰,如图2a 所示侧壁量子阱的峰值波长较c面量子阱蓝移20~50 nm 不等。Hao 等[29]也同样测得了侧壁和c面量子阱的发光峰(图2b)。Xu 等[30]利用微区变温光致发光(PL)测试,研究了V 形坑及其附近c面量子阱在不同温度下的发光特性。结果表明,随着温度的升高,短波长的峰占主导地位且峰位出现蓝移现象,如图2c 所示。这归因于在V 形坑附近的c面量子阱中,载流子迁移率随温度的升高而增加,使得更高比例的载流子在较高能量处发生跃迁辐射,在此过程中,限制在侧壁量子阱中的载流子获得了足够的能量从而传输到V 形坑附近的c面量子阱中。Meyer 等[31]通过微区光致发光扫描系统(PL mapping)研究了V 形坑缺陷附近区域量子阱的发光特性,结果表明V 形坑附近的PL 强度明显较弱,且暗区(V 形坑)附近发光峰的能量比c面量子阱高数个meV,这说明V 形坑中的侧壁量子阱显著影响周围c面量子阱的发光性能(图2d)。

还有一些研究同样证实了V 形坑侧壁量子阱对其附近c面量子阱的发光性能产生了重要影响[32-35]。归纳起来,V 形坑附近c面量子阱的In 含量和厚度有一定的波动,与远离V 形坑的c面量子阱相比,其应力较小,缓解了量子限制斯塔克效应,使其发光峰蓝移。V 形坑中侧壁量子阱的In 含量较低,其势垒高度大于c面量子阱的,故侧壁量子阱能够在穿透位错周围形成高势垒,阻挡载流子被穿透位错处的非辐射复合中心所捕获。

4 V 形坑对LED 电学特性的影响

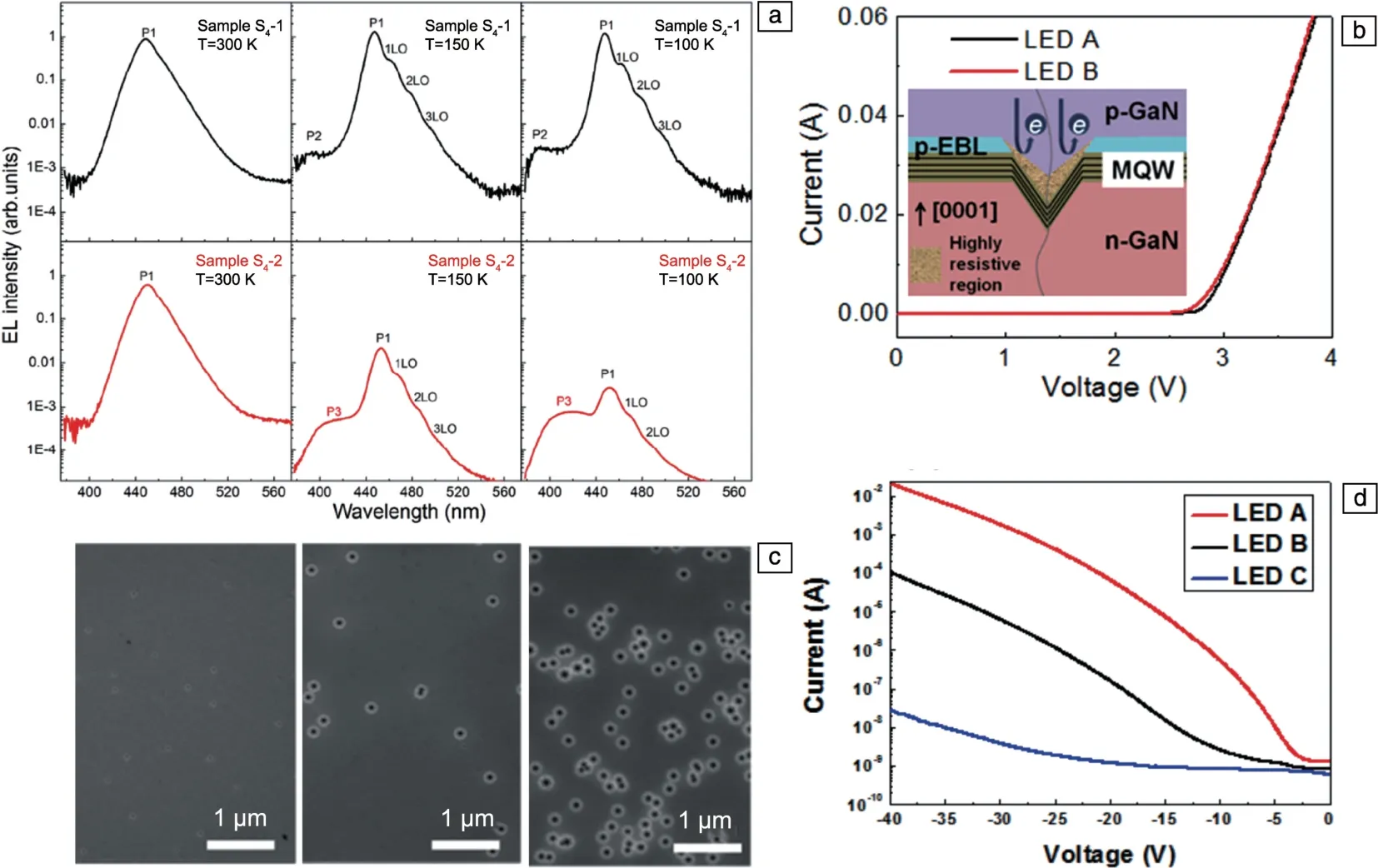

Wu 等[36]在电致发光(EL)条件下,通过改变p-AlGaN电子阻挡层中Mg 掺杂水平来研究V 形坑对空穴注入的影响机制。随着温度降低,无掺杂样品的侧壁量子阱发光峰P3 较强,如图3a 中下方的EL 图谱所示。不同掺杂水平的样品,其等效电阻不同,导致注入侧壁量子阱的空穴数量不同,因此侧壁量子阱的发光强度不同。Han 等[37]发现Mg 的掺杂存在各向异性,与c面相比,侧壁中Mg 的掺杂量很低。因此,生长在V 形坑中的p-AlGaN 电子阻挡层以及部分生长在侧壁上的p-GaN 层的电阻较高,天然阻挡了载流子向位错处非辐射复合中心靠近,对位错在电学上进行了屏蔽,如图3b 所示。Kim 等[38]通过调节低温GaN 的厚度来改变V 形坑尺寸,并研究了V 形坑尺寸对器件反向漏电的影响。图3c 和3d 分别为生长完多量子阱结构后LED 的SEM 照片和反向漏电测试结果。结果表明,V 形坑尺寸的增加有助于降低LED 的反向漏电,这意味着器件的屏蔽效应更优。他们团队利用Poole-Frenkel 模型对产生这一结果的物理机制进行解释:温度在250 K 以上时,外加电场的存在使量子阱中由缺陷引起的深能级电子变为自由电子所需的能量降低,深能级电子更易变为自由电子,故器件的反向漏电电流增加;但是,随着V 形坑尺寸增加,深能级电子变为自由电子所需克服的势垒高度显著增大,即深能级电子变成自由电子所需的能量更大,故器件的反向漏电流减小。

图3 V 形坑对LED 电学特性的影响:(a)不同Mg 掺杂量下样品的变温电致发光(EL)图谱[36];(b)不同Mg 掺杂量下LED 的I-V 特性曲线(插图为器件B 中V 形坑周围形成高电阻区域的示意图)[37];(c)不同尺寸V 形坑的SEM 照片[38];(d)具有不同尺寸V形坑LED 的I-V 特征曲线[38]Fig.3 Effects of V-shaped pits on electrical characteristics of LED:(a) temperature-dependence EL spectrum of samples with different Mg doping concentrations[36];(b) I-V characteristic curves of LEDs with different Mg doping concerntrations (The insetting is the schematic diagram of highly resistive region around V-shaped pits in LED B)[37];(c) SEM images of V-shaped pits with different sizes[38];(d) I-V characteristics curves of LEDs with different-size V-shaped pits[38]

5 通过优化V 形坑调控LED 光电性能

Okada 等[39]通过改变超晶格周期数来调控V 形坑尺寸,研究V 形坑尺寸对器件内量子效率(IQE)的影响。在不改变量子阱周期数(4 个周期)和厚度的前提下,分别生长超晶格周期为0,5,10,20 的样品。由原子力显微镜照片(图4a)可知,随着超晶格周期的增加,V 形坑尺寸逐渐从42.9 增加至177.6 nm,器件的IQE 先增加后减小。当超晶格周期为10 时,器件的IQE 最高,此时V形坑的尺寸为96.2 nm。Okada 等认为在一定范围内增加V 形坑尺寸,侧壁量子阱的势垒高度增加,有助于提高侧壁量子阱对位错的屏蔽效应;而当其继续增加,由于侧壁量子阱的均一性变差和c面量子阱发光面积减小,从而导致器件IQE 的降低。Xu 等[40]通过控制中高温GaN 插入层厚度来调控V 形坑尺寸,研究了V 形坑尺寸对器件EL 强度的影响机制。随着V 形坑尺寸从70~110 增加至110~150 nm,器件的光输出功率增加了10%(图4b)。分析认为,对于空穴浓度较低的GaN 基LED 而言,随着V 形坑尺寸的增加,空穴注入面积增加的同时注入深度也得到提高。V 形坑尺寸的增加,使由侧壁量子阱注入至靠近n-GaNc面量子阱中的空穴数目增多,使得空穴浓度分布更均匀,注入效率增加,提高了LED 的光电性能。Tsai 等[41]通过调控p-GaN 的生长温度研究了V 形坑对器件光提取效率和抗静电性能的影响(图4c)。他们分别通过先高温后低温生长p-GaN、低温下生长p-GaN 和高温下生长p-GaN 的思路制备LED。前两种方法制备的样品表面均存在大量V 形坑,而高温下生长的样品表面平整,光提取效率最低。先高温后低温的方法可以兼顾光提取效率和抗静电性能。Li 等[42]通过三维数值模拟研究了电注入下V 形坑附近载流子的传输行为,由正向偏压下V 形坑附近区域的空穴电流传输矢量图(图4d)可以看出,空穴可以通过侧壁量子阱注入到c面量子阱。这是由于侧壁量子阱的极化势垒低于c面量子阱,注入到V 形坑区域的空穴可以从侧壁量子阱流向c面量子阱。因此,V 形坑给空穴提供了额外的传输通道,使其除了从c面量子阱正上方注入,还能从侧壁量子阱流向c面量子阱,从而使各c面量子阱的空穴分布更加均匀。

6 结语

图4 V 形坑调控器件的光电性能:(a)不同超晶格周期下MQWs 表面V 形坑的原子力显微镜(AFM)照片[39];(b)具有不同尺寸V 形坑的LED 的外量子效率(EQE)及光输出功率随注入电流的变化图(样品A,B 的V 形坑尺寸分别为70~110 和110~150 nm)[40];(c)不同工艺下制备的LED 的光输出功率和抗静电性能[41];(d)V 形坑中空穴传输示意图[42]Fig.4 Optical and electrical properties of LEDs regulated by V-shaped pits:(a) AFM images of V-shaped pits on MQWs surfaces with different superlattice cycles[39];(b) EQE and light output power of LEDs with different-size V-shaped pits vs. forward current (V-shaped pits sizes of sample A and B are 70~110 and 110-150 nm,respectively)[40];(c) light output power and electrical resistance of LEDs prepared by different processes[41];(d) schematic diagram of holes flowing in V-shaped pits[42]

近年来,GaN 外延层中V 形坑的微观结构、侧壁量子阱的发光机制、V 形坑对器件光电性能的影响以及通过V 形坑调控器件性能的研究逐渐丰富起来。GaN 基LED的发光波段向黄光乃至红光发展,器件类型向外延结构更为复杂的边发射、垂直腔发射激光器发展,V 形坑缺陷在上述器件中的微观形貌以及对器件性能的影响值得进一步研究。