一种适用于音频调制的混合架构低功耗Σ-Δ 调制器

安胜彪 ,夏 爽,王 敏,陈国通,杨瑞霞

(1. 河北工业大学电子信息工程学院,天津 300401;2. 河北科技大学信息科学与工程学院,石家庄 050018)

随着物联网时代的到来,需要更多性能优良的模数转换器来优化无线传感网络.例如环境信息监测、体征监测和交互式多媒体系统等,都需要模数转换器具有较高信号噪声失真比(SNDR).因SAR ADC 的结构特点,其主要应用于中低速、中等分辨率的传感网络中[1-2].SAR ADC 虽具有很高的功耗效率,但是由于集成电路元件间匹配精度的限制,SAR ADC 很难实现高的精度.通常为了实现高精度SAR ADC,需要加入额外的校正电路,但这往往是以额外的硬件资源和降低系统的转换速率为代价的,甚至还会大大增加电路的实现成本,比如电路出厂后的激光校正过程.而Σ-Δ ADC 则由于采用了过采样和噪声整形技术,大大降低了对元器件匹配的要求,很容易实现12位以上的转换精度[3].鉴于这两种类型ADC 的优点,提出了一种将SAR ADC 和Σ-Δ ADC 相结合的架构. ADC 通过噪声整形和过采样(OSR)技术不仅降低了所需信号频带中的量化噪声,提高了模数转换器SNDR(信号噪声失真比)[4],同时也降低了调制器功耗.

1 调制器结构框架

高阶噪声整形需要具有运算放大器的高阶积分器,同时OSR 需要高速采样工作,这也将增加ADC的总功耗.综合考虑,该调制器选用前馈架构,该架构对积分器中的运算放大器失真不敏感[5],选择多位量化器ADC 来降低放大器的转换速率,以降低ADC的整体功耗[6].

当ADC 中的多位量化器由Flash ADC 实现时,由于通过电阻网络的静态电流和多个比较器的动态电流,ADC 的功率仍然很大.此外,在传统的前馈调制器中,在ADC 的输入节点处需要使用放大器构成的有源模拟加法器,这额外增加了调制器的功耗[7].

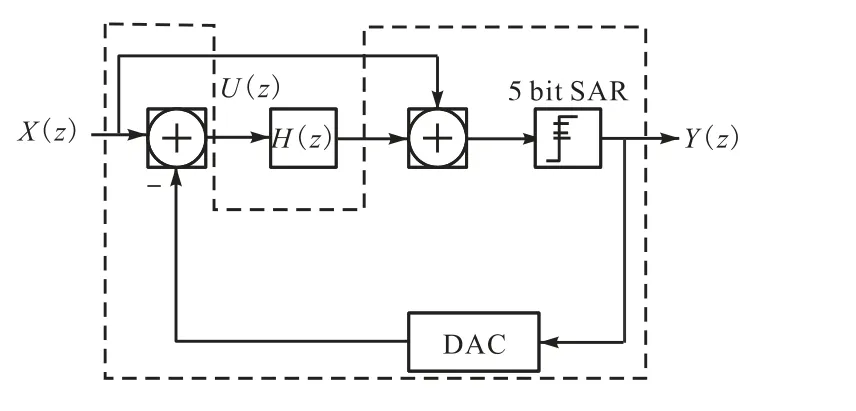

综上所述采用了一种不含有源模拟加法器的多位前馈ADC 实现方案[8],积分器采用无静态电流的环形放大器实现[9-10],嵌入SAR ADC 的无源加法器采用分离电容阵列和动态比较器实现.方案构架如图1 所示.

图1 本文提出的Σ-Δ调制器构架Fig.1 Proposed Σ-Δ modulator

2 芯片电路设计

根据调制器系统框架图,并综合调制器的功能和性能相关参数,设计出了该调制器的电路级实现结构,其由可重复使用的5 bit SAR ADC 和两个积分器组成,如图2 所示.在ADC 的采样阶段Φ1期间,SAR ADC 的电容器阵列对输入信号进行采样,并且电容器CS 对积分器输出进行采样.在该采样操作之后,SAR ADC 在SAR 逻辑的控制下以二进制搜索方式量化采样信号并通过DAC 输出.之后,在电容器阵列的顶板上产生余差电压VRES.

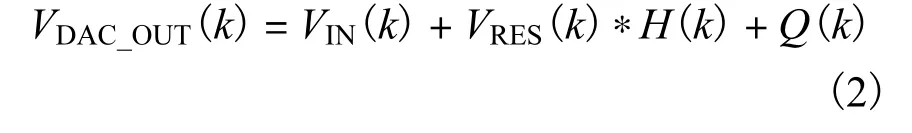

式中:VIN是输入采样信号;是DAC 的输出电压.然后在ADC 的积分阶段Φ2期间由两级积分器处理该余差电压,当前采样的数字输出可以表示为

式中:H(k)是积分器的传递函数;Q(k)表示ADC 的量化噪声与比较器噪声的和.将式(1)代入式(2),得到

2.1 SAR ADC单元电路设计

在所提出的调制器架构中,SAR ADC 不仅用作量化器,还用于调制器中的信号采样.

这种复用技术的另一个优点是所提出的ADC 中输入前馈,进而可以降低与ADC 输入信号无关的积分器摆动,同时降低对运算放大器的性能要求,包括运放的开环增益和电源电压等[11].

图2 本文提出的Σ-Δ 调制器电路结构Fig.2 Circuit structure of the proposed Σ-Δ modulator

由于输入信号直接采样到SAR ADC 的电容器阵列上,因此加法器仅需要对两个积分器的输出求和,该信号幅值在多位ADC 中通常非常小.因此ADC 前面不需要全摆幅的模拟加法器.利用可重复使用的SAR ADC 和前馈拓扑,ADC 几乎可以实现轨至轨的输入信号范围.因此,可以使用小电容器来满足系统对热噪声的要求.尽管ADC 花费1/2 时钟周期来采样积分器的输出,但小的采样电容器CS 将降低对第2 级积分器的要求[12].

异步SAR ADC 是所提出的ADC 架构中的可重用量化器.通过使用异步时钟发生器可以避免高频片外时钟.其工作程序可分为采样、再分配和模数转换.SAR ADC 采用改进的切换方案来降低开关能量耗散和单位电容器的数量.与使用传统开关时序的SAR ADC 相比,单位电容的数量可减少1/2.这意味着只需要16 个单位电容即可实现5 位模数转换,从而将5 位ADC 的电路元件减少了1/2[13].通过切换最后一个单位电容的一侧来捕获最终的5 位残余误差,而不是像传统结构在转换阶段保持不变.这样也可降低芯片功耗,节省芯片面积.SAR ADC 电路结构如图3 所示.

2.2 积分器单元电路

积分器通过反馈环路中的电容充放电来实现求和的功能,本文所设计的积分器是双端输入双端输出的积分器,图4 所示为本文所设计的积分器结构,内部主要包含3 个模块:运算放大器,共模反馈电路,偏置电路.图4 中,φ1、φ1a为采样开关,φ2、φ2a为积分开关,皆为传输门,用两互不交叠的时钟控制.φ1、φ1a闭合,φ2、φ2a断开,在此期间内,量化器进行采样和转换工作,即第1 级积分器的采样.同时,第2 级积分器对第1 级积分器结果进行采样.φ2、φ2a闭合,φ1、φ1a断开,在此期间内,量化器的量化结果通过DAC 反馈到输入端,与输入信号相减送入积分器.第1 级积分器对差值信号进行积分,第2 级积分器对第1 级结果进行积分,即积分器的输出比输入信号要延迟2 个量化器的输入信号.

图3 可复用SAR ADC结构单元电路Fig.3 Reusable SAR ADC structural unit circuit

图4 积分器单元电路Fig.4 Integrator unit circuit

3 版图设计及后仿真

在SMIC 0.18µm 工艺条件下完成了版图绘制和验证工作,图5 为芯片版图,ADC 的有效区域为0.56 mm2.在ADC 的输入端使用自举开关,以降低导通电阻的非线性[14].使用多个单位电容单元构建电容器,以实现系数的精确比率匹配.利用MIM 电容作为电路的单位电容,实现在小芯片面积条件下的高密度集成.电容阵列的差分结构完全对称分布于比较器两侧,用于提高电路整体抗噪能力,将数字控制逻辑统一放置在芯片后端,并对数字部分与模拟部分进行有效隔离可以减小数字噪声对前端模拟模块的干扰.整体设计结构保证ADC 模拟部分的对称排列.

图5 调制器芯片版图Fig.5 Modulator chip layout

图6 和图7 为不同输入情况下FFT 频谱图.仿真分析中Σ-Δ ADC 差分输入0~25 kHz 正弦波,采样频率为3.2 MS/s,OSR=128,并对仿真结果使用想DAC 处理后采样进行FFT 分析,峰值SNR=126 dB.该芯片的总功耗为3.65 mW.模拟和数字电路的供电电压均为1.8 V,FOM 为0.27 pJ/转换.

表1 总结了所提出的ADC 的性能,并与之前同种类型和工艺条件下ADC 进行了比较.该结构类型的Δ-Σ ADC 各项性能指标优越,仿真分析结果证明了所提出ADC 结构的可行性.

图6 23 K输入频率下FFT频谱图Fig.6 FFT spectrum at 23 K input frequency

图7 13 K输入频率下FFT频谱图Fig.7 FFT spectrum at 13 K input frequency

表1 不同结构类型Δ-Σ ADCTab.1 Different structural types Δ-Σ ADC

4 结 论

本文针对目前快速发展的电子信息技术,提出了一种适用于音频处理模数转换器的低功耗、高分辨率调制器方案2 阶5 位量化结构的Σ-Δ 调制器.

(1)调制器除了应用最基本的提高系统的过采样率(OSR)、量化器位数以及积分器的阶数外,设计了基于SAR 结构可复用量化器Σ-Δ 调制器,将量化器中不存在静态功耗的动态SAR 比较器进行重复使用,以及将有源加法器替换为无源加法器等方式,进一步降低了系统功耗和芯片面积,并提升了调制器的有效精度.

(2)通过对电路结构优化,在过采样率为32 的条件下,对0~25 kHz 模拟输入信号进行FFT 频率分析,其分辨率可达18 bit,功耗3.65 mW。可以看出,该结构调制器在满足低功耗要求的同时满足音频应用对精度的需求.相对其他0.18 μm CMOS 工艺实现的调制器性能,该结构具有较高的数据转换效率和更好的优值.通过与其他结构类型Σ-Δ ADC 进行对比分析,显示该结构的创新和优越性.