一种交叉互联的高可靠锁存器

(合肥工业大学 电子科学与应用物理学院,安徽 合肥 230009)

锁存器作为具有记忆功能的存储器件,被广泛地应用于各种逻辑电路当中。它的可靠性会影响到整个芯片的工作状态,若锁存器发生故障,将严重影响整个芯片的稳定性。

当芯片工作在太空环境中时,芯片中的锁存器会因为辐射发生各种不良现象。由辐射引起的问题主要分为总剂量效应以及单粒子效应。其中随着工艺的逐渐成熟,总剂量效应的影响在不断地减小。单粒子效应是由高能粒子轰击引起的器件损坏或逻辑电平翻转。主要包括单粒子翻转、单粒子瞬态以及在入射粒子能量极高的情况下出现的单粒子烧毁和单粒子栓锁等。后两种只有在粒子能量极高的情况下才会触发,因此出现的频率较少。现阶段,随着器件特征尺寸的减少,电路的供电电压以及节点处的电容也随之变小,使节点发生翻转的临界电荷明显减小,低能量粒子的轰击也有可能引起敏感节点逻辑状态发生翻转,导致芯片发生SEU的可能性在不断地提高。而且由于器件的高密度,使得单个粒子轰击时产生的电子—空穴对会同时影响到多个节点[1],使电路中几个相邻节点同时发生翻转,发生多节点翻转(Multiple Node Upsets,MNUs)。目前工艺尺寸下常出现的是DNUs(Double Node Upsets)。据相关研究表明,SEU以及DNUs是引起电路产生软错误率最高的一种因素,国内外学者提出了许多针对SEU 以及DNUs的锁存器加固方案[2]。

对于锁存器的加固技术主要有两种比较经典的方法,一是通过将简单的静态锁存器复制多个,再加上一个表决器来判断正确的锁存值。三模冗余方法是此类方法一种经典的加固方案,该方法能够有效地屏蔽锁存器内部节点的软错误,但是带来了巨大的面积功耗和延时开销。另外对于DNUs没有很好的一个容忍能力。另一种加固方法是抗辐射加固设计,这种方法不仅能有效地缓解软错误对锁存器的影响,还能取得较低的性能开销,因此被广泛应用。目前这类方法比较常用的是采用以C单元为关键部件的加固方案,利用C单元的保持功能来保证电路内部节点的稳定,但这种方法只适用于高频电路中。

本文为了完全容忍SEU以及DNUs,并且降低锁存器的开销,增加加固锁存器的适用范围,基于抗辐射加固设计方法提出了一种新的抗辐射加固锁存器。该锁存器通过采用具有保持功能的DI单元作为基本器件,保证内部结构节点状态的稳定。并且调整了内部器件之间的连接关系从而减少了器件的个数。经过大量的SPICE仿真实验证明,与常用的以C单元为关键部件的抗辐射加固结构相比该结构在保证容忍SEU以及DNUs的同时,又保证了面积、功耗、延迟方面较小的开销,并可适用于低频电路中。本文将提出的结构称作ACCRL结构。

1 电路描述

这一部分主要分析ACCRL结构以及核心组件DI单元的电路组成和工作模式,并且分析ACCRL结构的容错能力。最后对ACCRL结构进行故障注入,验证ACCRL结构的可靠性[3]。

1.1 DI单元以及ACCRL结构的电路组成

DI电路结构构成及其工作模式如图1所示。DI单元为一个含有两个输入、一个输出的三端器件,由一个PMOS晶体管以及一个NMOS晶体管组成。它有4种工作状态,在DI单元的两个输入状态相同时,它的功能与一个反相器的功能类似。即两个栅极输入端的逻辑值都为1时,输出逻辑值“0”。在两个栅极输入端的逻辑值都为0的情况下,输出逻辑值“1”。在输入不同时,它的输出情况主要分为以下两种。① PMOS晶体管的栅极输入为高电平1,NMOS晶体管的栅极输入为低电平0。整个器件的NMOS晶体管以及PMOS晶体管都处于关断的状态,它的工作状态为高阻态,输出端的电容会保留上个阶段的输出电平。② PMOS晶体管的栅极输入为低电平0,NMOS晶体管的栅极输入也为高电平1。在这种情况下,PMOS管与NMOS管都处于导通的状态,若晶体管处于正常尺寸下,则输出端的逻辑值会处于一个中间态。为了消除这种中间态,在考虑功耗的情况下,本文将NMOS晶体管的尺寸上调,PMOS晶体管的尺寸下调。这样使这种中间态下移达到低逻辑状态。在锁存器正常工作时,只会处在两个输入端逻辑电平相同的状态,不会出现输出处于高阻态以及PMOS晶体管和NMOS晶体管都导通产生瞬间大电流的状态,保证了较小的功耗。

图1 DI电路构成以及它的4种工作状态

提出的结构如图2所示,它由12个核心结构DI单元组成,激励D分为3路输入,并由A3节点作为整个电路的输出Q。为了便于分析,将ACCRL结构中的DI单元分为上中下三层,分别为上层的DI1、DI4、DI7、DI10,中层的DI2、DI5、DI8、DI11,以及下层的DI3、DI6、DI9、DI12。另外将每层的DI单元分为4级,具体为第一级的DI1、DI2、DI3,第二级的DI4、DI5、DI6,第三级的DI7、DI8、DI9和第四级的DI10、DI11、DI12。按照组成ACCRL结构中DI单元的输入输出关系来看,输入到DI单元中的NMOS晶体管上的输入A的逻辑值不发生翻转的情况下,输出就不会发生翻转。将ACCRL结构中的每一层结构中的DI单元的输出都输入到该层下一级DI单元中的NMOS晶体管上,并且与其他层DI单元的PMOS相接。也就是说ACCRL结构上中下三层结构的输出节点分别在发生SEU时,并不会发生影响到其他层的输出状态。若每一层的每一级之间都按照这样的连接关系,当某两个不同层上的节点发生SEU时,有一层一定处于正常工作状态,即有4个节点一定储存了正确的逻辑值,考虑到DI单元的保持状态,将这一层的节点加入到对发生翻转的节点的纠正过程中,也就是打乱ACCRL结构的两级之间的连接关系,将使尽量多的DI单元加入到错误节点滤除的过程中。如图2所示,在ACCRL结构中每层的第三级与第四级之间的输出发生了交叉连接。分析发现,交叉连接后只需三层四级DI单元就可以完全容忍DNUs。而按照正常的每一层上DI单元的输出连接到该层的下一级DI单元上,需要三层六级DI单元才能对DNUs完全容忍。

图2 本文提出的结构

1.2 抗SEU和MNUs性能分析

在ACCRL结构内部一共存在15个点,由于节点E(E1、E2、E3)通过传输门与节点A(A1、A2、A3)直接相连,所有节点A和节点E可以看作同一组点。总共只需要考虑ACCRL结构中的12个节点,把它们分为三层,第一层为节点A1、B1、C1、D1,第二层为节点A2、B2、C2、D2,第三层为节点A3、B3、C3、D3。由于并不会发生翻转,再经过第三级和第四级DI单元后,会将A1的逻辑状态值恢复为高电平1。另外一种情况下,输入D为低电平0,A1节点逻辑状态发生翻转,由0变为1。仅有可能B1节点发生翻转。而DI1的输入状态A为1,B为0,则DI1的输出B1的逻辑值会发生翻转变为0。B1只可能会造成C1翻转,B1在经过DI3单元时,会使DI3处于保持状态,保持C1正确的电平,最后经过第四级和第一级DI单元后将A1和B1的逻辑值恢复到正确状态。同样的当A2、A3发生SEU时,也能自恢复到正常逻辑电平。

考虑任意两个节点发生翻转的情况,并将节点的组合分为三组。第一组为发生翻转节点对的位置位于同一层上,第二组为发生翻转的节点对位于同一级内,第三组为发生翻转的节点对位于不同层与不同级上。本文在每一组中任取一个组合进行故障注入加以分析。第一种情况下,发生翻转的两个节点的位置位于同一层上,选择A1与C1节点进行故障注入。在输入D为0的情况下,A1与C1同时发生SEU,由0变为1。使得DI1与DI7的输出B1和D1节点同时发生翻转,由1变为0。这时在同一层上的所有节点都发生了翻转,而其他层上的DI单元由于在NMOS晶体管上的输入状态并没有发生翻转,因此输出端的逻辑值并不会发生翻转。若按照每一层上每一级的输出连接到下一级的NMOS管上,第一层上的4个节点必将保持错误的逻辑值。但是经过交叉连接后,D1节点的错误电平经过DI12单元将被阻塞,保持A3的正确状态,不会再传播到下一级。而节点D2处的正确逻辑值被输入到DI10单元上的NMOS上,经过几级DI单元的传播之后,将恢复发生翻转的节点处的逻辑状态。与之类似,同一层上节点的其他组合以及在输入D为0时,发生翻转的节点处的错误逻辑值也会恢复到正确值。第二种情况下,发生翻转的节点位于同一级内。选择A1与A3节点进行故障注入,在输入D为0的情况下,A1与A3节点发生翻转由0变为1。DI3单元的输入组合变为了NMOS输入为1,PMOS输入也为1,DI1的输入组合变为了NMOS输入为1,PMOS输入为0,使B1与B3的逻辑状态也会发生翻转由1变为0,B2节点保持正确的逻辑值。而C1节点由于DI4处于输出保持状态,会保留下正确的逻辑状态。C2节点由于DI5的NMOS的输入没有发生翻转会继续储存一个正确的逻辑状态,C3节点由于DI6的输入都发生了翻转,会由0变为1。在下一级可以看到只有DI9单元的NMOS输入发生了翻转,因此只有D3节点发生了翻转,由1变为0。若D3连接到同一层的下一级DI单元上的NMOS上,会使E3节点处于一个保持状态,则会保持A3处的错误状态。本文在这里改变了第三级第四级的连接关系,使D3节点处的错误电平输入到第二层DI单元的NMOS上,而第一层上正确的电平输入到第三层DI单元的NMOS上,使得E2处于保持状态,并保持A2的正确状态,使错误信号不再传播。同时第一层上保持正确逻辑状态的D1经DI12、DI3、DI6、DI9单元将E3、A3、B3、C3的错误电平修正为正确状态。与之类似,不同级上节点的其他组合以及输入D为1时,发生的翻转也会恢复到正确的逻辑状态。第三种情况,本文选择B1与C2节点进行故障注入,在输入D为0的情况下,若B1与C2节点发生翻转,则B1由1变为0,C2由0变为1;第三级DI单元的输出C1节点处于保持状态,将保留正确的逻辑状态;而C2节点由于节点B2没有发生翻转,并不会发生翻转,又被刷新为状态0,第三层上没有故障注入,C3节点扔然保持正确逻辑。整个结构中的节点都恢复到正确的逻辑状态。与之类似,其他不同层和不同级上节点的组合以及输入D为1时的情况下,发生的翻转也会恢复到正确的逻辑状态。

本文采用双指数电流源模型对ACCRL结构进行故障注入,并在同一时刻在不同节点处同时进行故障注入,验证ACCRL结构容忍DNUs的能力。由于该结构是静态锁存器,且工作频率很高,不用考虑漏电流[4]。

首先验证ACCRL结构容忍SEU的能力。选取ACCRL结构中的所有节点A1、A2、A3、B2、C1、C2、C3、D1、D2、D3进行分时单点故障注入,实验结果如图3所示。在图3中可以看到发生翻转的每一个节点在逻辑值发生变化之后,很快地自恢复成之前存储的逻辑值。说明ACCRL结构能够完全容忍由高能粒子引起的SEU。

另外为了全面模拟上文中提到发生DNUs的节点对组合,实验在上文的每一种分类中都选取了一个节点对组合,分别为(A1,A3)、(B3,D2)、(A1,C1)、(B2,C2)。实验结果如图4所示,在图中可以看到发生翻转的节点对在发生逻辑值翻转之后,在很短的时间内就自恢复成之前存储的逻辑值。说明ACCRL结构能够完全容忍由高能粒子引起DNUs。

2 对比仿真

采用HSPICE工具对ACCRL结构以及现存的容错结构进行功耗、延迟以及PDP方面的比较。仿真条件如下:采用45nm PTM工艺,温度设置为25 ℃,电源电压设置为1 V。为了公平起见,本文中涉及到的所有结构的尺寸为能完成其设定功能的最小尺寸[5]。

2.1 面积开销与功耗分析

采用UST(Unit Size Transistors)来衡量面积开销。并在UST中加入了源区和漏区的面积,具体计算公式为

图4 ACCRL结构两个节点故障注入波形

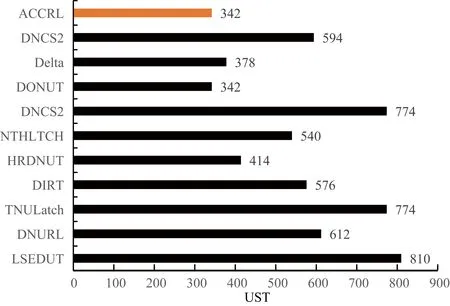

由于提出的ACCRL结构采用了只有两个晶体管组成的DI单元作为核心器件,并且在内部的连线上舍弃了正常的连线方式,采用了交叉耦合的连线方式,减少了器件的使用。与其他加固结构的面积开销比较如图5所示,在图中可以看到在UST这一项指标中DONUT结构和提出的ACCRL结构的面积开销要明显小于其他结构。

图5 相关结构面积开销比较

面积开销一般与功耗相对应,本文选择的对比结构大部分采用了大量的钟控模块,所以造成有些结构的面积与功耗不相符的情况。与其他加固结构的功耗开销比较如图6所示,在图6中可以看到ACCRL结构的功耗仅大于LSEDUT、HRDNUT、DNURHL三个结构的功耗。而LSEDUT、HRDNUT、DNURHL三个结构为了降低功耗,在内部加入了大量的钟控单元,这样虽然降低了功耗,但是带来的面积开销是巨大的。可以看到LSEDUT的面积开销比ACCRL结构增加了136%,而功耗仅仅降低了7%。HRDNUT面积开销增加了21%而功耗也仅仅降低了14%,DNURHL面积开销增加了31%而功耗也仅仅降低了28%。大量的钟控模块还可能造成整个电路的不稳定性。综合考虑了面积开销与功耗后,在ACCRL结构中也加入了小部分钟控结构,达到了面积开销与功耗两方面较好的指标。

图6 相关结构功耗比较

2.2 PDP分析

PDP能够很好地衡量一个电路的功耗延迟特性。本文比较了这些结构的D-Q延时(输入输出延迟)和整个电路的平均功耗的乘积。与其他加固结构的PDP比较如图7所示,在图7中可以看出ACCRL结构由于具有较小的功耗和延迟,使得整体的PDP也处于较小位置。在这些结构中只有DNURHL的PDP比文中提出的ACCRL结构PDP小。但是同样的DNURHL结构为了达到较小的PDP在结构中加入了大量的钟控单元。与ACCRL结构对比PDP只减小4%,面积开销却增加了31%。

图7 相关结构PDP比较

2.3 综合考虑

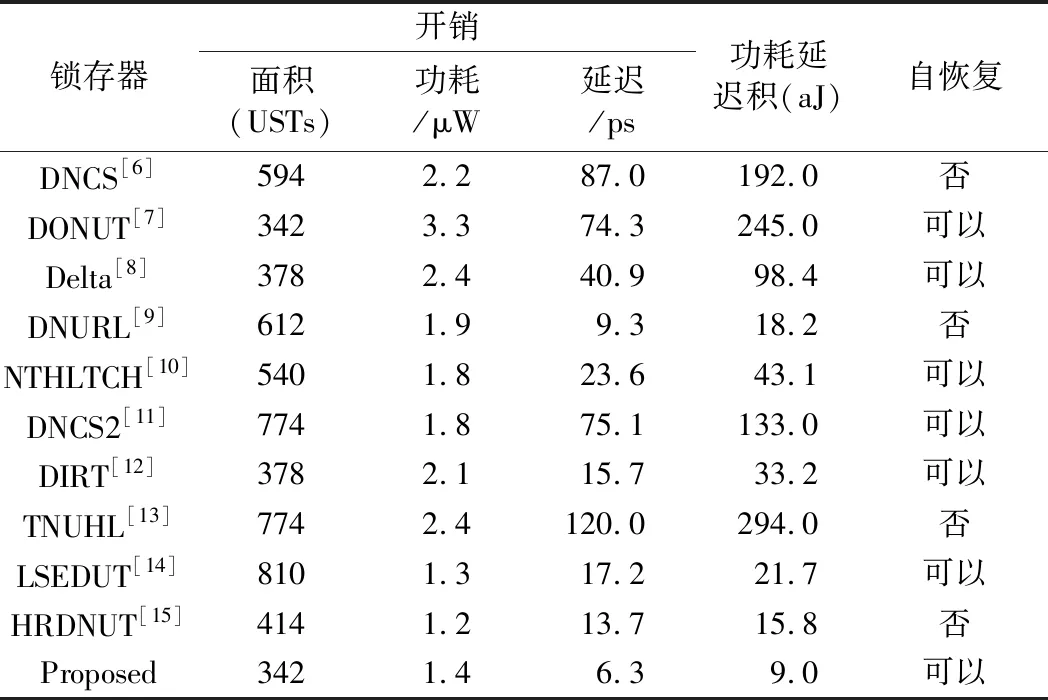

表1总结了所有结构的面积开销、功耗、延迟,以及PDP方面的指标。ACCRL结构比所有对比结构的平均面积开销减小了63%,功耗降低了45%。PDP也是所有结构的最小值。在表1还加入了自恢复指标,用来表示本文提到的结构在发生SEU或DNUs后能不能自恢复所有的内部节点的逻辑状态。ACCRL结构不仅能够使输出状态保持正确值,还能自恢复所有的内部节点。

表1 各存储单元各项数据一览表

3 结束语

本文提出了一种高可靠的锁存器。该锁存器以DI单元作为核心器件,并且内部连线采用了交叉互连,显著减少了器件个数的使用。在45nm PTM工艺下的HSPICE仿真表明,该结构不仅能够完全容忍由辐射引起的SEU以及DNUs,而且与传统的具有容错性能的锁存器相比,在面积、功耗、PDP方面都有很大的提升。另外空间环境是极为复杂的,工作在太空中芯片还存在总剂量效应等一系列的不良辐射反应。本文采用的HSPICE模拟方法只能初步分析SEU对电路结构的影响,还需要将该结构插入实际芯片中进行更加精确的辐照实验,进一步研究电路的可靠性以及分析空间其他因素的影响。