数字锁相放大器技术及光谱检测应用进展

杜振辉, 张永明, 刘翰蔚2, 王玉祥, 张 帅

(1.天津大学 精密测试技术及仪器国家重点实验室,天津 300072; 2.天津开发区爱特网络系统有限公司,天津 300457)

锁相放大器(Lock-In Amplifier,LIA)可从干扰极大的环境中提取已知频率的微弱信号,具有灵敏度高、抗干扰能力强等特点,目前已广泛应用于光电通信、光谱、光断层摄影与生物医学等领域[1-6]。随着现代检测任务与测量环境的多样化发展,LIA技术已成为现代科研与工程领域关注的重点。

LIA最初的形式为模拟锁相放大器(Analog Lock-In Amplifier,ALIA),其鉴相器(Phase Sensitive Detector,PSD)由模拟器件搭建而成。随着数字电路的发展,LIA逐渐数字化,出现了数字锁相放大器(Digital Lock-In Amplifier,DLIA)[7-9]。早期的DLIA由数字集成电路(Integrated Circuit,IC)构成,然而由于其集成度高、电路更迭成本较大,因此目前DLIA多采用单片机(Microcontroller Unit,MCU)、数字信号处理器(Digital Signal Processor,DSP)、可编程逻辑器件(Field Programmable Gate Array,FPGA)与计算机(Personal Computer,PC)进行设计[10-13]。其克服了模拟器件存在的温漂、噪声源多、稳定性相对较差等问题,同时也由于其设计的可重复性,极大地降低了电路的更迭成本,成为LIA技术的主流。目前,基于DLIA技术的研究成果丰富,已衍生出多种应用方向,对其技术的发展有重要意义。

本文讨论了数字锁相放大器的主要设计思路、单相PSD到双相PSD演变、不同硬件构建数字锁相放大器的优劣以及不同应用条件下数字锁相放大器技术之间的差异。针对光谱分析应用,综述了动态信号检测失真、载波信号波动时的频率跟踪、相关参数优化及性价比等实际问题的解决方案,并对数字锁相放大器的发展与应用做了展望。

1 DLIA设计思路

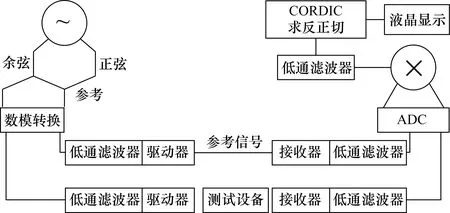

DLIA的设计思路分为信号输入通道设计、互相关检测算法设计、硬件构成设计与参考信号源的设计,如图1所示。其中,信号输入通道的设计多采用模拟电路设计,目的在于对待测信号进行预处理,以满足后续模拟数字转换器(Analog to Digital Converter,ADC)的采样要求以及互相关检测算法的输入要求;互相关检测算法设计为DLIA设计的核心,不同的算法实现方式会对DLIA的性能有显著影响。

互相关检测算法依托于具体的硬件设计完成,这些硬件包括MCU、DSP、FPGA以及PC。由于不同硬件自身结构的差异,导致由他们构成的DLIA在性能与参数上会有明显差异。

同时,在波长调制光谱分析与频率调制光谱分析实验中,需要对调频信号进行检测,由于此时调制信号频率未知,就无法人为对DLIA提供参考信号源,需要DLIA对待测信号频率进行识别并内部生成其相应的参考信号,因此,不同的应用条件又衍生出不同的DLIA技术。

图1 DLIA的基本结构框图

1.1 信号输入通道设计

信号输入通道的设计主要是为解决待测信号幅度匹配及外界干扰等问题。

在使用运放电路对待测信号进行放大时,需要考虑对噪声的抑制。运放噪声由电压噪声、电流噪声以及热噪声叠加而成[14]。当所用电阻阻值较小时,电压噪声起主要作用;当阻值较大时,电流噪声起主要作用;当阻值居中时,热噪声也会产生影响,其影响大小取决了其他两相的幅值。由此,在设计低噪声运放电路时要注意以下四点:① 选取的运放应具备低噪声电平、低噪声电流以及低转角频率;② 保持运放电路中的电阻达到一定标准,以减小电流噪声与热噪声;③ 将噪声的增幅严格限制在运放电路的最小电流上,形成运放的正常运转;④ 电路布线时确保输入信号回路完全接地。

利用陷波器消除工频干扰。利用硬件电路搭建高阶陷波器,其陷波效果与阶次相关,阶次越高,陷波效果越好,同时设备的成本与体积也就越大[15]。目前高性能陷波器的设计多采用软件的方法,即在高性能处理器上通过小波变换滤波[16]、自适应滤波[17]、卡尔曼滤波[18]等滤波算法来实现。相较于硬件电路而言,软件实现的陷波器更具灵活性。由于工频干扰在49~51 Hz区间内波动,传统陷波器通常存在滤除精度不高的问题。在硬件实现方面,陈振生[19]等人在陷波电路结构中引入了频率/电压转换器与压控带阻滤波器结合的设计方案。其利用频率/电压转换器实现对频率的精确跟踪,从而令其抗干扰性能不受工频频偏的影响,性能稳定。而在软件实现方面,王宇[20]等人提出可采用快速傅里叶变换(Fast Fourier Transform,FFT)实时提取工频干扰频率值,此外,为保证系统实时性,其通过减少FFT的采样点数并在采用序列后续补零,以达到较高的检测精度。两种方案均具有明显的效果。

抗混叠滤波器的设计是为了保证输入至ADC的信号符合ADC的采样要求。为保证输入信号符合采样定理,提高ADC的采样频率通常意味着成本的提高,因此多在采样前设计抗混叠滤波器。对高速信号进行频率抽取可有效降频,然而当抽取倍数较大时,滤波器阶次较多,其延迟时间和硬件资源消耗都很大。针对该问题,李汉阳[21]提出了一种级联滤波结构代替直接抽取滤波结构,在同样的滤波效果下,级联结构极大地减少了资源的消耗,并降低了信号处理的延迟时间。

1.2 DLIA算法设计

DLIA算法设计包括互相关检测算法设计与低通滤波器设计。其中,互相关检测算法设计方式分为单相PSD检测与双相PSD检测。单相PSD的优势在于占用资源少,在DLIA发展初期,硬件资源相对有限,故多采用该设计。然而,单相PSD算法会受到待测信号与参考信号之间相位差的干扰,因此在单相PSD算法中,对信号间相位差的检测是极其重要的处理过程。对此,Vandenbussche[22]等人采用将测量路径与参考路径完全对称的方式,来避免信号间相位差带来的影响。

相对而言,双相PSD检测采用了正交I、Q两路PSD的形式,这种算法有效避免了信号间相位差对检测结果的影响[12],但也由于增加了一路PSD,导致了资源占用率的提高。在目前的设计过程中,硬件资源相对充足,因此对PSD的设计多采用双相结构,从而保证待测信号与参考信号之间的相位匹配。

此外,在PSD的实现方式方面,可采用的方法由反正切函数与坐标旋转数字计算机(Coordinated Rotation Digital Computer,CORDIC)算法。由反正切函数得到的特征曲线线形度最佳、鉴相范围最广、产生的误差也最小,在全球定位系统载波跟踪环中均有成功的应用[23]。相较于反正切函数,CORDIC算法的优势在于仅利用移位和累加操作就可实现鉴相功能,非常适合通过硬件电路实现功能,但是算法输入输出的范围较小,具有一定局限性。对此,王珂南[24]等人在CORDIC算法中增加了象限转换和相位转换功能,使改进后的鉴相器输入输出范围扩大至4个象限,极大拓宽了其应用范围。

在低通滤波器的设计方面,目前可选择的拓扑结构为有限脉冲响应(Finite Impulse Response,FIR)结构、无限脉冲响应(Infinite Impulse Response,IIR)结构以及多级反馈滤波级联等结构。FIR滤波器实现方式简单且具备线性相位,但需要的参数更多、运算量更大;IIR滤波器需要的参数较少,但其相位非线性。然而在实际应用中,对于一个频率较高的信号,既需要较快的运算速度,也需要相位线性,因此级联积分梳状滤波器(Cascaded Integrator-Comb Filter),即CIC滤波器,成为了最佳选择。其优势在于不仅相位线性,更在于其易于操作,仅需延迟、加减法便可实现。但是,传统的CIC滤波器也具有通带衰减过大的问题。针对该问题,谢海霞[25]等人提出了一种改进型的CIC抽取滤波器,在分级抽取滤波器的基础上用锐化技术改善了滤波器通阻带衰减,采用内插二阶多项补偿函数对通带进行额外补偿,使带内更平坦,并利用多相分解的方法降低了抽取滤波器的采样率。实验证明,改进后的CIC滤波器具有更好的通、阻带特性。

此外,以多级反馈滤波级联的拓扑结构替代常规FIR滤波器,可提高检测精度,并扩宽其应用条件。如SR865采用了无源滤波、FIR与IIR多级滤波级联拓扑结构,其相位分辨率为(360/232)°,同时其时间常数最小可达1 μs,达到了滤波效果与时间常数之间极佳的平衡状态。

1.3 硬件构成设计

在DLIA的硬件构成方面,多采用MCU、DSP、FPGA以及PC进行设计。

基于MCU的DLIA内部指令只能顺序执行。这种结构简化了DLIA的开发难度,但也存在局限性。若中央处理单元(Central Processing Unit,CPU)被占用,MCU则无法对新数据进行处理,因此限制了DLIA的带宽。例如采用MSP430系列的低功耗单片机搭建的数字锁相放大器[26],虽然可完成对微弱正弦信号的检测,但其带宽仅有数百kHz。

DSP采用流水线技术,可并行执行多个操作,提升了DLIA的带宽,同时也提高了其运算能力。李龙华[27]等人研制的一款用于光寻址电位传感器(Light-Addressable-Potential-Sensor,LAPS)检测系统的数字锁相放大器,采用TMS320VC5509A型号DSP开发板,其信噪比可达到63 dB,能准确地检测出LAPS系统的输出信号。

FPGA硬件并行的结构特点使其在进行复杂运算时更有优势,其性能更优,且在实时性要求较高的气体成分检测中有广泛应用。贾兆荣[28]等人设计了基于FPGA的数字锁相放大器与信号采集电路,用于大气透射仪的信号采集处理模块,测试证明该设计有效提高了DLIA的动态范围与测量精度;由范松涛[29]等人开发研制的基于FPGA的数字锁相放大器,其最大示值误差小于±0.2%,远小于国家标准计量要求±5%。但是,高速处理能力也导致其功耗较高、芯片发热量大,在一些温度较高的检测环境中需要进行散热处理。

基于PC的DLIA多采用LabVIEW进行设计,这种设计方式极大地降低了相敏检波算法等数据处理的难度。王力[30]等人设计开发了一款基于LabVIEW的锁相放大器,使用PCI-6251型数据采集卡完成对数据的采集,通过图形化编程完成DLIA的互相关检测算法,同时对白噪声进行了抑制。实验证明,其与仪器化的锁相放大器相比,甚至有更好的噪声抑制效果。此外,基于PC的DLIA集信号输入、处理与显示于一体,其设计、修改的便捷性得到提高。

1.4 参考信号源设计

由于DLIA应用条件的差异,导致其参考信号的来源不同,因此可将参考信号的来源分为外界供给与内部识别两类。对于大部分检测应用而言,均采用外部供给参考信号的形式,这种应用条件要求待测信号频率已知,且参考信号为待测信号的同源信号。在无法提供同源参考信号的条件下,可考虑加入锁相环(Phase-Locked Loop,PLL)或在软件中引入相位自适应算法[19],从而保证待测信号与参考信号之间相位一致,否则当二者之间存在极小相位差时,就会在检测结果中存在极低频的拍频信号,对检测结果造成干扰。

对于频率未知的待测信号,由于无法通过外部供给的形式向DLIA提供参考信号,就需要采用离散傅里叶变换(Discrete Fourier Transform,DFT)、快速傅里叶变换(Fast Fourier Transform,FFT)等方法对待测信号频率进行识别,继而从内部生成相应的参考信号。赵玲[13]等人沿用该思路,采用LabVIEW中的频率检测模块,对待测信号的频率进行了提取,再将频率字送至直接数字式频率合成器(Direct Digital Synthesizer,DDS)中产生所需的参考信号。实验证明了该方案的可行性,但是由于在实际检测活动中,待测信号常混杂其他频率的干扰信号,故该应用条件首先要求在频谱分析中,干扰信号与待测信号频谱相距较远,从而保证可通过滤波或限制频段等方法将待测信号与干扰信号分离;其次要求待测信号的幅值在频谱中相对较大,从而可通过幅值比较等方法将待测信号频率识别出来。此外,针对谐波检测方法中存在的频谱泄露、栅栏现象、运算量大以及实时性差的缺点,王玉梅[31]等人提出了一种基于加窗FFT与小波包变换融合的检测方法,首先利用加窗FFT精确检测出谐波成分,再结合小波包变换快速且有选择地提取所需的谐波分量。结果证明,该方法可有效解决频谱泄露以及实时性差等问题。

与外部供给的形式相比,内部识别的形式增加了FFT(或DFT)与DDS环节用于参考信号的生成,引入了PLL用于保证参考信号与待测信号之间的相位差恒定,故该形式虽然可以检测频率未知的待测信号,但需要消耗额外的资源,同时由于信号处理环节较长,因此也并不适合用于检测快速变化的调频信号。

2 应用相关的研究进展

在光谱分析领域,由于检测任务与所处环境的差异,导致在DLIA的实际应用过程中会产生许多难题。例如在开放光程气体检测实验中存在的动态信号时信号失真与载波信号波动问题、可调谐二极管激光吸收光谱(Tunable Diode Laser Absorption Spectroscopy,TDLAS)实验中存在的便携化检测问题以及太赫兹光谱分析实验中检测精度不达标等问题,对此衍生出许多研究方向。通过对比DLIA在不同方向的研究进展,本文对其应用相关的5种研究进展进行了分析。

2.1 动态信号检测

在开放光程气体检测等实验中,待测信号的幅值会随着距离的改变而改变。当反射点存在微小凸起或凹陷时,待测信号的幅值就会产生快速且微弱的变化[32]。然而,一般的DLIA在检测幅值快速变化的微弱信号时,部分信号点会由于其高频特性被DLIA中的低通滤波器滤除,从而造成对有效信息的破坏。针对该问题,目前的解决思路包括降低积分时间常数与改变低通滤波器结构两大类。

① 降低积分时间常数:为了能够检测到快速变化的信号,就要求DLIA的时间常数足够小。Davies[32]等人在DLIA中的低通滤波器后加入了一个积分器,并将积分时间调整为数字电路时基的整数倍。这种方法有效解决了积分时间较小带来的输出结果不可靠的问题,同时又避免了在积分时间较小而余数较大情况下,测量噪声相对较大的问题。

② 改变低通滤波器结构:Maclachlan[33]等人对低通滤波器的特性进行了分析,并指出只有在待测信号不变的前提下,才能保证低通滤波器的输出结果不掺杂过多的噪声。对此,Vandenbussche[34]等人以具有极佳线性相位与极低等效噪声的倍增有限脉冲响应(Multiplicative Finite Impulse Response,MFIR)谐振器代替低通滤波器。改进后的DLIA不仅可以检测到快速变化的信号,同时也具有极佳的滤波效果。

2.2 性价比提高

提高DLIA的性价比是科研人员长久关注的问题。针对该问题,目前可行的措施有更换滤波结构、使用单相测量代替双相测量、对参考信号方波化等,这些措施多为设法降低乘法器的使用量,从而降低其成本,进而提高DLIA的性价比。

(1) 更换滤波结构:Guan[35]等人将低通滤波器调整为下采样均值滤波器,通过减少采样点的运算量来降低硬件资源,从而达到了降低硬件资源使用率的目的。但是这种方案也有很大的局限性。由于在采样过程中去除了部分采样点,导致对快速变化的待测信号造成了一定程度的信号失真,故认为该方法只适用于检测平坦变化的信号。

(2) 单相测量:Vandenbussche[22]等人将DLIA中的双相测量改为单相测量,以此减少半数乘法器的使用量。同时,为解决单相测量带来的相位误差,Vandenbussche首先分析认为该相位误差是由于待测信号与参考信号经过路径的不同而产生的,继而在此基础上提出,可让待测信号和参考信号同时经过ADC,保证二者相位差恒定后,再进行单相DLIA算法,从而避免二者之间的相位差。

单相测量流程如图2所示。

图2 单相测量的DLIA结构框图[22]

然而该方案同样具有一定局限性。这种处理措施虽然能保证待测信号与参考信号之间的相位差恒定,但却无法保证不同检测活动之间可以维持始终如一的相位差,这就要求每次检测活动进行前都要重新进行基准标定,对检测人员的使用造成了不便。

(3) 参考信号方波化:方波参考信号的优势在于可将PSD中的乘法操作转化为加减操作,从而降低乘法器的使用量。假设参考信号为幅值为1的正交方波信号,即

(1)

(2)

当待测信号经A/D采样后序列为x(n),其与方波参考信号一同进入鉴相器,其输出结果为

(3)

(4)

该方案能够极大地降低DLIA的资源使用率,同时由于将乘法运算优化为加减运算,也可提高DLIA的计算速度。然而,方波中存在的奇次谐波不可避免地会对检测结果造成一定干扰。目前有两种可行的措施用于消除奇次谐波带来的干扰。

① Afanassyev[36]等人提出,可利用DLIA内部的低通滤波器消除3次以上的奇次谐波干扰。通过实验验证发现,该方案对FIR滤波器的阶次要求较高,因此推荐使用IIR滤波器、MFIR谐振器代替FIR滤波器。

② Li[37]等人提出了一种DLIA算法,可用于去除奇次谐波的干扰,同时还能够检测到奇次谐波的幅值与相位。该算法采用两路方波参考并行检测两种频率分量,一路用于高频信号的解调,另一路用于低频信号的解调。相较于传统的解调算法,该算法在低频信号解调的同时,计算了高频信号解调过程中两个正交PSD输出结果的差值,从而消除了高频成分的干扰,能够明显提高待测信号的解调效果。

2.3 便携化检测

目前,越来越多的光谱分析开始向开放环境测量方向发展,将TDLAS技术应用于气体管道泄露检测[38-42]、酒驾检测[43-47]以及深海天然气勘测[48]等已成为光谱分析领域发展的重要方向,这使得DLIA的工作环境不能再局限于室内。然而,传统DLIA产品厚重的机箱却难以支持其进行户外作业,DLIA便携化的问题愈发受到关注。目前,多数DLIA开始向集成板卡方向发展,其载体已得到极大简化。

DLIA板卡实现方式多样,可采用DSP、Multisim、LabVIEW、FPGA等软硬件进行设计[49-55],而FPGA因其并行结构优势,在DLIA的实现载体中占有很大份额。其中,Altera公司开发的软件DSP Builder[51]与Xilinx公司开发的软件System Generator[54]均可与Matlab软件中的Simulink模块配合使用,实现图形化编程,在提高DLIA板卡便捷性的同时,也简化了其设计难度,并降低了DLIA更新换代的成本。

2.4 参考信号频率自跟踪

在开放光程气体检测实验中,由于光程长度是变化且未知的,这就导致检测器接收到的拍频信号的频率是未知的,因此无法人为向DLIA提供所需频率的参考信号[32]。针对该问题,目前有两种可行的措施,分别为FFT法与频率补偿法。

① FFT法:Liu[53]等人提出可先通过FFT获取待测信号频率,再采用DDS生成参考信号从而进行DLIA算法。这种方案的优点在于FFT可快速准确获取待测信号的频率值。但是,由于FFT算法是依据一定采样点数进行的,当待测信号频率改变时,采样点数的变化会导致出现频谱泄露等问题。该问题虽然可以通过加窗操作进行解决,但是由于待测信号频率的时变性,会对加窗操作造成不便。

② 频率补偿法:Tong[56]等人采用多次迭代的措施,将PSD得到的差频值补偿给参考信号,从而实现频率自跟踪,其实现算法如图3所示。这种方法由于不再依赖于采样点数,因此突破了FFT方法自身的局限性,且相较于FFT法,该方案实时性更强。但是,该方案对待测信号包含的频率成分具有一定要求,仅适用于特定的场合。当待测信号包含其他频率的干扰信号时,PSD得到的差频值则不再单一,对迭代过程会造成干扰。因此,频率补偿法只能处理仅含高斯白噪声的待测信号,而FFT法则可做到对特定频率进行甄别。

图3 频率补偿法实现参考信号频率自跟踪[56]

2.5 相关参数优化

在太赫兹光谱分析实验中,通常待测信号极其微弱,需要超高精度的设备对其进行检测[57-58],因此,对DLIA的性能进行优化,改善其特定参数具有重要意义。

在提高精度方面,Vandenbussche[59]等人分析认为,DLIA的精度受限于ADC的采样率与精度、参考信号查找表(Lookup Table,LUT)的精度与DLIA的结构3个方面。该理论为后续如何提高DLIA的方法提供了理论依据,但是对于特定的ADC,其采样率与精度有限,而LUT精度的极限就是ADC的精度,故目前的创新设计多通过改变DLIA的结构以提高其精度。

因此,依据Vandenbussche的理论,Zhou[60]等人将过采样技术应用于DLIA,通过增加DLIA的运算点数、牺牲运算时间与成本,提高了DLIA的精度;Gonzalo[61]等人向DLIA中引入定时计数分析仪(型号为CNT-91),通过提高参考波形频率精度的措施提高了DLIA精度。二者均是通过改变DLIA的结构以达到提高精度的目的,也从侧面证明了Vandenbussche理论的正确性。

此外,笔者认为该理论具备拓展性,即DLIA参数的优化方向有信号输入通道设计、PSD设计与低通滤波器设计3个方向。例如,在信噪比和灵敏度方面,Rahmannuri[62]等人对低通滤波器的截止频率进行了自适应调整,通过循环迭代的方式,对参数的指标进行判断与调整,从而实现了信噪比与灵敏度的提高;在线性度方面,De Almeida[63]等人采用Q积来替代传统鉴相器,优化了DLIA解调结果的线性度;而在DLIA工作环境拓展方面,Cheng[64]等人通过对信号输入通道与算法的实现平台进行设计,成功设计出一款可在200 ℃条件下连续工作4 h的DLIA,极大地拓宽了DLIA的工作温度范围。

3 DLIA的发展趋势

在DLIA的发展历程中,带宽、动态储备与噪声等关键参数指标得到了极大优化。其中,在提高分辨率、带宽、动态储备与降低噪声方面,目前多从信号输入通道的角度来考虑,而对于相位分辨率与时间常数的优化,则多依赖于DLIA内部互相关检测算法的实现方式。

在DLIA参数指标演进的过程中,对性能更加优良的ADC进行合理选型是提高DLIA各类参数必不可少的条件之一。高速ADC(≥10 MS/s)极大地提高了DLIA的工作带宽;精密ADC(24~32 bits)则在提高DLIA分辨率方面起到了重要的作用;同时,在相同噪声抑制能力的前提下,精密ADC也由于其位数较多而具有更高的输出精度,因此也具备了更高的动态储备[65]。此外,目前的DLIA设计更多采用CORDIC算法代替正弦查找表的方式来生成解调所需的参考信号,这一变化也在一定程度上提高了DLIA分辨率[66];在信号输入通道中设置抗干扰能力更强的前级滤波电路,则可以有效抑制待测信号伴随的噪声,提高了DLIA的可靠性[67]。

而在互相关检测算法层次,采用双相PSD代替单相PSD的设计方式,不仅可以有效避免相位差带来的干扰,同时也能够提高DLIA的相位分辨率[12];现有DLIA多采用降采样滤波器、CIC滤波器等快速滤波结构,对于优化DLIA的时间常数具有重要作用。

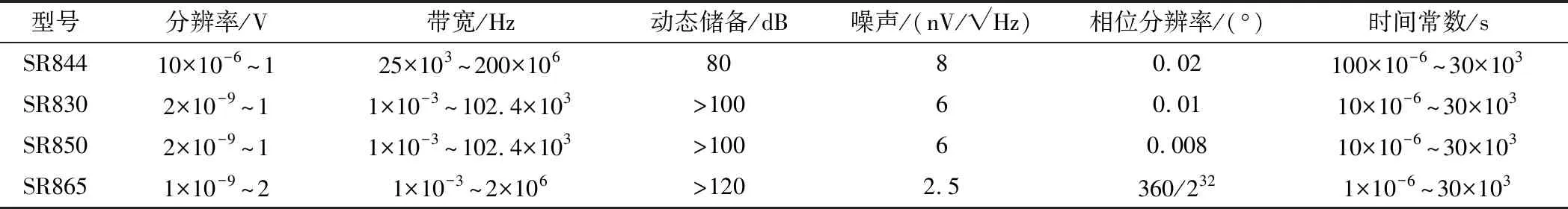

以美国SRS公司生产的系列数字锁相放大器为样本,概括了该系列数字锁相放大器的分辨率、带宽、动态储备等关键参数指标的演进过程,如表1所示。由表1可知,新型数字锁相放大器较以往产品而言,其分辨率、带宽、动态储备与相位分辨率均得到明显提高,噪声得到有效抑制,时间常数得到极大优化。

表1 数字锁相放大器关键参数指标演进

注:表中型号由上到下按时间先后顺序排列

此外,进一步提高DLIA的性能一直是微弱信号检测领域研究的热点,研究方向主要涉及动态信号检测、性价比提高、便携化检测、参考信号频率自跟踪以及相关参数优化等方面。通过对比近10年内有关DLIA的文献资料,发现现代检测活动中仍存在多种问题。基于此,笔者分析认为DLIA具备以下3个发展趋势。

① 提高动态信号检测能力:动态信号的实时性检测是现代检测系统的一个重点。目前鲜有实时性令人满意的DLIA,该问题矛盾点在于DLIA的积分时间与其滤波效果具有互斥性。若要提高实时性,则要减少积分时间,然而积分时间的减少会降低滤波效果。因此,在保持滤波效果不变的情况下,设法减少积分时间常数、提高DLIA的动态测量能力是DLIA发展、创新的一个重要方向。

② 提高DLIA动态储备:通常待测信号的幅值极其微小,需要引入前置放大电路对待测信号进行放大,但其背景噪声也会一同放大,从而造成放大电路的过载;较小的放大倍率则会导致待测信号无法达到DLIA的检测范围。因此,设法提高DLIA的动态储备,亦或在前置放大电路中有效的滤除噪声,是DLIA发展、创新的一个重要方向。

③ DLIA参考信号频率自跟踪:动态变化的待测信号通常不仅伴有高斯白噪声,同时还会掺杂其他频率的干扰信号,且干扰信号幅值远大于待测信号。现有文献中的DLIA频率自跟踪方案具有很大的局限性,即当待测信号伴有较大幅值干扰信号时,现有的检测方案很难检测出目标信号。因此,针对动态变化的待测信号检测问题,设法实现DLIA参考自跟踪,是其发展的一个研究重点。

除此之外,DLIA性价比的提高、便捷化发展与相关参数的优化也是未来的发展方向,但目前针对这些问题的文献较多,发展速度较快,将来会出现性能饱和。相反,DLIA动态信号检测等三个方向文献较少,研究意义相对较大。