基于ARM的分布式测试系统时钟同步研究及实现

王 旭,陈 晔,2,郑 宾,2

(1.中北大学 电气与控制工程学院,太原 030051;2.中北大学 电子测试技术国家重点实验室,太原 030051)

随着测试技术的发展,单一独立测试设备已不能满足现代测试要求,测试任务大多需要将不同测试设备连接起来构成分布式测试系统才能完成。而对于分布式测试系统来说,时间同步是保证数据有效的重要前提。若各测试节点或测试子系统的时间同步精度不足,即使得到了测试数据,也无法对测试结果(包括速度,压力,加速度等)进行准确的分析。国内外许多专家学者针对此问题进行了大量研究和探索,如:文献[2,5]研究了通过软件实现PTP时钟同步的方法。文献[3,8]等进行了基于Cortex-A8的LXI触发盒的软件和硬件开发。目前,该研究方向存在的不足和问题在于:对于分布式测试系统时钟同步和同步触发技术而言,仍停留在理论阶段,未能有效的将理论应用于实际测试系统,并且上述提到的LXI 触发盒技术在测试系统中并不通用,测试系统可以由不同的测试仪器构成,需要具有不同的触发模式和功能。针对上述存在的问题,本文采用PTP精密时间协议通过基于ARM(STM32F407)设计时钟同步与触发单元对该分布式测试系统进行同步。

1 设计思路及原理

1.1 整体设计思路

原分布式测试系统由若干个测试节点(每个测试节点即对应一个PXI仪器)组成,每相邻的两个测试节点之间相隔一定距离。原有测试系统的结构框图如图1。PXI仪器可以通过背板总线触发实现同步测试,但是由于PXI 设备之间的时钟同步精度不足,且触发精度随触发线长度的增加而降低,导致触发信号的精度无法满足高精度同步测试的需求,于是通过在原有测试系统结构的基础上改进,设计了基于ARM的时钟同步与触发单元为每个测试节点(每个测试节点对应一个通用测试仪器)提供高精度的时间基准信号,从而满足同步测试的需求。改进后的分布式测试系统整体架构框图如图2。

图1 原分布式测试系统结构框图

1.2 PTP协议简介

PTP协议(Precision Time Protocol),又称IEEE 1588协议,2002年由IEEE组织发布,并于2008年发布IEEE 1588V2标准。IEEE 1588实现时钟同步过程为[1]:

1)主时钟每隔一定时间(Sync_Interval)向从时钟发送一条Sync(同步)报文,主节点记录发送时间戳t1,但是t1不随Sync一起发送,从时钟在接收到Sync时记录下时间戳t2。

2)主时钟向从时钟发送一条Follow_up(跟随)报文,该报文内部含有(1)中发送Sync时记录的t1时间戳。

3)从时钟向主时钟发送Delay_Request(延迟请求)报文,从时钟端会记录报文发出时的时间戳t3。

4)主时钟在接收到延迟请求报文后记录当前时间戳t4,并且返回给从时钟Delay_Response(延迟请求响应报文),该报文内部包含时间戳t4,从时钟收到此报文后,利用得到的t1,t2,t3,t4计算得到它和主时钟的时间延迟[1],至此,一个同步周期结束。具体同步流程原理简图如图3。

图2 改进后分布式测试系统整体架构框图

图3 主从时钟同步流程原理简图

同步计算过程包括延迟值(Delay)计算和偏移值(Offset)计算,延迟值为主从节点之间的报文传输延迟的平均值,偏移值为主从节点之间的时间偏差[2]。计算公式如下:

(1)

(2)

根据式(2)即可得到主从时钟偏差。

根据IEEE 1588同步过程可知,决定时钟同步精度的关键在于时间戳的获取。现有的获取时间戳的方式有以下3种:

1)在网络层获取,这种方式是通过设置Linux内核中的时间选项为SO_TIMESTAMPNS从而得到报文到达网络驱动层的精确时间,但实现的同步精度较差(最高达到10微秒级)。

2)在数据链路层(MAC)通过硬件获取时间戳,该种方式需要借助支持PTP协议的MCU芯片完成,例如:通过STM32F407 ARM芯片实现亚微秒量级的同步,该种设计优点是通用性较强。

3)在PHY物理层获取,利用支持PTP协议的PHY芯片当接收到PTP事件报文时芯片会自动对时间戳进行标记[3]。该种方式获取的时间戳精度理论上可以达到纳秒级,但该种设计难度较大,并且增加设计成本。本文的设计采用基于在MAC层上获取时间戳。

2 系统设计

本设计基于对ARM的软硬件设计实现主从节点之间的同步。

2.1 硬件系统

硬件系统的设计主要分为以下几个模块:电源/复位模块,串口模块,JTAG模块,以太网通信模块等。

而以太网通信模块为整个硬件系统设计的核心,采用STM32F407 ARM芯片+LAN8720(普通以太网PHY芯片)组合实现以太网应用。由于STM32F407芯片内部集成MAC,则LAN8720(PHY芯片)可以直接和MCU相连。两者之间通过RMII(简化媒体独立接口)进行通信。接口设计电路简图如图4。

图4 以太网硬件接口设计电路简图

下面简要介绍下STM32的PTP特性。其内部集成的MAC能实现时间戳的获取功能,支持发送帧和接受帧时间戳,主要特性包括以下两个方面:

1)更新PTP时间。STM32使用 PTP 输入参考时钟 HCLK 更新64位PTP时间[4]。

2)捕获时间戳。当对STM32使能IEEE1588功能时,MAC通过识别报文的起始帧界定符SFD从而捕获当前时间戳,以太网硬件驱动程序将对报头进行解析,以区分出普通报文和PTP事件报文[5]。

2.2 系统软件设计

2.2.1系统软件架构

系统软件架构如图5所示。整个软件设计的关键是PTP应用层软件(PTP协议的实现),通过交换PTP报文信息实现,而PTP协议报文使用UDP协议进行封装和传输。UDP协议的实现需要TCP/IP协议栈。所以首先需要进行网络协议栈的移植。本设计选用LwIP协议栈进行移植,以实现数据包传输功能。CMSIS-RTOS实时操作系统负责任务的切换和调度。标准外设驱动提供GPIO、定时器和串口等基本外设的驱动,以太网驱动提供以太网硬件设备的驱动。以太网驱动程序采用ST公司提供的Eth_Driver库文件。标准外设驱动程序使用ST提供的Stm_std库文件[6]。

图5 系统软件架构

2.2.2CMSIS-RTOS实时操作系统移植和LwIP协议栈移植

CMSIS-RTOS针对RTX实时操作系统的内核进行封装,并演变为Keil的一个组件,因此使用起来很简便,具体移植工作主要分为两部分。

1)添加内核文件:包含文件RTX_HAL和RTX_Kernel,分别用于设置RTX接口和内核。

2)配置RTX:通过RTX_Conf_CM.c对RTX进行配置,本设计根据所使用的主控芯片特性进行设置,配置操作系统主频为168 MHz,设置系统时钟节拍周期为1 000 μs,同时系统使能特权级模式[7]。

LwIP协议栈是一种轻型TCP/IP协议栈。其源码内容包含3部分:doc(协议栈说明文档),src(socket接口函数,LwIP内核源码以及相关的头文件),test(LwIP的测试代码)。而移植协议栈时,需要修改系统文件以适配操作系统。

2.2.3以太网硬件驱动实现

以太网硬件驱动函数具体需要实现的功能及函数如下:

1)网卡初始化函数:low_level_init(),该函数实现对网卡结构体netif中相关字段的初始化操作,以建立稳定的物理链路并建立接收线程[8]。

2)网络数据发送函数low_level_output(),该函数的作用是将LwIP协议栈按网络报文要求封装好的数据报文通过网卡发送出去。

3)数据提取函数low_level_input(),该函数的作用是从网卡中提取接收到的网络数据,并将数据复制封装在pbuf中,并返回pbuf结构体指针。

4)PTP时钟偏差函数ETH_PTPTime_UpdateOffset(),该函数实现从时钟对主时钟时钟偏差的调节。

2.2.4基于PTP协议的时钟同步应用层软件设计

1)时钟同步软件架构。时钟同步软件的总体框架如图6所示。来自其他PTP时钟的报文通过UDP接口传递给PTP协议引擎进行处理。PTP协议引擎将在设定端口接收和发送报文。MAC在接收到报文后对数据包进行解封,以提取有用信息。通过运行最佳主时钟算法决定本地时钟状态[9]。若本地时钟为主时钟,则会向局域网内发送Announce报文,和其他的外部时钟数据集进行比较。若本地时钟为从时钟,则通过运行本地时钟调节算法,最终达到和主时钟之间的同步。

图6 时钟同步软件总体框架

2)最佳主时钟算法。最佳主时钟算法由bmc.c实现。它是判别同一PTP域内所有时钟主从等级的一种算法。通过广播Announce报文,比较本地时钟和外部时钟的数据集,从而得出局域网内的主时钟,并且在网络发生变化时,该算法能够自动运行,并及时更新PTP域内的主时钟,使其他从时钟与主时钟实现同步。

3)IEEE 1588协议引擎。IEEE 1588协议引擎主要由protocol.c实现。该代码主要运行PTP协议状态机,完成协议端口状态之间的正确转换,核心函数为protocol()[10]。

PTP协议状态机的运行过程:首先各个时钟端口上电后进行初始化,然后同一PTP域内的时钟运行BMC算法,程序根据运行结果(端口状态)执行相关操作。

4)时间戳获取。PTP协议的关键在于时间戳的获取。STM32F407的MAC支持以太网帧时间戳,每个帧在发送或接收状态下都会对应32位秒值时间戳和32位纳秒值时间戳[11]。

5)IEEE1588系统时间校准。IEEE1588系统时间校准主要通过粗调和精调两种方式进行调节。粗调即把初始值或时间偏移值写入时间戳更新寄存器[12]。校准时通过将计算得到的offset值写入时间戳更新寄存器,然后根据偏移量的正负进而对系统时间进行加减。使用精调即调节从时钟的频率,消除由于频率漂移带来的时钟抖动,计算并校准从时钟频率漂移的具体算法如下[13]:

① 在MSTime(n)时刻,主时钟向从时钟发送Sync报文,从时钟在本地时钟MSTime(n)时刻接收到该报文,假设主时钟到从时钟之间的网络链路延迟为Delay(n),则主时钟对应从时钟接收Sync报文的时间为

MCTime(n)=MSTime(n)+Delay(n)

(3)

② 当前同步周期的主时钟计数数目为

MCount(n)=MCTime(n)-MCTime(n-1)

(4)

③ 当前同步周期的从时钟计数数目为

SCount(n)=SCTime(n)-SCTime(n-1)

(5)

④ 当前同步周期的主从时钟计数差值的计算公式如下:

ClockDiffCount(n)=MCount(n)-SCount(n)

(6)

⑤ 从时钟的分频系数FreqScaleFactor(n)的计算公式如下:

(7)

通过之前设定主时钟时间戳加数寄存器的值,根据式(7),可以计算出从时钟时间戳加数寄存器的值。该算法在粗调的基础上,进一步减小主从时钟偏差。

2.3 分布式测试系统同步触发

由于在分布式测试系统中,各被测物理量的测试及采集时间不同步,因此各测试单元的触发信号的精确性显得尤为重要。在上述实现时钟同步的基础上通过编写上位机软件,在计算机上运行控制管理功能客户端软件,获取时钟单元的状态信息并对时钟单元的触发功能进行设置。本设计实现外部触发捕获,延时触发输出,定时触发输出功能。

外部触发信号捕获关键在于对脉冲宽度的测量以排除其他信号误触发,并提供外部触发信号抵达时准确的时间戳,以满足将分布式测试设备采集数据相互关联的需求[14]。

对应的软件设计流程如下:使能外部触发捕获功能后,对应的输入信号通道开始检测触发信号的上升沿,检测到上升沿则获取此时的PTP时间戳external_timestamp,启动计数器对脉冲信号宽度进行测量,当检测到触发信号的下降沿时,则计数器停止工作。通过计算脉冲宽度,判断信号是否有效。若返回值为TRUE,则将external_timestamp赋值给valid_timestamp,并保存供上位机调取,否则直接丢弃,继续检测触发信号。

该延时触发功能需在一个激励信号的触发下启动,使用同步后的PTP时间可以准确实现延时触发输出。

设计流程如下:设置延时触发时间后,新建PTP时钟读取线程,然后在输入通道检测触发信号,当检测到触发信号之后,PTP时钟读取线程获取当前PTP时间PTP_timestamp,根据设置的延时触发时间计算预定触发时间trigger_time,到达触发时间时,输出触发信号。

定时触发设计的目的是用于实现在某一特定时刻同时输出脉冲信号使测试节点内的测试设备实现同步测试。

设计流程如下:首先设置触发时间,然后新建PTP时钟读取线程,判断是否到达预设置的触发时间,若达到触发时间,则输出触发信号并kill当前进程,反之,则一直等待延迟时间。

3 时钟同步测试

3.1 两时钟节点网线直连测试

首先,为排除网络不对称对对时精度的影响,采用网线将两个时钟节点(LAN口)相连,从时钟端通过串口打印与主时钟的实时偏差。

在此实验中,分别设置单个同步周期时间为4 s,2 s,1 s。待时钟运行稳定后,使用串口实时打印时钟偏差,测试结果如图7所示。数据统计分析如表1所示。

图7 两时钟节点网线直连测试结果

表1 两时钟节点网线直连测试数据统计分析

时钟同步周期/s同步周期数绝对偏差平均值/ns最大正偏移/ns最大负偏移/ns4500301595-5622500221498-3521500176389-244

3.2 两时钟节点交换机互连测试

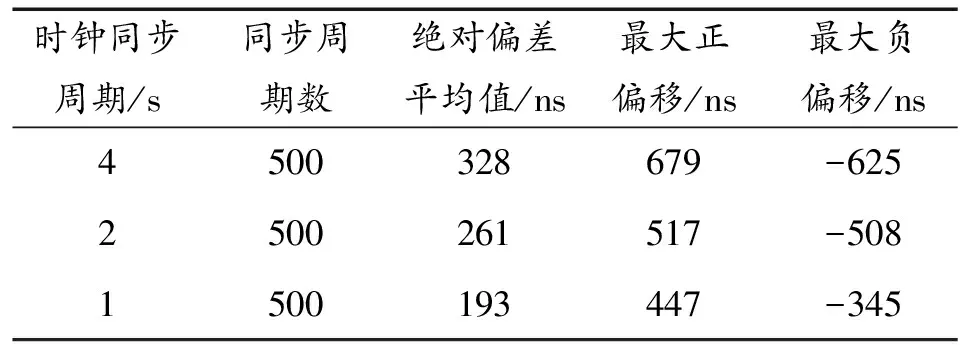

将两个时钟同步单元通过网线连入交换机的LAN口,并且将计算机的网口也连入交换机,设置计算机的本地连接为DHCP,然后从时钟端通过串口打印与主时钟的实时偏差。本实验同样分三次进行,分别设置单个同步周期时间为4 s,2 s,1 s。测试结果如图8所示。测试数据统计分析如表2所示。

图8 两时钟节点交换机相连测试结果

表2 两时钟节点交换机相连测试数据统计

时钟同步周期/s同步周期数绝对偏差平均值/ns最大正偏移/ns最大负偏移/ns4500328679-6252500261517-5081500193447-345

对比表1和表2,可以得出:当同步周期越短,同步后的主从偏差则越小;当同步周期设置相同的情况下,使用网络元件(路由器或交换机)会导致网络链路不对称,从而导致同步精度下降。

3.3 外部触发捕获

每个时钟单元设计了外部触发输入捕获口(IO口),能够检测外部触发信号,并记录下触发信号到达IO口的时间。此次实验,将两时钟节点通过交换机组网,等主从时钟关系建立并运行一段时间后,向各时钟节点的外部输入捕获通道输入触发信号,其中一个主时钟作为PTP时间基准,另一个从时钟通过主时钟进行校准,当输入通道在检测到对应的触发信号后,会自动记录到达IO口的时间值,并通过串口打印。测试结果如图9所示。其中,左边的表示主时钟接收触发信号后输出的时间戳,右边的表示同步后的从时钟接收触发信号后输出的时间戳,由数据可见,两者的时间差小于200 ns。

图9 外部触发测试结果

3.4 延时/定时触发输出

每个时钟同步单元均设计有延时/定时触发输出口,组网方式即将3个时钟同步单元接入交换机,并将计算机通过网口连入交换机。延时触发测试即通过将触发信号源接入从时钟输入端和示波器通道CH3,在计算机客户端软件中设置延时时间,待从时钟检测到符号要求的信号后,延迟一定时间通过触发输出口连接示波器的CH1通道。测试结果如图10所示。从实验结果可看出,触发信号延时200 ms后输出。

定时触发测试即将各时钟单元的触发输出口连接到示波器的CH1、CH2和CH3通道,当在计算机客户端软件中设置触发时间后,3个时钟同步单元在设定的时刻分别输出触发信号,测试结果如图11所示。由图11可知,3个时钟同步单元输出的触发信号之间时间间隔小于4 μs。

图10 延时触发测试结果

图11 定时触发测试结果

4 结论

本文提出的基于ARM设计时钟同步与触发单元对分布式测试系统进行同步,该方法通过引入PTP精密时间协议,分析其原理,然后基于ARM芯片及其相关的外围电路设计了时钟同步与触发单元,进而通过相关软件(时钟同步软件、TCP/IP协议栈移植、同步触发软件等)的设计,以及大量相关实验(两时钟节点网线直连,两节点交换机相连,外部触发捕获,延时触发输出,定时触发输出测试)表明组网的各时钟同步与触发单元实现了亚微秒级时钟同步精度和精确同步触发功能,该设计方法具有通用性,满足了一般分布式测试系统同步及触发功能要求。