一种基于XVC协议的FPGA调试模块设计

赵 赟

(中国船舶重工集团公司第七二三研究所,江苏 扬州 225101)

0 引 言

随着现代舰船电子设备的高度集成化,相关的分机板卡也越来越多。传统的USB-JTAG调试方式通信有效距离短,在舰船现场调试FPGA时,由于内外部环境复杂,调试人员可能需要攀爬,或者拥挤在狭小空间内,同时多块板卡对应单独的调试电缆,调试不同板卡还需要不停插拔,给调试工作带来极大不便。

针对此现象,本文基于Xilinx公司提出的XVC协议[1],设计了一种PTMP以太网调试模块,它通过高速背板同各个板卡连接,以Xilinx公司推出的Zynq7000芯片为处理芯片,以Realtek公司的RTL8305NB-CG交换芯片作为网络桥接,调试人员通过单个以太网口就能调试所有板卡,有效调试距离为100 m,还能支持多人在舰船不同地点同时调试,大大提升了舰船现场调试的便捷性和安全性。

1 模块原理框图设计

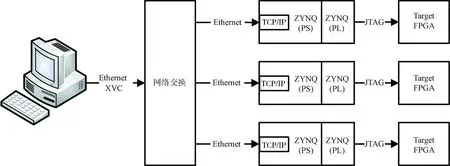

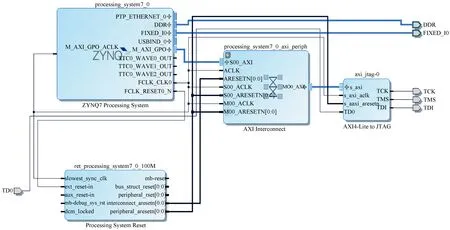

本模块系统原理框图如图1所示,调试电脑(PC)通过以太网和网络交换芯片相连,网络交换芯片将数据包分发到各个Zynq7000芯片,Zynq7000的处理系统(PS)部分接收到调试PC的以太网数据包后通过AXI4-Lite总线发送到可编程逻辑(PL)部分,PL部分将其解析并转化为联合测试工作组(JTAG)时序信号发送至需要调试的FPGA芯片,完成调试工作。

图1 系统原理框图

1.1 处理芯片选用

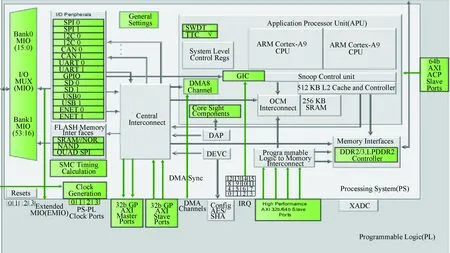

本文选用Zynq7000系列芯片作为模块的处理芯片,该芯片是Xilinx公司推出的片上系统(Soc)解决方案,该方案将ARM公司Cortex-A9和FPGA集成在一个芯片上,通过内部总线连接,从而让内部通信速度大大提升。它分为PS和PL两大部分,PS部分包括2个ARM Cortex-A9处理器、AXI总线、内部存储器、外部存储器及外设接口(这些外设包括USB总线、以太网接口、SD卡接口、I2C总线接口、CAN总线接口、串口、GPIO等等);而PL部分则包括Xilinx 7系列的FPGA[2],Zynq7000的具体架构如图2所示。

图2 Zynq7000芯片内部结构框图

1.2 AXI总线选用

Zynq7000作为Xilinx首款将ARM Cortex-A和7系列FPGA集成的Soc,其优势在于ARM处理器和FPGA之间的高速通信,而AXI(Advanced Extensible Interface)总线就是连接这两者的高速通道。AXI属于ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture),是一种高性能的片内总线,AMBA-AXI协议主要用用于高带宽、低延迟的系统设计,描述主从设备之间的数据传输方式[3]。主设备和从设备之间用握手信号建立连接。当从设备准备要接收数据时,会向主设备发送READY信号。而当主设备的数据准备好后,会发出和维持一个VALID信号,表示数据有效,VALID和READY信号都有效的时候,握手完成,主从设备之间开始传输数据。

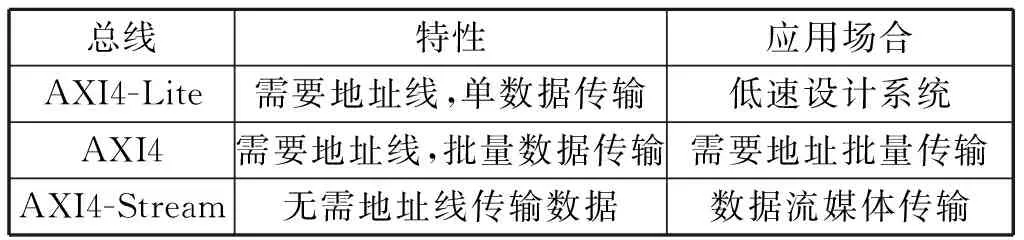

Zynq7 000支持AXI4-Lite、AXI4和AXI4-Stream 3种总线模式,表1列举了3种AXI总线的特性。

表1 3种AXI总线比较

本模块的设计需求是将以太网数据包转化为JTAG命令,用于调试和下载FPGA,属于低速应用,而 AXI-Lite总线结构简单,适合这种小批量、简单控制的场合,所以本模块使用AXI4-Lite总线来传输ARM和FPGA之间的数据。

1.3 网络交换设计

本模块为Zynq7000设计的以太网接口,为简化的千兆比特介质独立接口(RGMII),该接口由IEEE 802.3-2000定义,支持10/100/1 000 Mbps传输速率,同时采用4位数据接口,有效减少了芯片接口管脚数目,通过Zynq7000 PS部分设计了支持AXI4-Lite总线的以太网MAC架构[4]。

为了交换对应不同板卡的以太网数据包,本模块还在PC机和Zynq7000芯片设计了一个网络交换模块,该模块的核心芯片选用了Realtek公司的RTL8305NB-CG芯片,它有5个端口,每个端口有独立的媒体访问控制地址(MAC)和物理层接口(PHY),支持10/100 M以太网交换,从调试PC发送的以太网数据包会通过接入端口向所有端口广播,而对应的Zynq7000芯片收到广播信息后,会根据对应信息选择接收还是丢弃所收到的以太网数据包[5],从而完成本模块设计的PTMP功能。

2 模块系统软件设计

2.1 XVC协议

本模块软件是基于Xilinx XVC协议设计,XVC协议是Xilinx公司推出的基于TCP/IP的虚拟线缆协议,允许用户不使用传统的USB线缆,而是通过以太网来远程访问FPGA的JTAG接口并对其进行调试,支持多种平台。

2.2 Lwip协议

本模块的网络硬件接口为RGMII接口,同时通过Lwip协议实现以太网连接,Lwip协议是一种TCP/IP协议的小型化实现,最初由Adam Dunkels在瑞典计算机科学研究所的计算机和网络架构(CNA)实验室编写。它实现的重点是在保持TCP/IP协议的主要功能情况下同时减少硬件RAM使用。这使得Lwip适用于小容量RAM或者ROM的嵌入式系统。现在Lwip已被移植到多个平台和操作系统,无需底层操作系统都可以运行[6]。

Zynq7000通过Xilinx Vivado软件的软件开发工具(SDK)来实现Lwip协议,在Vivado软件中通过一个知识产权(IP)核集成工具完成基于Zynq的硬件平台设计,在搭建好硬件平台后直接发送到SDK,然后再通过该平台加载软件程序。

2.3 系统软件流程图

本文基于Zynq7000芯片设计的软件流程图如图3所示。

Processing_system7_0k模块为Zynq7000的PS部分,首先负责所有外设驱动编写,包括以太网、串口、DDR等,在设备启动后首先将外设初始化,然后开始通过RGMII网口接收由调试PC发送的XVC协议以太网数据包,该数据包主要由以下3种命令组成:

l getinfo:

l shift:[number of bits][TMS vector][TDI vector]

l settck:[period in nanoseconds]

其中,getinfo命令检索XVC服务的版本和TMS及TDI信号位移的最大指针长度,目前Xilinx使用的XVC服务为v1.0,TMS和TDI的最大指针长度和软件应用定义的缓存深度有关,本模块定义的最大长度为2 048,所以getinfo命令返回的字符串为xvcServer_v1.0∶2048 。

shift命令是XVC协议的主要命令,它由三部分组成,共6个字节,前4个字节指示TMS和TDI的指针长度,后面2个字节则是发送的TMS和TDI数据,该指令会返回同TMS指针向量同样长度的TDO指针,代表从JTAG接口返回的全部TDO数据[7]。

图3 系统软件流程图

settck命令主要用来设置TCK信号的时钟周期,基本单位为ns,具体通过ASCII码来定义。比如十进制100 对应的ASCII字符为D,将settck命令值设为D(即设置TCK信号的周期为100ns[8])。

另外2个模块rst_processing_system7_0_100 M负责软件模块的复位,而processing_system7_0_axi_periph模块则在解析PC机通过XVC服务发送的以太网包后,将解析过的命令通过AXI4-Lite总线写入PL部分的寄存器,然后通过axi_jtag_0模块转换为JTAG时序连接到目标FPGA,从而完成调试。

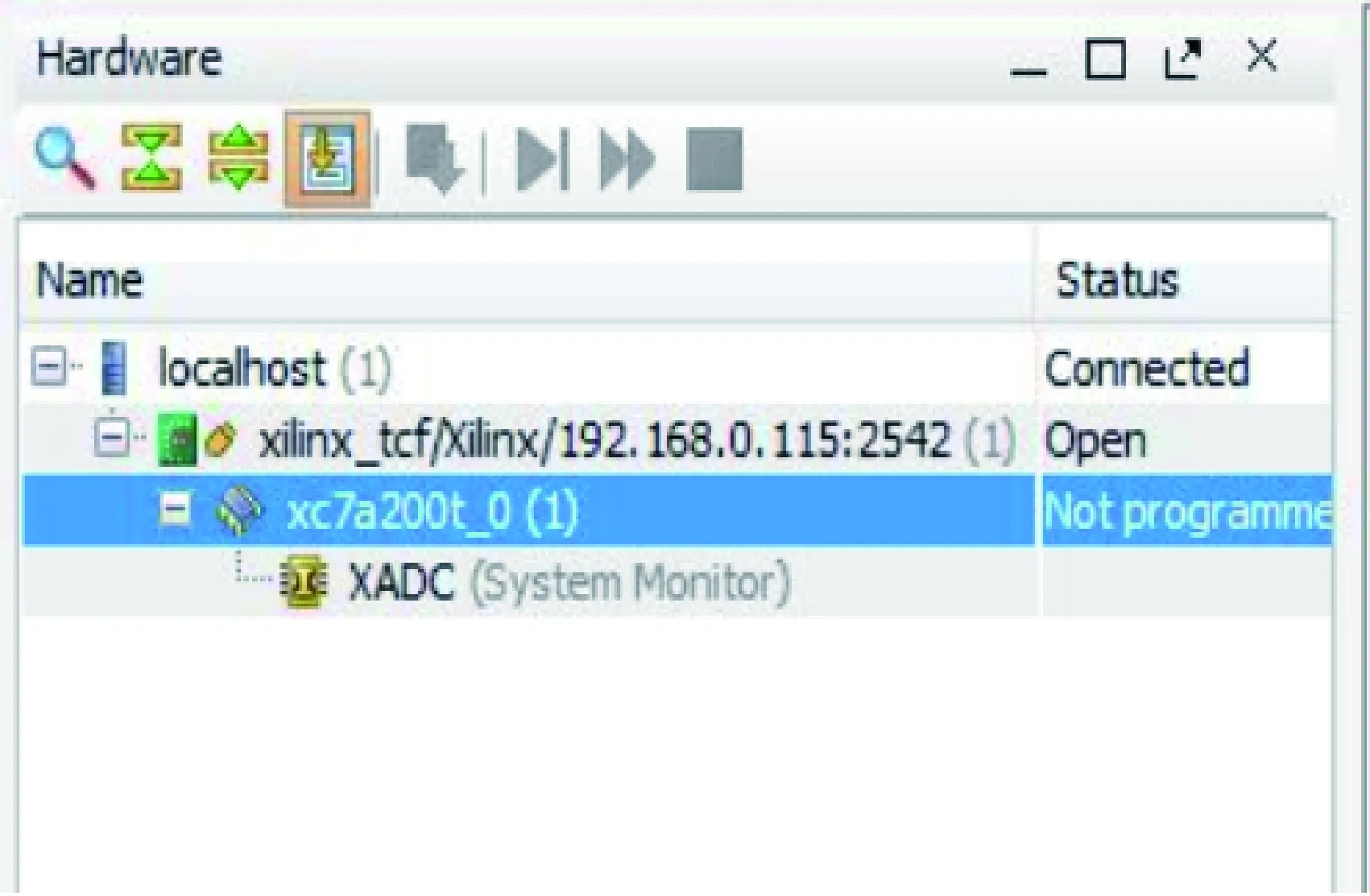

3 调试测试

本文的测试环境软件为Xilinx Vivado软件,打开Vivado软件进入硬件管理界面,在TCL控制台输入指令,连接目标FPGA对应的IP地址,连接成功后开始对目标FPGA进行下载调试。如图4所示,通过Vivado软件的现场测试,将一个5 M的bit文件在线加载进FPGA所需时间为20 s左右,而通过Bpi模式烧录mcs文件进入对应Flash时间大约为25 min。和传统JTAG相比,调试下载速度基本一致,但对于现实设备上的板卡调试而言,该方法更加灵活方便。

图4 目标FPGA连接成功

4 结束语

在本模块中,调试PC通过网络交换芯片,利用单网口可以访问所有板卡对应的Zynq7000芯片,通过XVC协议将以太网数据包解析为JTAG命令,从而完成调试板载FPGA的目的。在实际设备应用中,仅需要一个交换芯片模块,而将Zynq7000芯片集成在各块板卡上,用来代替传统的上电控制芯片。