基于忆阻器的神经突触的设计

高 畅,李 彤,李 泉,王铁钢,范其香,倪晓昌

(1.天津职业技术师范大学电子工程学院,天津 300222;2.天津职业技术师范大学机械工程学院,天津 300222)

忆阻器是一个具有记忆功能的纳米级器件[1],它自问世以来就被应用于许多领域,如超高热度的人工智能、神经网络系统、存储器等,但是基于忆阻器对神经突触模拟的研究较少,特别是在神经网路电路的仿真及硬件的实现方面,因此关于忆阻器对神经突触的模拟是科学家们向往的研究方向[2-3]。在生物学中,神经系统具有高效敏捷的处理能力,这是源于突触在神经元之间进行信息传递的作用[4]。忆阻器是与神经突触非常接近的仿生器件,忆阻器的掺杂层相当于突触前膜,不完全掺杂层相当于突触后膜,中间的交换层可以视为突触间隙。当忆阻器的外加电压变化时,产生的磁场会使掺杂层的氧离子发生移动,导致掺杂层与不完全掺杂层所含的氧空位的数量发生变化,从而使忆阻器的电阻随之变化。在神经网络系统中,若神经元受到刺激,神经递质会传递给与其相连的后一个神经元,导致后一个神经元的状态发生改变;若断电忆阻器的阻值仍保持不变,神经递质最后也会保留下来[5-6]。过去模拟一个神经突触的功能需使用多个电容和晶体管来实现,现在仅需使用一个忆阻器就可以进行神经突触的模拟。忆阻器的出现不仅减少了功耗,降低了成本,优化了电路的设计,同时还提高了实验效果[7]。

近几年,各研究团队根据忆阻器的特点建立各种模型,并根据模型建立相应的神经网络电路,如2017年,西南大学的冯广[8]对于忆阻值漂移现象提出了利用双极性脉冲的对称性减少忆阻器因离子漂移产生的误差。2018年,东北师范大学的林亚[9]提出了一种基于肖特基势垒宽度调节的忆阻模型,通过调节耗尽层区的宽度,从而能够连续地调节忆阻器的阻值。但是,目前关于利用忆阻器实物构建电路的报道还很少。本文建立忆阻器的SPICE 模型,将其与其他器件连接,构建突触电路并进行仿真,利用NiO 忆阻器实物进行硬件电路的连接并验证突触电路的特性。

1 忆阻器模型的建立及NiO忆阻器的制备

1.1 电路模型的建立及在PSPICE中的描述

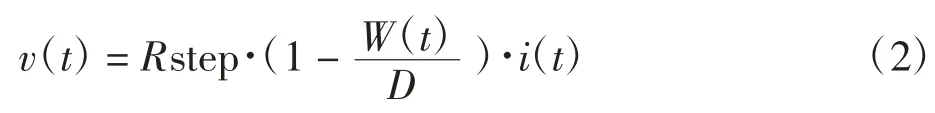

二氧化钛双层忆阻器模型是由惠普公司研发的,掺杂层是掺杂氧空位的二氧化钛层,即缺氧二氧化钛层,电阻较小为RON;不完全掺杂层是无缺氧二氧化钛层,电阻较大为ROFF。掺杂层的线性长度用W 表示,忆阻器的长度用D 表示。忆阻器两端电压计算公式为:

忆阻器的SPICE 模型原理图如图1所示。

图1 忆阻器SPICE 模型原理图

图1中涉及的电压源均由电压控制,电流源均由电流控制。电阻Rser 相当于式(1)中的RON,阻值为10 Ω,因阻值较小所以在串联电路中可以忽略不计;电阻 Rstep 相当于式(1)中的 ROFF,阻值为 1 kΩ,电流源Fcopy 为忆阻器的电流,流经电阻Rstep 后可以得到Rstep 两端的电压,该电压作为输入端对电压源Eres 进行反馈,这样阻值固定的ROFF与一个可控电压源串联,则能得到一个阻值可以由外部电压控制的电阻,电阻Rstep两端电压为:

电阻Rsp 阻值无限大,这里采用1 000 MΩ 的电阻,因中间连接的电阻Rser 阻值很小,电流源Fcopy与电流源Gmem 上的电流值几乎相同;电容Cmem 与电流源Gmem 连接组成一个积分器,对该电流进行积分可得电容Cmem 两端的电压值[10-11],电压源Ecopy也表示该电压,作为电压源Eres 的另一个输入端,由此构建的模型使SPICE 的仿真更加稳定。

采用PSPICE 语言对忆阻器的物理模型进行描述,忆阻器作为一种新型器件,作为子电路连接于电路中,定义为<.SUBCKT 子电路名 节点 N1 N2 N3...>[12-16]。忆阻器电路构建程序如下:

.SUBCKT memristor1 1 2 6

Eres 1 9 POLY(2)(8,0)(10,0)0 0 0 0 1

Vsense 9 4 DC 0

Fcopy 0 8 Vsense 1

Rstep 8 0 1K

Rser 2 4 10

Gmem 6 0 VALUE={I(Vsense)*max(v(6,0)*(1-v(6,0)),0)}

Cmem 6 0 50nF

Ecpy 10 0 VALUE={min(max(v(6,0),0),1)}

Rsp 6 0 1000Meg

.ENDS

在PSPICE 软件中对其进行仿真,得到忆阻器电流与电压之间的关系滞回曲线如图2所示。

图2 滞回曲线

1.2 NiO忆阻器的制备

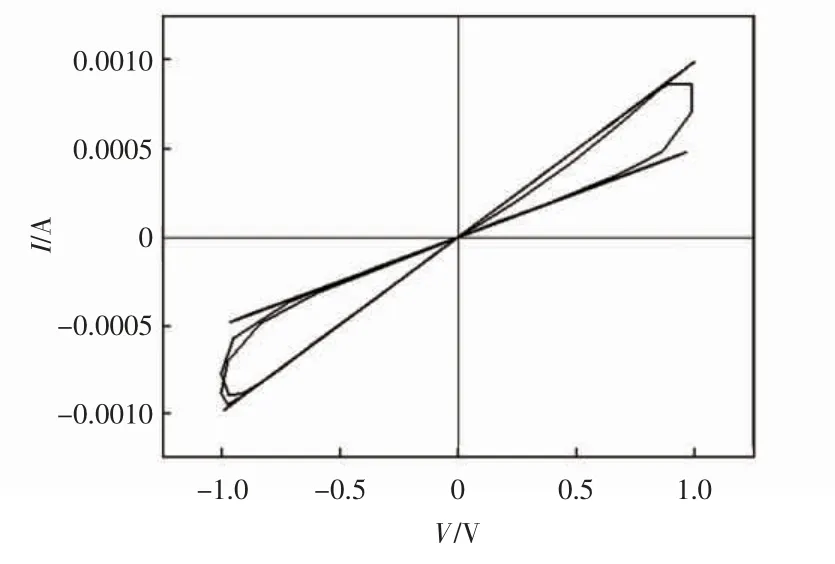

在实验室中,利用磁控溅射方法在Si 衬底上制备NiO 忆阻器薄膜,溅射功率为150 W,工作气压为2 Pa,沉积时间为1 h,然后在400 ℃条件下退火30 min,得到NiO 忆阻器实物。实验发现该电阻呈现出电阻随着电压变化也发生变化,得到了典型的带有回环的V-I特性曲线,即为忆阻器实物。NiO 薄膜电学特性曲线如图3所示。

图3 NiO薄膜电学特性曲线

2 忆阻器的神经突触的建立及仿真

2.1 忆阻器的神经突触的建立

1983年,Henry Markram 提出突触可塑性STDP 规则,即脉冲时间依赖可塑性规则[17-19]。他指出,神经突触兴奋或抑制强度取决于前后神经元被激励的先后顺序。若前神经元先活动,后神经元接收到前神经元传来的信号后再活动,则会增加前后两神经元之间的衔接水平,称为长时程增强(LTP)效应;若后神经元首先产生活动然后再从前神经元那里接收信号,这将削弱前后两神经元之间的衔接水平,称为长时程抑制(LTD)效应。忆阻器、外围电路和突触权重调整模块组合的突触装置如图4所示[20-21]。

图4 突触装置

最初的SD 和SP 均为低电平,状态节点SD 经过非门I3 变为高电平,当突触前神经元信号PRE 先输入权值增强电路时,与非门I4 输出低电平,与之相连的晶体管MP1 导通,电压V2 对电容C1 充电使其上升为高电平,因此只要有脉冲输入就会一直保持高电平,与电容C1 相连的状态节点SP 也上升为高电平。在权值抑制电路中高电平的SP 经过非门I7 变为低电平,所以与非门I8 必定输出高电平,晶体管MP2断开,突触权值抑制电路不工作。当停止PRE 脉冲信号的输入时,电容C1 最先放电,经过2 个晶体管MN2 和MN1。放电过程中突触后神经元信号POST到达电路,晶体管MN3 导通,使电容C1 通过晶体管MN3 对电容C2 进行充电,电容C1 与电容C2 迅速变为相同的电压。电路中的反相器I1 和I2 均有一定的翻转电压,在此充电过程中,当电容C2 上的电压比反相器I1 的翻转电压高时,反相器I2 则会输出高电平。当停止POST 脉冲信号的输入时,晶体管MN3 断开,电容C1 则停止对电容C2 充电,电容C2 上的电压逐渐降低,当电容C2 上的电压比反相器I1 翻转电压低时,反相器I2 则会输出低电平,经过一系列的过程,输出端则会输出相应宽度的LTP 脉冲。

当突触后神经元信号POST 先输入权值抑制电路时,与非门I8 输出低电平,与之相连的晶体管MP2 导通,电压V3 对电容C3 充电使其上升为高电平,因此只要有脉冲输入就一直保持高电平,与电容C1 相连的状态节点SD 也上升为高电平。在权值增强电路中高电平的SD 经过非门I3 变为低电平,所以与非门I4必定输出高电平,晶体管MP1 断开,突触权值增强,电路不工作。当停止POST 脉冲信号的输入时,电容C3最先放电,经过2 个晶体管MN4 和MN5。放电过程中突触后神经元信号PRE 到达电路,晶体管MN6 导通,使电容C3 经过晶体管MN6 对电容C4 进行充电,电容C3 与电容C4 迅速变为相同的电压。电路中的反相器I1 和I2 都有一定的翻转电压,充电过程中,当电容C4 上的电压比反相器I5 的翻转电压高时,反相器I6就会输出高电平。当停止PRE 脉冲信号的输入时,晶体管MN6 断开,电容C3 则停止对电容C4 的充电,电容C4 上的电压逐渐降低,当电容C4 上的电压比反相器I5 的翻转电压还低时,反相器I6 则会输出低电平,经过这一系列的过程,输出端则会输出相应宽度的LTD 脉冲。

权值增强电路和权值抑制电路不能同时进行操作,因为SD 和SP 这2 个状态节点会通过电压状态来控制电路。如果PRE 信号先输入,权值增强电路工作,高电平的SP 使权值抑制电路不工作,最终输出LTP信号;如果POST 信号先输入,权值抑制电路工作,高电平的SD 使权值增强电路不工作,最终输出LTD 信号。在LTP 和LTD 电路中,一个周期分为9 个时间段,电压V1~V9 对应周期T1~T9,且电路中的电压源V4、V5 的电压在各个时间段的变化是相同的。对于V4和V5的设定值如表1所示,其中LTP 前神经元刺激信号V4 的周期用(a)表示,后神经元刺激信号V5 的周期用(b)表示;LTD 后神经元刺激信号V5 的周期用(c)表示,前神经元刺激信号V4 的周期用(d)表示。

表1 V4和V5的设定值

2.2 基于忆阻器的神经突触的仿真

突触权值调整电路在不同PRE 和POST 信号间隔下的仿真如图5所示。

图5 突触权值调整电路在不同PRE 和POST 信号间隔下的仿真

在 LTP 和 LTD 电路中,LTP 输入电压为 V(LTP input),LTD 输入电压为 V(LTD input),SP 点电压为V(SP),SD 点电压为 V(SD),LTP 输出电压为 V(LTP output),LTD 输出电压为 V(LTD output)。从图5可知,仿真分为4 个时间段,在前2 个时间段中,第1 个是PRE 信号先到达,POST 信号间隔1 ms 后到达,节点SP 迅速上升为高电平,使得权值抑制电路不工作,权值增强电路产生12 ms 的LTP 脉冲;第2 个是PRE 信号到达,POST 信号间隔15 ms 到达,节点SP 又升为高电平,权值抑制电路仍不工作,权值增强电路产生11 ms 的LTP 脉冲。在后2 个时间段中,当第1 个POST 信号先到达,PRE 信号间隔1 ms 后到达,节点SD 迅速上升为高电平,使得权值增强电路不工作,权值抑制电路产生11 ms 的LTD 脉冲;第2 个POST 信号到达,PRE 信号间隔15 ms 后到达,节点SD 又升为高电平,权值增强电路仍不工作,权值抑制电路产生11 ms 的 LTD 脉冲。

3 神经突触硬件电路的实现

结合仿真电路及实验室制备NiO 忆阻器实物,搭建模拟神经突触实际电路,实际电路连接如图6所示。硬件主要有P 沟道场效应管、N 沟道场效应管、2 个74LS00与非门和4 个74LS04 反相器。电路板I 为长时程增强电路和长时程抑制电路,电路板II 用于连接忆阻器的外围电路,电路板III 为实验室制备的NiO 忆阻器。采用0.01 pF 的贴片电容,借助连接板连接到电路中。

图6 实际电路连接

在对电路板进行调试时,主要用到信号发生器、示波器和直流稳压电源。直流稳压电源分别设置为1 Vdc、5 Vdc、2.5 Vdc 和 0.1 Vdc。在进行周期脉冲激励信号波形的调试时,首先要对信号发生器的通道进行相应的设置:CH1 通道和CH2 通道都选择矩形波,周期设置为20 ms,占空比设置为0.048 82%,分别对应示波器的黄色和蓝色脉冲波形。然后对LTP 电路的输出点out1 进行测试,长时程增强模块LTP 输出波形如图7所示。

图7 长时程增强模块LTP 输出波形

示波器中out1 点输出波形与仿真过程中LTP 电路中out1 点输出波形(图5)大致相同。当前神经元收到激励信号产生活动时,导致长时程增强电路(LTP)工作,长时程抑制电路(LTD)不工作,SP 点产生放电效果,out1 输出端口产生相应波形。由于2 个模块为互补关系,一个工作,另一个则不工作,所以产生的波形相同,只是波形对应的周期不同。

通过上述仿真实验和硬件电路设计及实验结果可以看出,忆阻器可以很好地进行神经突触的模拟,结构简单的纳米级忆阻器与传统的CMOS 相比,减少了很多功耗,使电路更加简单。

4 结 语

本文基于物理公式,编写了电路描述程序,并绘制了忆阻器的SPICE 模型原理图。利用PSPICE 软件对忆阻器进行建模,并对电路进行仿真,验证LTP、LTD 模块在前后神经元激励顺序不同以及间隔时间不一的作用下,电容的充放电效果和LTP、LTD 模块的输出情况。仿真结果表明:该方法不仅解决了硬件繁琐、电路复杂的问题,还优化了电路的设计,使神经突触电路的仿真结果更加精准。同时,使神经网络的模式识别和关联存储等方面的优势更好地显现出来。