深亚微米CMOS环形放大器研究

裴志军,王雅欣,韩 蕾

(天津职业技术师范大学电子工程学院,天津 300222)

随着CMOS 技术的持续进步,工艺特征尺寸从微米、亚微米发展到深亚微米、超深亚微米和纳米,CMOS 模拟集成电路设计方法面临着愈来愈严峻的挑战。由于CMOS 技术工艺特征尺寸缩小的进步主要是针对高速数字集成电路的性能进行优化,这使得在深亚微米及以后CMOS 技术中,模拟集成电路的设计采用传统电路拓扑结构实现精确、有效的放大器变得越来越困难[1]。面对CMOS 技术节点的不断挑战,研究者们提出了各种解决方法,如数字校正、增益增强、输出摆幅增强等技术。但是,这些技术所采用的模拟放大器结构大多难于从CMOS 技术节点进步中受益,因而很难像数字集成电路那样随CMOS 工艺特征尺寸的缩小而获得性能上的改善[2]。随着CMOS 技术的不断发展,模拟放大器电路的设计也应充分利用先进CMOS 工艺技术其潜在的高性能优势。为此,深亚微米CMOS 模拟集成电路的设计方法,可以从高速低功耗的数字集成电路中进行有益的借鉴。近年来,在深亚微米CMOS 技术节点,出现了一种新型的放大器拓扑结构,称为环形放大器(ring amplifier,RAMP)[3]。环形放大器的结构与CMOS 环形震荡器类似,由具有反馈的三级CMOS 反相器构成。但与环形振荡器不同的是,其第二级反相器被分裂成2 个信号路径,且分别嵌入失调电压。另外,第三级反相器的2 个MOS 晶体管被偏置在亚阈值区以便能够获得最大输出级阻抗。由于具有类似于CMOS 环形振荡器的简单结构,CMOS 环形放大器可以较好适应CMOS 技术的发展,因此在深亚微米模拟放大器电路设计中特别具有吸引力。与传统模拟放大器结构相比较,CMOS 环形放大器具有诸多优点,如具有轨到轨输出摆幅的有效放大能力,功耗-延时积性能随CMOS 技术节点的进步而有效改善等。CMOS 环形放大器结构简单,也能够以低功耗获得高增益,从而在低功耗高能效应用中受到研究者的广泛关注[4]。为此,本文对CMOS 环形放大器的工作机理及相关设计技术进行分析探讨。

1 环形放大器工作机理分析

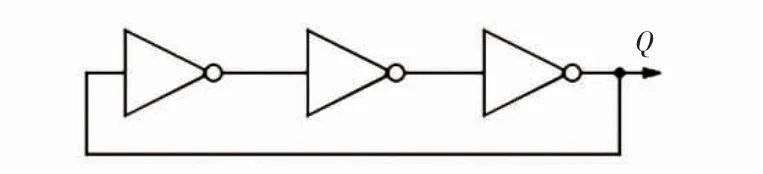

CMOS 集成电路中,由CMOS 反相器构成的环形震荡器的性能随CMOS 技术的进步而得到极大的改善,因而通常被工艺制造厂商用作表征特定CMOS 工艺技术的方法[5]。CMOS 环形放大器具有与环形振荡器相似的简单结构,因此也能够受益于CMOS 工艺技术的进步。一个三级CMOS 反相器构成的环形振荡器如图1所示。一种基本的CMOS 环形放大器结构如图2所示。

图1 三级CMOS 反相器构成的环形振荡器

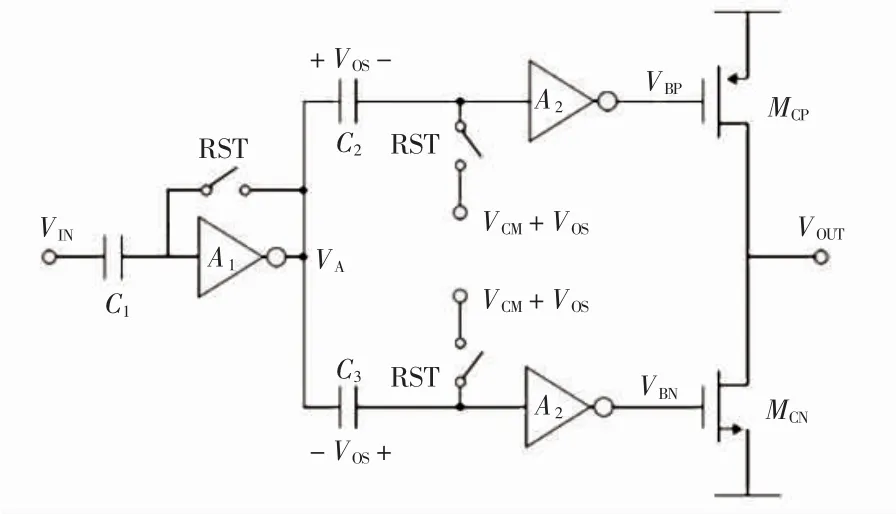

图2 基本的CMOS 环形放大器结构

由图2可知,环形放大器本质上是将环形震荡器分离成2 个信号路径,并且在每一个信号路径嵌入不同的失调电压,以便使输出级晶体管MCN和MCP偏置于非导通的亚阈值区,也称为死区(dead zone)。环形放大器输出到输入的反馈常采用开关电容电路,如果导致死区的失调电压足够大,则具有反馈闭环配置的环形放大器将经历转换、稳定和锁定死区3 个阶段过程,从而由内部反馈机理产生稳定,并能够将振荡器转换为放大器,对信号进行放大。

在图2中,通过电容C2和C3的存储,在环形放大器的第二级反相器之前嵌入失调电压VOS,从而产生相应的死区。当环形放大器稳定且锁定时工作于放大状态,与死区相对应的任何输入可以看作环形放大器的稳态解,并且与死区相应的输入还决定着环形放大器的整体精度[3],其中死区电压VDZ=2VOS。

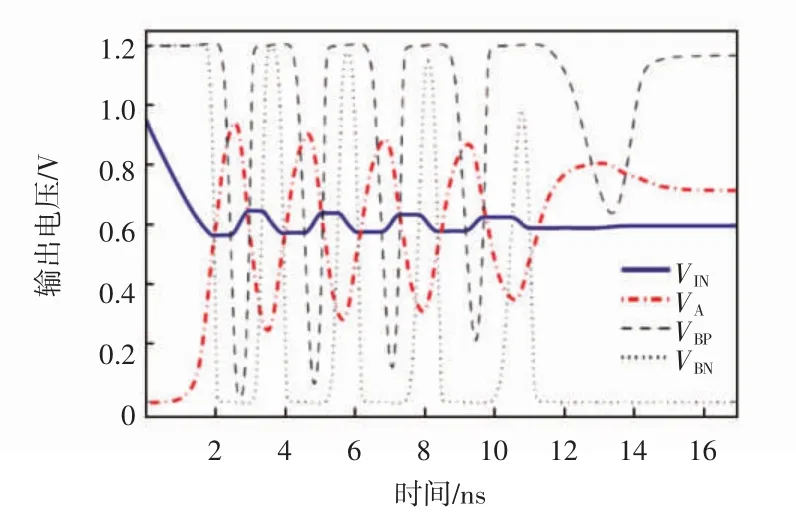

采用环形放大器进行放大时所经历的3 个工作阶段如图3所示。

图3 环形放大器的3 个工作阶段

其中,采用在输入端VIN处观测反馈信号的幅度,而输出端VOUT处的信号是VIN处信号的放大、移位。显然,在0 ns~2 ns 的初始阶段,环形放大器朝着死区方向快速转换。然后,在2 ns ~14 ns 期间,环形放大器围绕着死区震荡,并逐渐趋向于稳定。最终在约15 ns时,随着输出级晶体管MCP和MCN都截止,环形放大器到达一个死区内的稳态解且保持锁定。

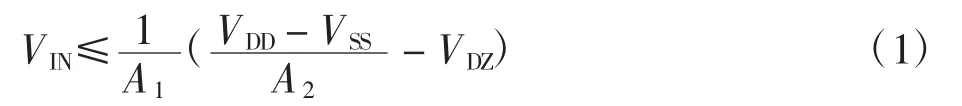

在初始转换阶段,环形放大器前二级的工作方式类似于双向比较器,根据输入信号的采样值相应地选择输出级的一个晶体管MCN或MCP来处理信号,于是所选择的输出级晶体管则作为偏置电流源对输出负载电容进行充电或放电,从而进行转换。当输入信号低于该双向比较器的参考阈值时,相应的晶体管偏置电流源则关断,转换阶段结束。但是,由于比较器存在时间延迟,将产生超过比较器阈值的一定量的过冲。因此,在初始转换阶段后,环形放大器将开始围绕着设置目标值震荡。此时,若不存在相应的死区,则这种环形放大结构在功能上与反相器构成的环形震荡器相同,将连续无限地震荡。然而,随着死区的逐渐增大,该环形放大器最终将到达稳定状态。如果将死区进一步增大,则稳定所要求的时间可以极大减小。在实际设计中,往往希望环形放大器能够在1 个或2个震荡周期内稳定。环形放大器的稳定过程,本质上是在每一个连续的震荡周期,施加于输出级晶体管MCN和MCP的过驱动电压峰值逐步减小,从图3可知,VBP和VBN的信号峰值幅度逐次变化情况。为了能够触发这种过驱动逐次减小效应,输入信号应满足下式:

式中:VIN为输入峰值-峰值幅度;A1、A2分别为第一、二级反相器的有效增益,具有负值;VDD为电源电压;VSS为参考地电压;VDZ为死区电压。

该过驱动逐次减小效应从概念上也可理解为环形放大器的输出端极点相应频率的动态调整。输出级的过驱动减小所引起的输出电流下降将导致环形放大器的输出阻抗增加,从而使得输出阻抗和负载电容构成的输出极点趋向更低频率。随着连续震荡周期中过驱动逐次减少效应的增强,输出极点逐次趋向于越来越低的频率。当环形放大器锁定在死区时,输出晶体管截止,输出阻抗将变得无穷大,则输出极点位于直流频率。

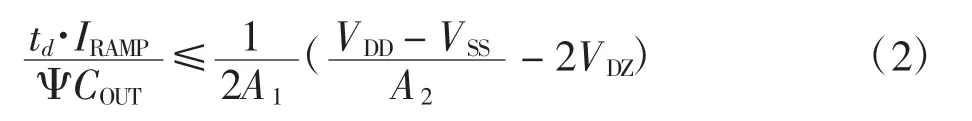

通过分析,环形放大器的稳定性准则可表示为[3]:

式中:td为延迟时间;COUT为输出负载电容;IRAMP为负载驱动电流;Ψ 为与过驱动相关的尺度因子。

从式(2)可以看出,环形放大器的设计在精度、速度和功耗之间存在着折中。为了增加速度,可以通过增大电流IRAMP来增加初始转换速率,然而这需要增加相应的死区电压VDZ,从而降低精度。减小稳定所要求的时间,td也可以增加速度,但相应的功耗将增加。相似地,若通过减小VDZ来增加精度,则必须相应地减小IRAMP而使速度降低或者减小td来增加相应功耗。在环形放大器工作过程中,反相器有效增益的动态调整能够有效改善速度、精度和功耗之间的设计折中。

在前文中将环形放大器的稳态条件考虑为输出级晶体管均完全截止,从而稳定锁定死区。然而,如果进一步考虑到上述输出极点的动态调整,环形放大器可以从输出极点的低频位置到直流的频率范围内稳定。实际上往往会存在一定的概率,环形放大器碰巧稳定在死区的边缘。如果这种情况发生,其中1 个输出级晶体管仍然有小量的电流而不截止。因此,除了2个输出级晶体管都截止的死区外,还存在着边界弱区(weak zone),使输出极点相应频率位置足够低而产生稳定。这种稳定的边界弱区的存在可以从输出电流IOUT相对于输入电压VIN的直流扫描分析中观察,死区附近的输入相关特性如图4所示。死区边界弱区的存在有助于改善对于环形放大器工作时的精度。

图4 死区附近的输入相关特性

2 CMOS环形放大器结构

在环形放大器设计中,虽然在电路结构的位置上如何嵌入产生死区的失调存在着多种选择,但图2中所示的方法具有诸多优点。首先,采用电容嵌入失调可以精确地设置产生死区的失调电压值。然后,通过在第二级反相器前嵌入失调易于获得稳定性。最后,在第一级增益后嵌入失调能够产生与较小输入相适应的死区,从而获得期望的精度,同时也能够使嵌入的失调足够大,以便于采用可调整参考电压源。基于CMOS 反相器,一个基本的CMOS 环形放大器结构如图5所示。

图5 基本的CMOS 环形放大器结构

与CMOS 环形震荡器不同,在CMOS 环形放大器中,第三级反相器的PMOS 晶体管MCP和NMOS 晶体管MCN的输入端信号路径被分离成2 个不同的信号路径。这使得输出级的上拉PMOS 晶体管和下拉NMOS晶体管能够被分别偏置为不同的直流偏压,因此使得输出级的2 个晶体管都可以工作在亚阈值区。将输出级晶体管偏置在亚阈值区不仅有益于减小电路功耗,而且对于闭环配置的环形放大器的稳定性也至关重要。该CMOS 环形放大器电路结构中,死区电压VDZ由嵌入直流偏压VRN和VRP确定。为了使环形放大器稳定,死区电压应满足:

式中:A2为第二级CMOS 反相器级的电压增益;VTN、VTP分别为输出级NMOS 和PMOS 晶体管的阈值电压。

除了失调直流偏置电压,对于环形放大器的稳定工作也应当考虑输入信号范围。为了使环形放大器稳定工作,如前所述,输入交流信号幅度应当满足一定条件要求。当环形放大器电路能够满足稳定性准则,则环形放大器的时间域响应将经历初始转换、稳定和锁定信号放大阶段过程。

3 闭环配置CMOS环形放大器设计

模拟集成电路中放大级电路的设计,若采用传统有源负载共源放大器结构,则信号仅驱动1 个晶体管,而采用CMOS 环形放大器结构,则与静态CMOS 逻辑门工作类似,NMOS 和PMOS 晶体管对推挽工作。典型的CMOS 反相器的电压转移特性曲线如图6所示,需要强调的是应正确设计优化晶体管的尺寸,使逻辑阈值VM近似位于0.5VDD附近,以便能使线性区最大化。

图6 CMOS 反相器的电压转移特性曲线

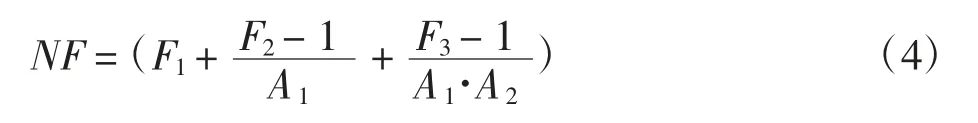

对于CMOS 环形放大器的设计,首先需要确定各级CMOS 反相器的增益分配。因为每一级增益都影响着环形放大器的噪声性能,因此恰当地分配每一级增益显得非常重要。环形放大器的整体噪声系数(noise figure)可表示为:

式中:F1、F2、F3分别为三级 CMOS 反相器级的噪声系数。

可见,对于给定的增益要求,第一级分配最高增益将有助于有效减小环形放大器的噪声系数。因此,第一级反相器的晶体管应当设计为较大尺寸以获得高增益。第二级反相器的直流偏置电压决定了第三级反相器的直流偏压,从图5可知,失调电压VRN和VRP通过第二级反相器而产生输出级PMOS 晶体管的直流偏压和NMOS 晶体管的直流偏压,这对于闭环配置的环形放大器的稳定性至关重要。减小第二级反相器增益有助于稳定输出级晶体管的直流偏压,因而第二级反相器的晶体管应当设计为较小尺寸。第三级反相器的晶体管尺寸的设计不仅影响着CMOS 环形放大器的整个增益,也影响着稳定性。第三级反相器的晶体管应被偏置工作于亚阈值区,选择适当晶体管尺寸使具有最大阈值,将导致较大死区,从而减弱稳定性对输出级晶体管偏压变化的依赖性。第三级反相器对闭环配置环形放大器非常重要,设计中也应当考虑闭环配置中反馈电容的电荷共享效应。

稳定性在CMOS 环形放大器设计中也需要重点考虑。闭环配置环形放大器的稳定性不仅与三级反相器相关,也与反馈因子密切相关。在闭环配置开关电容环形放大器结构中,反馈因子表示为:

式中:Cin为输入电容;Cf为反馈电容。

为了获得较高的闭环增益,反馈电容应尽可能小。然而,环形放大器输出端极点也与反馈电容相关,因此反馈电容的值也应当尽可能大, 以使环形放大器稳定工作。在闭环配置环形放大器中,通常由三级反相器获得的高开环增益,可使反相器级对闭环增益和稳定性的影响不显著。另外,在该开关电容环形放大电路中,除与输入端连接的开关外,其他开关皆不在信号传输路径中,因此开关可采用简单的最小尺寸NMOS 晶体管。

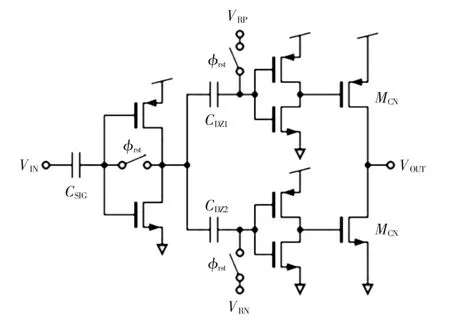

在实际应用中,上述单端输入、单端输出的CMOS 环形放大器结构往往难于满足模拟集成电路中信号差分处理的要求。采用2 个环形放大器构成的伪差分放大器结构虽然可以对差分信号进行处理,但所获得的共模抑制比(common mode rejection ratio,CMRR)较低。若信号处理采用浮动采样方法,可以消除伪差分放大器结构所需要附加的共模反馈电路,伪差分浮动采样环形放大器如图7中所示,在1.5 b MDAC 应用中采用了伪差分浮动采样环形放大器结构[3]。

图7 伪差分浮动采样环形放大器

4 技术挑战

CMOS 环形放大器结构能够充分受益于CMOS 工艺技术的进步。随着CMOS 工艺特征尺寸的减小,CMOS反相器的功耗-延迟积近似线性下降[6],使得CMOS 环形放大器中三级反相器的传输延迟也可随CMOS 工艺技术的进步而有效改善。通过对环形放大器稳定性准则的分析可知,传输延迟的减小可以有效改善环形放大器速度和精度。此外,CMOS 环形放大器结构中,前2 级反相器的增益,以及输出级晶体管MCN和MCP的器件增益也将受CMOS 技术进步的影响,但是随着工艺特征尺寸的减小仍然能够维持足够的反相器增益。虽然在22 nm CMOS 工艺技术节点,平面晶体管器件将面临挑战,环形放大器结构中基于平面晶体管的反相器将难于维持足够增益。但在亚32 nm CMOS 工艺节点,可以采用新技术,如FinFET 器件或绝缘硅(silicon-on-insulator,SOI),这将更好地控制短沟道效应[7],可以为实际的环形放大器应用提供足够的固有器件增益。

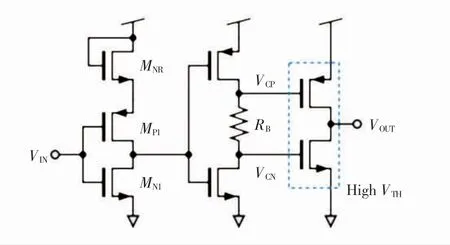

虽然上述CMOS 环形放大器结构具有诸多优点,但偏置电压必须设置在一个较小的窗口范围。在实际模拟集成电路应用中考虑工艺变化和电源电压变化影响时,一方面,若过驱动电压太高,输出级的输出阻抗不足够大,则可能引起震荡;另一方面,如果过驱动电压太低,第二级反相器工作在线性区,则可能导致较低的三级反相器增益。自偏置的环形放大器如图8所示。从图8可以看出,自偏置的环形放大器结构受工艺和电源电压变化的影响较小[8]。第二级采用单个自偏压直流耦合CMOS 反相器代替2个交流耦合的第二级反相器,并且消除了2 个外部偏压和相应的开关。第三级反相器采用高阈值电压器件,对于给定的栅源电压,能够提供更高的输出阻抗。工作时,位于第二级反相器晶体管漏端的电阻可动态偏置输出级晶体管的栅电压。该电阻偏置失调方法,可以使失调跟踪电源电压的变化。当环形放大器经历转换时,这种动态偏压能够有效驱动后级晶体管,并且当输入端接近虚地时,所提供失调电压使输出级晶体管工作在深亚阈值区。在第一级反相器中,为了对噪声和功耗进行优化,通过一个二极管连接的晶体管MNR 降低了晶体管MP1和MN1构成的反相器的有效电源电压。而反相器电源电压的减小将能够使晶体管MP1和MN1采用更大尺寸宽长比W/L,从而对于给定电流可以获得更高夸导,因此引起更低热噪声而不增加静态功耗。

图8 自偏置的环形放大器

在自偏置环形放大器结构基础上,通过改进可构成适合于流水线模数转换器应用的全差分环形放大器[9]。另外,将自偏置环形放大器第二级的电阻RB用类似CMOS 逻辑开关的 APCMOS(anti-parallelarrangement of CMOS transistors)结构替代,则在改善失调电压调整性的同时,增加了环形放大器的可控性,并且在此基础上通过对第一级和输出级进一步优化,可使环形放大器在高速高精度的流水线模数转换器应用中表现出巨大潜力[10]。

5 结 语

在模拟集成电路设计中,与传统放大器结构相比较,CMOS 环形放大器在深亚微米CMOS 技术具有独特优势。CMOS 环形放大器结构源于环形振荡器,并且能够充分受益于CMOS 技术的不断进步。环形放大器将环形振荡器分离成2 个嵌入不同失调的信号路径,由反相器、电容和开关构成,结构简单且能够以低功耗获得高增益。CMOS 环形放大器以数字开关电源方式有效驱动大电容负载,这种高度数字化的开关行为,使得CMOS 环形放大器的功耗-延迟积性能可以随CMOS 技术的持续进步而有效改善。模拟集成电路中需要对信号差分处理,采用2 个单端输入、单端输出的环形放大器构成的伪差分放大器结构虽然可以处理差分信号,但共模抑制比较低。而采用浮动采样方法的伪差分环形放大器结构可以消除所需要的附加共模反馈电路。当然,也应存在许多其他可行的环形放大器结构以满足不同应用的需要,如自偏置环形放大器、高速高精确环形放大器等。在CMOS 环形放大器设计中精度、速度和功耗是选择满足应用所需要最优结构的重要因素。