基于实时计算的雷达波形发生器

祝昇翔,贺志毅,杜 海,熊 坤

(北京遥感设备研究所,北京 100854)

0 引 言

随着雷达技术的不断进步,干扰和抗干扰技术这对矛盾在不断对抗的过程中互相促进,共同发展。新出现的数字射频存储(DRFM)技术[1]可以快速接收、存储和转发雷达方的发射波形,对其进行有效的欺骗干扰[2]。为了应对这类干扰,低截获概率雷达通常需要发射各类复杂的特殊波形,期望能够提高目标检测和识别的概率,同时防止被非合作方截获和检测[3-4]。

直接数字频率合成器(DDS)采用数字化方法合成各类波形,具有分辨率高、灵活方便等优点。传统的雷达波形发生器多采用专用DDS 芯片来实现,例如常用的AD9910 内部采用32 bit累加器,支持高达400 MHz的波形输出[5],AD9914支持输出的最高点频可达[6]1.5 GHz。但是,这类方法受限于DDS 芯片本身的参数限制,工作频率不够高,无法适应新型复杂波形的需求。而使用通用高速DA 加FPGA 实现DDS 功能的架构具有更强的可编程能力,使用灵活方便,越来越多地被采用。文献[7]采用直接存储方式将波形预先生成好并进行预存,这种方式理论上可以产生任意复杂波形且不存在失真,但是当波形时宽较大时占用存储资源过多,而且波形是固定的,容易被敌方截获。

本文提出并实现了一种基于实时计算的雷达波形发生器。所用的核心器件为Xilinx 公司的FPGA 芯片(XC7K410T)和ADI 公司的射频数模转换器AD9129。在FPGA 内部采用实时计算方式,根据输入的波形参数灵活地生成各类复杂雷达波形,避免不必要的存储资源占用,已在实际产品中使用,效果良好。

1 波形设计

1.1 基本原理

DDS的主要结构包括累加器、相位-幅度转换器、数模转换器和低通滤波器。其中,累加器、相位-幅度转换器可在FPGA 内实现。DDS的三个主要控制参数为幅度、频率和相位。幅度控制在数字域容易实现,但对接收机要求较高,并不常用,因此各类复杂波形主要依靠改变频率和相位来实现。

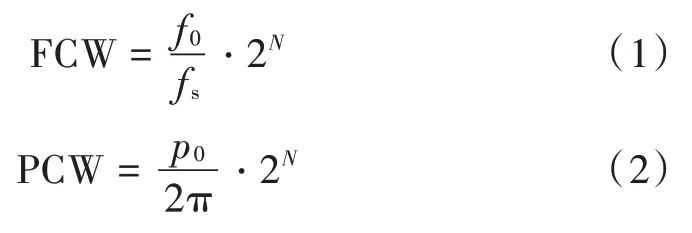

DDS 通过频率控制字和相位控制字控制信号的频率和相位:

式中:FCW 为频率控制字;PCW 为相位控制字;f0为期望输出的频率;p0为期望输出的相位;fs为采样时钟频率;N为对应控制字的二进制位数,即累加器的位宽。

以最简单的正弦波为例,其频率为常数,初始相位设为零,每个时钟周期累加器对固定的频率控制字进行累加,累加结果的高位送入相位-幅度转换器进行查表即可。对于正弦波来说,该表格存储的就是正弦波的一个周期的时域离散结果。相位-幅度转换器根据系统的要求而定,通常占用资源很少,以4 096 点,14 位位宽的正弦波查找表为例,占用资源为56 Kb,相位分辨率约为0.087 5°。

1.2 线性调频波形

1.2.1 波形特性

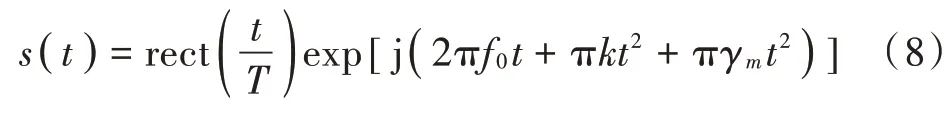

线性调频信号是雷达系统中最常用的波形之一,对多普勒频移不敏感,有一定的低截获能力。其复信号形式为:

式中:T为脉冲宽度;f0为载波频率;k为线性调频斜率。DDS 发射波形时一般可取其实部作为实信号使用。对相位进行求导,可以得到频率:

普通正弦波的频率为固定值,而线性调频信号的频率是线性变化的,相位也是随着频率而变化的。因此,在DDS 实现时需要使用频率累加器和相位累加器两级累加器。第一级频率累加器需要设置初始频率(正调频时为f0-B/2,负调频时为f0+B/2,B为信号带宽),然后每个时钟周期累加k对应的频率控制字。第一级频率累加器的输出,送入第二级相位累加器进行累加,累加结果的高位送入相位-幅度转换器进行查表,表格内容仍然为正弦波的数值。由式(3)可知,线性调频信号的相位是t的二次多项式,按照文献[8],当相位表达式为更高阶数的多项式时,可采用相同的方法使用多级累加器实现复杂波形输出。

DDS 频率设为2 GHz,线性调频信号载波频率设为500 MHz,时宽为10 μs,带宽为60 MHz,调频斜率为正。其时域和频域仿真结果如图1 所示。

图1 线性调频波形时域和频域结果Fig.1 Time-domain and frequency-domain results of LFM waveforms

1.2.2 波形产生

各类宽带波形普遍要求DDS 频率达到GHz 量级,而FPGA 内部工作时钟频率一般不超过500 MHz,无法直接满足DDS的频率和相位控制字的更新速率。因此要实现GHz 级的DDS 输出,必须利用FPGA的并行处理特点。

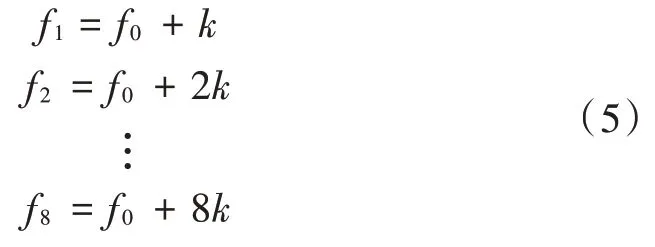

本设计中DA 工作频率采用2 GHz,FPGA 工作时钟采用250 MHz,内部采用48 位累加器以提高分辨率。与普通DDS 处理流程的区别是:在1 个时钟周期内需使用8 路累加器和相位-幅度转换器同时计算出原先顺序计算的8 个点的幅度结果,这样等效的转换速率是2 GHz,实现了速率匹配。

8 路频率累加器的输出分别为:

8 路相位累加器的输出分别为:

式中:f0为初始频率(不是载波频率);p0为初始相位。需要注意,计算按照8 个点循环,下一个时钟周期的初始频率为f8,初始相位为p8,以此类推。为了确保FPGA实现性能,对式中已确定的频率控制字的乘法预先算好并存储为参数,对其他乘法采用移位和加减法代替。对于更高频率的需求,可以划分为更多路数来支持。

1.3 巴克码波形

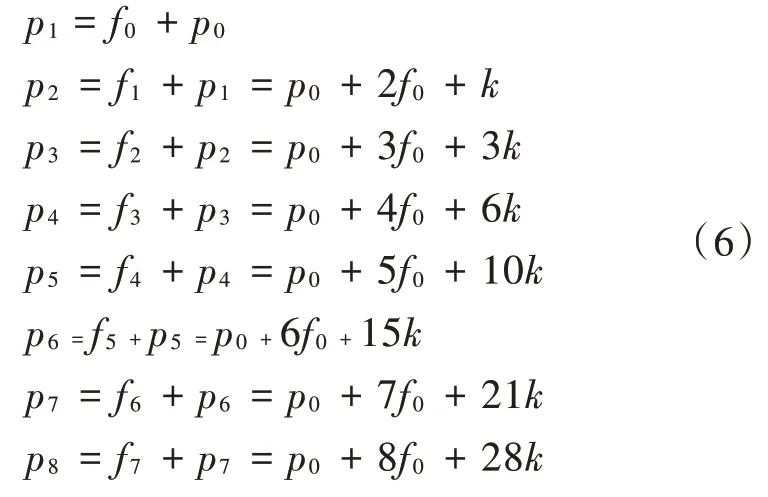

雷达波形可分为调频波形和调相波形。常用的调频波形如1.2 节的线性调频信号以及步进频率信号等,调相波形有二相编码信号、多相编码信号、Frank 码等,其优点是相位离散化,不易被截获。巴克码是一种常用的二相编码,已知最长的巴克码为13 位,数值为{1,1,1,1,1,-1,-1,1,1,-1,1,-1,1}。基于13 位巴克码的二相编码脉冲信号的复包络为:

式中:un为相位编码(+1,-1);Tb为子脉冲宽度。将一个脉冲分为13 个子脉冲,使用巴克码对固定载频(正弦波)进行调制,得到巴克码调制脉冲串。

DDS 频率设为2 GHz,载波频率设为500 MHz,子脉冲宽度设为50 ns,总脉宽设为13 μs,巴克码调制脉冲串时域和频域仿真结果如图2 所示。

图2 巴克码调制脉冲串时域和频域结果Fig.2 Time-domain and frequency-domain results of Barker code-modulated pulse train

FPGA 实现时,使用计数器控制各子脉冲输出时序,频率控制字按照载波频率设置,累加器输出查表得到幅度结果后再按照子脉冲对应的相位编码进行调制(即乘以1 或-1)即可。

1.4 抗DRFM干扰波形

在满足雷达探测性能的同时,还要尽可能防止敌方的干扰。传统的雷达波形形式相对固定,容易被敌方使用DRFM 技术进行存储转发实现干扰,因此要求新的雷达波形尽可能做到随机捷变,使得敌方无法识别信号,或者即使识别了也无法有效干扰。

1.4.1 SVLFM 波形

文献[9]给出一种对抗DRFM的变斜率线性调频信号(SVLFM),它是在LFM 信号的基础上,每个脉冲重复周期加入一个雷达方已知的随机相位扰动。该信号自相关特性较好,互相关特性较差,使得干扰与回波信号失配,从而实现抗干扰的目的。

式中:γm(m为脉冲重复周期编号)为雷达方已知的随机数,加入随机相位扰动后相当于线性调频斜率从k变为k+γm,通常γm的绝对值应小于k。同时,由于线性调频斜率发生变化,为了保证带宽恒定,信号发射的时宽需要成比例地进行对应改变。FPGA 实现时,方法同1.2 节,只是在用相位累加器计算时加入对应的相位扰动即可,而随机数可使用线性反馈移位寄存器生成伪随机数实现。

1.4.2 SIMFAR-LFM 波形

同时频率捷变雷达(SIMFAR)信号[10]是使用单个微波源同时产生多个不同频率的子信号,每个子信号在频域上分开且占据一定的带宽,子带内还可进行频率或相位编码。对于雷达方,可以在接收端对各子带信号分别混频、脉压处理后进行相干积累获得处理增益。而在总功率相同的情况下,敌方截获的单个子带的功率较低,增大了干扰的难度。使用LFM 信号同时进行频率捷变,可得到SIMFAR-LFM 波形,该波形属于组合波形,由M个子带组成,兼具了LFM和SIMFAR 信号的优点。

DDS 频率设为2 GHz,设置8 个带宽40 MHz的LFM同时发射的SIMFAR-LFM信号,时域和频域结果如图3所示。FPGA 实现时,8路线性调频信号的起始频率控制字不同,但是时宽就是总的脉宽,是完全一致的,因此在时域上可将8路相位-幅度转换器输出结果逐点进行累加。

在此基础上,为了进一步增加敌方干扰的难度,可以对每一个子带的线性调频斜率进行捷变,这相当于频率编码,而且便于实现。以此为例,仍然使用线性反馈移位寄存器,每个脉冲重复周期生成一个8 bit的二进制伪随机数,对应8 个子带的调频斜率,0 为正斜率,1 为负斜率,对应地修改DDS 每一路的起始频率控制字和调频斜率,即可实现脉内和脉间的调频斜率捷变。

2 发生器设计

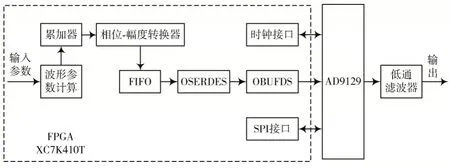

选用ADI 公司的射频数模转换器AD9129 作为DA 芯片,其位宽为14 位,包括基带模式、混频模式等以适应不同的频段,支持最高射频合成频率达4.2 GHz,可用于宽带无线通信和雷达系统等。

图3 SIMFAR-LFM波形时域和频域结果Fig.3 Time-domain and frequency-domain results of SIMFAR-LFM waveforms

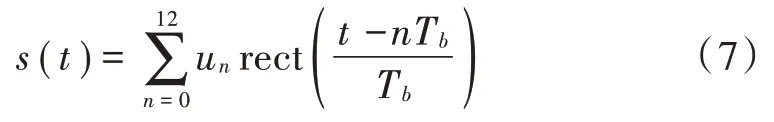

本设计使用的频率为2 GHz,根据输入参数求得雷达波形的幅度数据后,每个250 MHz时钟周期将并行的8 个采样点共112 bit 数据送入FIFO 缓存。从FIFO 读出数据后,按照高低位将其分为4 组:D1[27:0],D2[55:28],D3[83:56],D4[111:84]。每组数据截取1 bit 数据,送入OSERDESE2(Xilinx FPGA 底层原语)完成4∶1的并串转换,共28 路并行进行转换。为了支持GHz 级的高速数据转换,AD9129 提供了源同步LVDS 接口,包含P0和P1 两个数据接口,每个接口为14 bit 差分接口。这样FPGA 接口速率可以为DA时钟速率的一半,降低了设计难度。28 路OSERDESE2的输出分为上下两组,分别对应P0和P1 接口,送入28 个OBUFDS(Xilinx FPGA 底层原语)进行单端到差分的转换。时钟方面AD9129 需输出DCO时钟为数据源提供时钟,FPGA 需要输出DCI时钟给AD9129 用于接口数据同步,二者均为DA时钟速率的1/4,这里为500 MHz。此外,AD9129的寄存器读写通过串行外设接口(SPI)完成,可以配置DA的工作模式、幅度等参数。最后AD9129 将数模转换结果送入低通滤波器输出。设计框图如图4 所示。

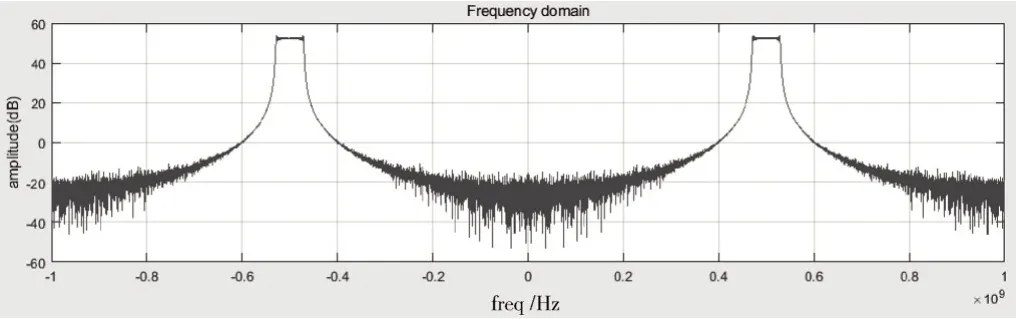

设计完成后产生LFM 波形的频谱如图5 所示,由于FPGA 采用定点计算产生波形,因此与图1的理想情况相比,频谱存在噪声。

3 结 语

本文采用通用高速DA 加FPGA的架构,充分利用FPGA 可灵活编程的特点,以实时计算的方式实现了雷达波形发生器。可根据输入参数实时生成捷变的波形,无需占用大量存储资源,使用灵活方便,具备了波形多样性的能力。目前已应用于产品,可产生大时宽、大带宽的各类复杂波形。经过各类试验验证,表现稳定可靠。

图4 波形发生器框图Fig.4 Block diagram of waveform generator

图5 FPGA实现LFM信号频谱Fig.5 LFM signal frequency spectrum implemented with FPGA