低电容TVS用常压外延工艺研究

仲张峰,尤晓杰,王银海,邓雪华,魏建宇,杨 帆

(南京国盛电子有限公司,南京 211111)

1 引言

瞬态电压抑制器(TVS)是一种用于电压瞬变和浪涌防护的半导体器件,它能在皮秒级的时间内吸收高达数千瓦的浪涌功率,有效保护电子线路中的精密元器件。对于高频电路的保护,则需要低电容或者超低电容TVS,以减少寄生电容对电路的干扰,降低高频电路信号的衰减。

低电容TVS通过低击穿电压的雪崩二极管与低电容的导引二极管(PIN或NIP)组合而成。因为低击穿电压的雪崩二极管的掺杂浓度很高,而PIN或NIP二极管中的I层掺杂浓度很低,此结构需要在重掺衬底上生长高阻外延层来实现。其中衬底电阻率越低,雪崩二极管反向击穿电压越低,被保护电路两端所能箝住的电压越小,浪涌抑制能力也就越好;外延层电阻率越高,电容越低,高频电路信号的衰减越小[1]。

外延生长是指在单晶衬底的表面上,利用二维结构相似性成核的原理,沿着原来的结晶轴方向,生长特定电阻率和厚度单晶层的工艺。埋层外延是指在制有特定光刻图形的衬底上进行的外延,其外延温度越高,图形漂移量越小,但相应衬底杂质挥发越多。而理想的低电容TVS器件要求重掺衬底和高阻外延层掺杂浓度差达到5个数量级,为了有效控制高阻层的电阻率,需要将衬底杂质挥发比控制到万分之一以下。埋层衬底的高温外延以及外延、衬底的超高浓度差对外延工艺中自掺杂的抑制提出了更高的要求[2]。低电容TVS器件材料常规是通过减压条件单片生长外延模式来实现,生产效率较低,成本较高[3]。而常压外延条件、多片生产模式具有生产效率高、成本低的特征。通过衬底背面自吸硅制作多层背封结构以及低温生长缓冲层的工艺,有效抑制了外延过程中的自掺杂,在P型重掺衬底上生长出薄层高阻的N型外延层,降低了雪崩二极管的反向击穿电压,提高了单位面积的浪涌抑制能力,满足了器件的设计要求。

2 技术要求

通过采用特殊的工艺条件,在常压机台上完成了P型重掺衬底上高阻N型外延层的批量生产制作,衬底电阻率 <0.005 Ω·cm,衬底晶向为 <100>,N-高阻层电阻率要求 >100 Ω·cm。

低电容TVS器件工艺中,外延层生长在埋层区域之上。埋层区域构成一定的图形,这种图形会随着外延生长在外延后的表面形成整体的平移,称为图形漂移;图形本身也会放大或者缩小,称为图形的畸变。为了控制埋层图形漂移和畸变,保证后续光刻工艺对标的准确度,外延生长速率和生长温度的选取尤为重要[5]。

3 外延工艺分析

图1为低电容TVS外延工艺结构图,其主要工艺技术难点是在高温外延条件下控制埋层漂移的基础上,如何有效地抑制衬底硅片的自掺杂影响,以保证N-高阻层电阻率的稳定控制、相对较窄的过渡区宽度、外延层参数均匀性控制、图形漂移量的控制以及几何参数的控制等。

为了有效抑制衬底硅片的自掺杂效应并保证后续光刻工艺的准确度,我们采取了以下工艺技术方案。

3.1 重掺衬底自掺杂抑制

重掺衬底自掺杂抑制是低电容TVS用外延材料研制的关键技术,存在以下几个工艺难点:

(1)常压外延工艺成本低、生产效率高,但自掺杂控制能力不及减压外延;

(2)多片生长模式下,衬底之间自掺杂影响大;

(3)<100>晶向表层非密排面,杂质挥发易于<111>晶向;

(4)外延电阻率远高于常规外延参数,衬底与外延层杂质浓度相差近5个数量级,杂质扩散影响程度大。

图1 低电容TVS外延工艺结构图

为了有效控制自掺杂,通过在衬底背面自吸硅制作多层背封结构、低阻缓冲层外延工艺等方法,可将衬底杂质挥发比控制到1/10000以下:

(1)因高温下杂质B易析出挥发,重掺P型衬底上的薄层外延工艺中主要的自掺杂来自衬底背面和边缘蒸发出的气相杂质。外延前在基座上包上一层本征外延层,通过高温自吸硅的工艺给衬底增加一层微米级的Poly背封层,进而阻挡衬底的P型自掺杂对正面外延的影响[6]。

(2)因B原子量小,高温下扩散速度快、距离长,对周边结构影响较大,在做N型埋层前,先在P型衬底上生长一层>1 Ω·cm的中阻P型缓冲层,减少高温下B扩散对埋层的影响。做N型高阻层之前,先外延一层N型低阻缓冲层,一方面抵消P型衬底和中阻缓冲层对后续N型高阻层的侵蚀;另一方面,在外延腔体和衬底边缘覆盖N型低阻层,进一步抑制衬底和腔体内P型自掺杂的影响。

3.2 图形漂移控制

实验和批量生产所采用的机台为PE-2061S设备,该设备生产常规埋层电路一般采用高温生长工艺。但考虑到温度越高,衬底自掺杂越重,而表面N-层电阻率要求大于100 Ω·cm,与之对应的P型自掺杂则需要控制到更低水平。经过3组温度拉偏实验与光刻匹配,常规埋层工艺降低30~50℃生长可以满足光刻的要求,同时为抑制衬底的自掺杂提供了有利条件。

3.3 HCl精确抛光

因外延前已进行了N型埋层的制作,表面存在损伤层,直接外延后将会产生满片层错。为了去除表面损伤层,得到较完整的外延基底,外延前通过衬底表面精确控制的HCl气相腐蚀和高温退火,在保证了表面外延质量的同时,避免对埋层厚度的过度侵蚀。

3.4 超高阻外延掺杂控制

低电容TVS外层电阻率>100 Ω·cm,掺杂设定只有常规参数的1/10,对流量精度控制要求较高;通过选取小量程流量计,保证掺杂流量在流量计线性范围内,实现外延电阻率的精确控制。

4 结果与讨论

温度越高,衬底边缘和背面自掺杂越重,为了满足自掺杂控制的需要,经过温度拉偏和器件工艺匹配,常规埋层工艺降低30~50℃生长可以满足光刻的要求,外延后图形如图2和图3所示。

图2 常规埋层工艺外延图形(500倍)

图3 降温工艺外延图形(500倍)

通过调整HCl气相腐蚀温度和流量,对衬底表面进行微量腐蚀,同步进行了退火工艺,在1 mm×1 mm区域层错数量控制到10个以下。

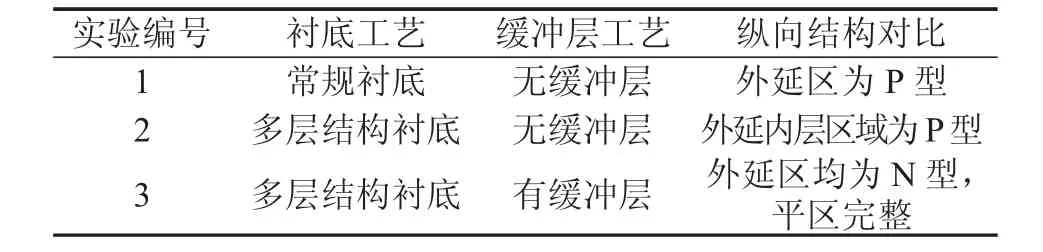

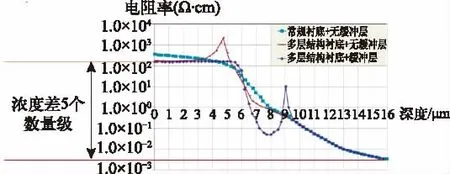

通过3组实验对比了不同工艺的结果,如表1所示。从图4外延层SRP可知,高温下B杂质扩散距离长,中阻P型缓冲层已全部被重掺衬底自掺杂影响,电阻率都在1 Ω·cm以下,通过P型中阻缓冲层降低了B扩散对埋层结构的影响。实验1中在常规衬底且无缓冲层的工艺条件下,整个N-高阻层都被衬底P型自掺杂中和为P型高阻层。实验2中通过衬底自吸硅工艺Poly背封,在无N型缓冲层工艺下,5~8 μm深度P型自掺杂仍占优,5 μm处存在高阻夹层。而实验3中,在衬底自吸硅背封和N型低阻缓冲层工艺下,表层衬底自掺杂已被控制到万分之一以下的量级,0~8μm外延区均为N型,其中0~6μm间为电阻率>100Ω·cm的N型平滑高阻层,满足了器件的设计要求。

5 结论

通过衬底背面自吸硅制作多层背封结构以及低温、长缓冲层的外延工艺,将重掺衬底杂质挥发比控制到万分之一以下,在超低阻P型衬底上制备出薄层(8 μm)N 型高阻(150 Ω·cm)外延层,平区厚度达到6μm,满足了高性能低电容TVS的量产需求。通过使用常压工艺、多片加工模式,实现了高效率的外延生产。

表1 工艺实验对比

图4 器件外延层SRP

为了降低雪崩二极管的反向击穿电压,P型衬底电阻率从常用的0.01~0.02Ω·cm范围降到了<0.005Ω·cm的范围;为了进一步提高单位面积的浪涌抑制能力,将N型高阻外延厚度从常用的10~20 μm降低到8 μm。在以后的工作中,通过进一步匹配背面处理工艺与外延工艺,有望继续提高N型高阻外延层的电阻率。