一种抗单粒子瞬态辐射效应的自刷新三模冗余触发器

曹 靓,田海燕,王 栋

(中国电子科技集团第五十八研究所,江苏无锡 214072)

1 引言

随着半导体工艺技术的发展,工艺尺寸日渐缩减,集成电路内部的晶体管密度不断增大。在航天等领域,电路在空间应用时单粒子效应的影响也随着工艺发展而愈加显著。另外,随着电路工作频率的不断提高以及工作电压的降低,不但会导致存储器类电路发生单粒子翻转效应(SEU),而且会使数字电路中的单粒子瞬态脉冲(SET)越来越严重[1-3]。

SET效应是因宇宙空间里高能粒子冲击电路而产生的瞬时电压或电流脉冲,对电路产生扰动的效应,会导致至少3种错误:

(1)SET脉冲通过某些模拟电路会被放大,形成更强的错误信号;

(2)SET脉冲被存储器、触发器、寄存器等捕获,造成数据存储错误;

(3)SET脉冲发生在时序逻辑中时,会使电路产生错误节拍,导致电路时序紊乱。

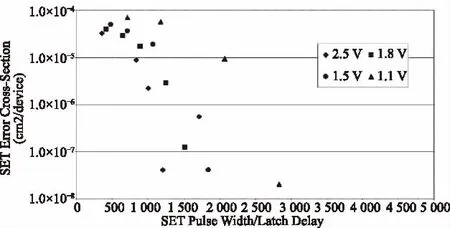

图1所示为SET效应在0.18 μm CMOS电路中产生的脉冲[4]。SET效应产生的脉冲宽度是随着电源电压的降低而变大的,最大能到纳秒级。而在SET加固方法上,传统采用的时间冗余、保护门等方法会增加电路的面积与功耗,仅适合于小规模数字电路,对于超大规模集成电路如CPU、FPGA等,需要一种更高效的方法来减小SET效应的影响。

图1 0.18 μm工艺SET效应产生扰动的脉宽

本文基于带自刷新功能的三模冗余触发器[5],提出一种抗SET脉冲的加固设计结构。该设计并不需要对每一个输入通路都进行时间冗余或保护门等方法进行加固,而是在其自刷新表决器上进行改进,从而实现对SET效应的加固。

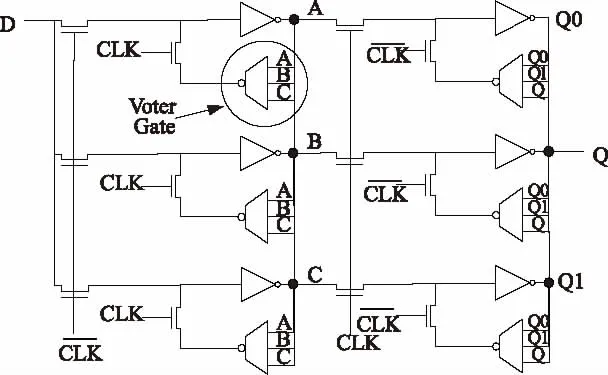

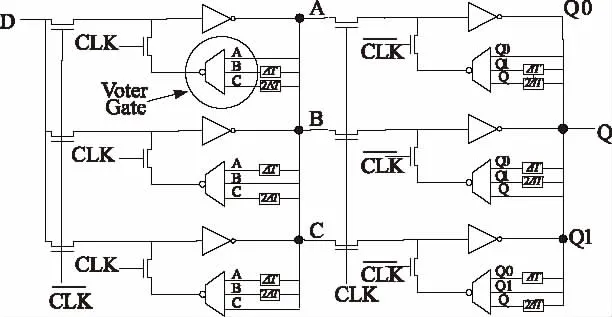

2 带自刷新功能的三模冗余设计

图2所示的三模冗余触发器,其特点为在3路并行触发器每个带反馈的存储结构里,均包含表决器设计,3路触发器共包含6个表决反馈结构,每个表决结构相互独立,互不干扰[5]。A、B、C、Q、Q0、Q1中任何一个节点发生SEU错误,都会被另外两路正确信号纠正,并且这个纠正过程是即时的,不需要等待时钟或其他信号驱动,从而达到SEU加固的目的。

图2 带自刷新功能的三模冗余设计

虽然该设计的触发器可以针对SEU效应进行很好的加固,但是当外部输入信号如D、CLK还有置位/复位等通路上信号因SET效应而产生干扰脉冲时,由于SET干扰信号可以同时影响3路存储单元,该结构就不能将其纠正,因此不具备SET加固效果。

3 传统抗SET效应加固设计方法

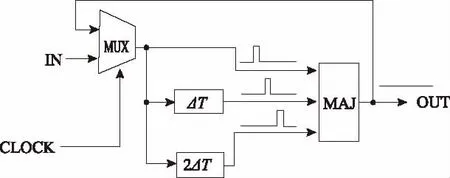

传统的抗SET设计加固方法多采用时间冗余或保护门结构[6],如图3和图4所示。

图3 时间冗余结构加固

图4保护门结构加固

图3 和图4所示的加固结构,其基本原理都是通过将原先的一路信号分成多路(一般2~3路),让信号在增加的通路上传播时增加一定的时间延迟(ΔT),在输出端将原信号和增加了ΔT时间的信号进行比较判断,将SET脉冲产生的扰动滤除。延迟ΔT的时间即为该结构可以滤除的SET脉冲的最大宽度,在设计时需要确保ΔT足够大,从而保证较好的加固效果。

从上述两种结构的工作原理来看,使用时需要在系统的每个关键路径上加入上述结构,如果电路结构复杂,信号路径较多,必然会给电路带来极大的额外面积和功耗,这对于大规模集成电路而言是难以接受的。并且,上述两种结构都还需要加入其他的辅助设计结构,同时也会增加面积和功耗。

4 抗单粒子瞬态辐射效应的自刷新三模冗余触发器设计

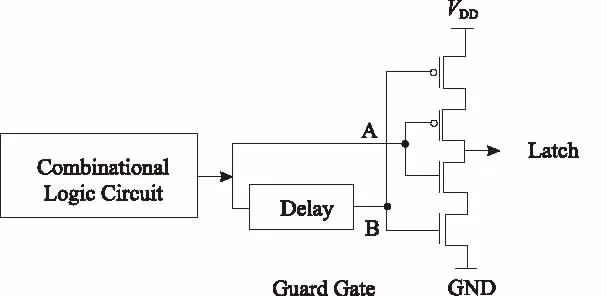

在图2所示的自刷新三模冗余触发器基础上,结合传统SET加固采用的时间冗余、保护门结构的加固思路,对图4结构中圆圈标识的表决器进行改进。通过在表决器输入的3路信号中的非自身反馈的2个通路上分别引入ΔT和2ΔT的延时来对SET干扰进行滤除,电路结构如图5所示。由于该设计直接针对单元存储结构进行,所以不需要对每一路输入信号进行加固,比较适于在结构复杂、信号较多的情况下进行加固应用。其工作原理在于,虽然外部SET干扰信号会同时输入并行的3个存储单元,但在存储的反馈环路上由于ΔT和2ΔT的存在,信号不会同时进行表决。因此,小于ΔT时间的干扰脉冲将不会被存储下来,触发器存储的信息不会因此被改写,从而在SEU加固的同时达到SET加固的目的。

图5 抗单粒子瞬态辐射效应的自刷新三模冗余触发器设计

5 仿真验证

仿真工具采用Hspice,仿真模型选用中芯国际0.18 μm工艺进行了仿真分析,仿真结果如图6所示。图6中d为触发器的数据输入信号,q为数据输出,ck为驱动时钟,set为触发器置位信号,clr为触发器复位信号。从仿真结果看,设计的抗单粒子瞬态辐射效应的自刷新三模冗余触发器对输入信号产生的干扰脉冲可以通过延时表决结构进行滤除,滤除的最大脉冲宽度达到2.6 ns,如图7所示,达到了抗单粒子瞬态脉冲加固需求。

6 试验验证

采用该触发器结构的试验电路经单粒子试验,在辐射环境下,以10 MHz工作频率、2000级触发器量级的逻辑功能进行工作,可达到37 MeV·cm2/mg下无逻辑错误。试验结果证明加固效果明显。

图6 抗单粒子瞬态辐射效应的自刷新三模冗余触发器功能仿真图

图7 抗单粒子瞬态辐射效应的自刷新三模冗余触发器滤波延时

7 总结

随着半导体工艺的进步、工作频率的增加以及工作电压的降低,大规模集成电路在空间应用时对单粒子瞬态辐射效应越来越敏感。在SET加固方法上,传统采用的时间冗余、保护门等方法已不适用于大规模数字电路。为此,本文提出了一种基于带自刷新功能的三模冗余触发器进行改进的设计结构,通过在三模冗余触发器的每一个存储反馈回路中的表决器输入的3路信号中,将其中非自身反馈的2个通路上分别引入ΔT和2ΔT的延时来对SET干扰进行滤除。该方法为抗辐射大规模集成电路的抗单粒子瞬态辐射效应加固设计提供了新的思路。