一款8位高速逐次比较型ADC的设计

王堋钰,高 博,钱 正,龚 敏,谭 萍

(微电子技术四川省重点实验室,四川大学物理科学与技术学院微电子系,成都 610065)

1 引言

模数转换器是现实世界中连接模拟信号与数字信号的重要桥梁。数据处理器大多需要低功耗、中低采样速率的A/D转换器。SAR ADC具有低功耗、尺寸小、转换效率高等特点。这些特点使其广泛应用于高速传输、便携医疗仪器、电池以及工业控制和信号采集等方面[1]。

SAR ADC结构中的主要模块有DAC电容阵列、比较器、采样开关以及数字控制模块。SAR ADC的转换精度与二进制加权的电容阵列有着密切关系,若单位电容越大,DAC的最高位(MSB)电容将显著增加,不仅导致最高位的置位时间越长,同时也影响了比较器在单位时间内的比较次数,对ADC的速度有显著的影响[2],因此高速的SAR ADC一般采用较小的单位电容。参考文献[2]是在180nm工艺下设计的一款ADC,可以看到该ADC的转换速度被限制到了35 MS/s。参考文献 [3]、[4]均采用较小的单位电容来得到更好的ADC性能,他们采用了串联电容或者是定制电容的办法来获得小电容,这样就导致流片成本的增加。以上是基于将单位电容减小的方法来提高速度,若是单位电容已经固定,则可以通过本文提出的DAC结构来提高ADC的转换速度。

本文提出一种提高SAR ADC速度的设计方法,将DAC的最高位(MSB)电容替换成两个小电容并联,两个小电容的容值和与之前的大电容容值相等。增加一个寄存器同时进行驱动,从而减小DAC的MSB电容的置位时间。相比传统结构25 MHz的转换速度,文中所提出的结构可达到51 MHz,速度提高了100%。此外,与传统结构相比,新提出的结构在只增加一个寄存器的条件下,ADC的功耗仅增加0.05 mW,ADC的精度也得到了提高。

2 SAR ADC整体结构以及改进型分裂式DAC

2.1 SAR ADC整体结构

本文设计的SAR ADC的原理框图如图1所示。采样信号(CLKS)为高电平时,输入信号通过自举开关进行采样,DAC电容的下极板与基准电压连接。CLKS为低电平时,采样开关进入保持状态,将采样后的输入信号送到比较器的输入端。首先,在CLK为高电平时,比较器进行第一次比较。第一次的比较结果送到SAR控制逻辑部分,SAR的输出控制差分电容阵列的相应侧电容开关的开或关。如果VIP大于VIN的值,比较器的正向输出端输出高电平,则最高位为1,并存入SAR逻辑电路中。差分电容阵列中对应电容开关打开或关闭,比较器的正向输入端电压变为VIP-0.5VREF,负向输入端电压变为VIN+0.5VREF,在CLK第二个高电平的时钟信号来临时进行第二次比较。A/D转换器重复该操作,直到第8位得出比较结果。在本设计中采用了同步时序结构,要8位的比较结果需要8个CLK的脉冲,8个CLK的脉冲时间加上采样时间构成了CLKS的长度。

图1 8位SAR A/D转换器结构图

2.2 改进型分裂式DAC

单调电容开关时序,输入信号通过电容的上极板采样。一个N位的差分SAR ADC仅需要2N-1个单位电容,相对于传统电容时序减少了一半。相比传统电容开关时序,单调电容开关整体功耗降低80%[5]。但该设计随着每一次比较后,单调开关时序的DAC共模电压下降。

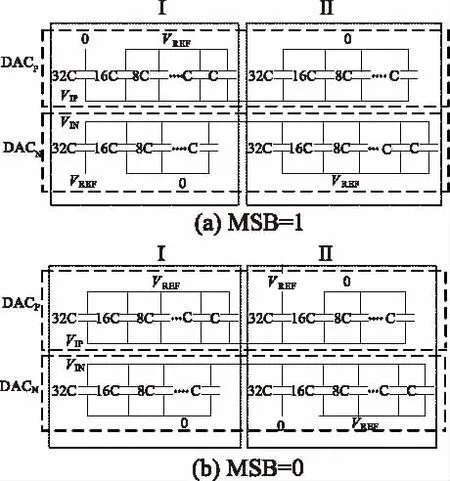

在单调电容开关时序DAC结构的基础上,采用分裂电容结构不仅可以使DAC的共模电压恒定,还可以提高ADC的速度。采样结束后,DACP电容中Ⅰ接高电压,Ⅱ接低电压,DACN相反。第一次比较后,如VIP大于VIN,则DACP中Ⅰ部分的最高位32C接地,DACN中Ⅱ部分的最高位32C接电源电压,其余不变,如图 2(a);若 VIN大于 VIP,则 DACP中Ⅱ部分的 32C接电源电压,DACN中Ⅱ部分的32C接地,其余不变,如图2(b)[6]。但是,不管是哪种结构的DAC,如果单位电容较大,最高位的电容值将很大,导致最高位的置位时间增加,速度也就降低了。

图2 分裂电容结构开关动作

在高速ADC的设计中,一般采用较小的单位电容,这样能缩短每次DAC的置位时间,尤其是最高位的置位时间。由于最高位电容较大,需要较大的置位时间,因此严重限制了ADC的速度。根据电容的充放电时间公式(1),通过增大电路中管子的尺寸,的确会减小电阻,但功耗会更高,而且电阻减小幅度有限,DAC置位的速度也并不会有明显增加。同时增加管子尺寸后也会引起更大的寄生电容,这样就会影响采样的准确性[7]。

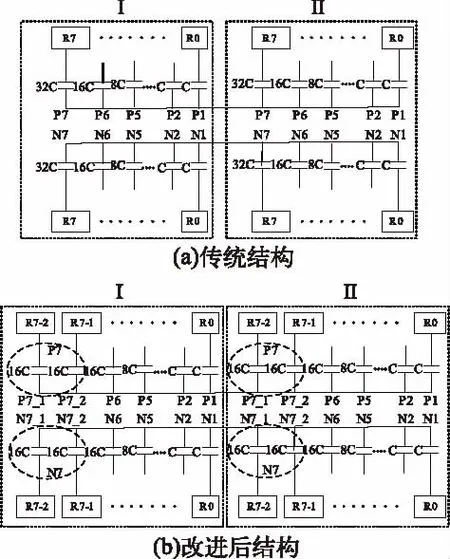

本文提出了一种可以提高速度的新颖结构,即将MSB电容替换成两个小电容并联(容值与替换前的电容相等),用P7_1和P7_2(N7_1和N7_2)来表示。通过这种方式,MSB电容成为两个相对较小的电容。由于每个电容需要一个SAR寄存器来触发,并且MSB电容被替换成两个小电容,因此新提出的ADC需要增加一个SAR寄存器。在比较器产生MSB比较结果之后,它们被发送到两个相同的SAR寄存器,然后产生两个相同的控制信号来驱动这两个小电容器,传统结构及改进后的DAC电路结构如图3所示。

图3 传统DAC结构与改进后的DAC结构

本设计中采用同步时钟,每位转换时间与最高位相同,最高位的置位时间被缩减一半,ADC的转换速度即可提高一倍。

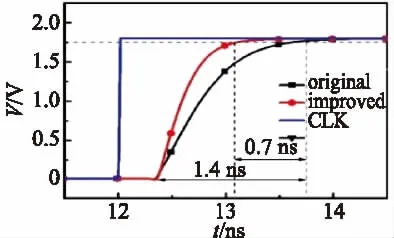

由于最高位的电容减小一半,根据公式(1)可知最高位的置位时间被缩减近一半。DAC采用180 nm工艺下的16 fF电容作为单位电容,通过Spectre仿真可得到传统和改进后两种结构的ADC的最高位时序图,如图4所示。图4中original为传统结构的时序,improved为改进后结构的时序。两条曲线电压增加到1.74 V的时间间隔为0.7 ns,传统结构电压从0增加到1.74 V所需时间为1.4 ns,可以明显看出DAC改进后最高位的置位时间缩短了一半,ADC的速度也提高了一倍。

图4 传统(original)和改进后(improved)两种结构最高位输出曲线

3 关键电路设计

3.1 比较器

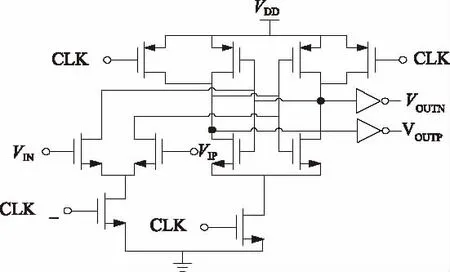

比较器在时钟的控制下比较差分电容的输出,并将结果传到SAR逻辑存储,然后再进行下一次比较。在CLK为低电平时,比较器的输出被置高位,CLK为高电平时,比较器进行比较。本文中采用的两级比较器结构如图5所示,第一级为放大级,第二级为再生级[8]。

图5 比较器结构图

在传统结构中ADC的转换速度受DAC的最高位置位时间影响较大,因此每两次比较中间的间隔时间较大。采用本文中的DAC结构可缩短两次比较的间隔时间,因此比较器的效率被提高了。

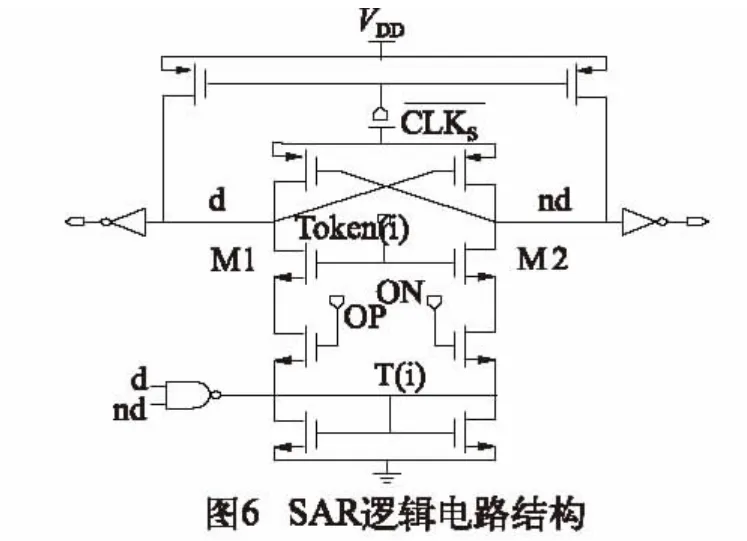

3.2 SAR寄存器

SAR寄存器在ADC中的作用是根据比较器的输出依次得到数字码并将其锁存输出到DAC电容中,驱动差分电容DAC完成逐次逼近的过程。一个SAR寄存器输出一个数字码,8 bit的ADC本应该需要8个SAR逻辑来完成整个转换过程。本文中为了减小最高位的置位时间,最高位电容被替换成了两个小电容,分别为P7_1和P7_2(N7_1和N7_2)。P7_1和P7_2(N7_1和N7_2)共同构成 P7(N7)这一位的电容,在驱动信号到来时,需要同时打开P7_1和P7_2(N7_1和N7_2)这两位的开关,因此需要两个SAR寄存器的输出信号来打开P7_1和P7_2(N7_1和N7_2)的开关,最高位则需要2个SAR寄存器。综上,本文中的8位SAR ADC需要9个SAR寄存器。SAR寄存器的结构见图6[6]。

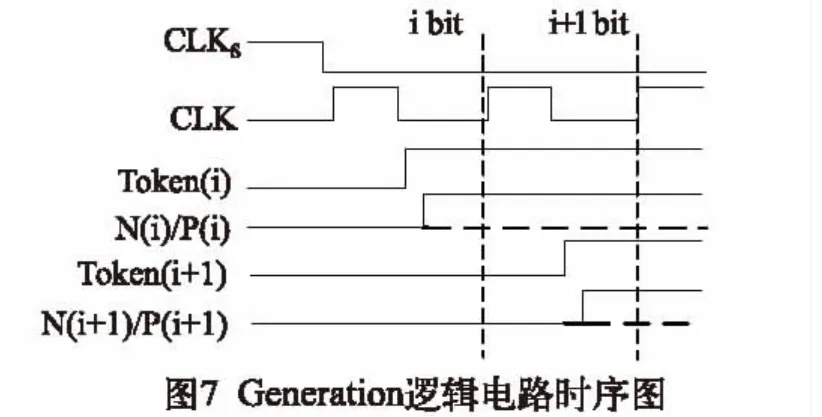

SAR寄存器在CLKS为高电平时,SAR寄存器的输出被置为低电压。CLKS为低电平时,最高位的generation在CLK驱动下产生一个高电平信号,根据比较器比较出的结果则产生一次数字码,系统进入下一次比较,时序见图7。

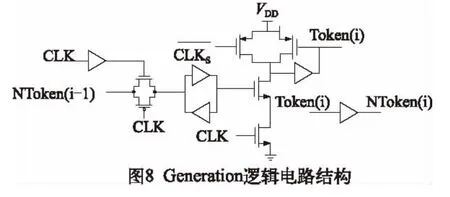

3.3 Generation逻辑电路

Generation逻辑电路的作用是驱动SAR寄存器工作。一个SAR寄存器需要一个generation的驱动,但P7_1和P7_2的SAR只需同一个generation来驱动,因此generation只需要8个模块。在CLKS信号为低时,每个CLK的高电平产生一个高电平TNEXT信号,SAR逻辑在TNEXT信号、CLKS信号、CLK信号的驱动下产生正确的逻辑。按照逻辑关系定义采用CMOS逻辑门电路实现,时序逻辑见图7,电路结构见图8。

4 版图及仿真结果讨论

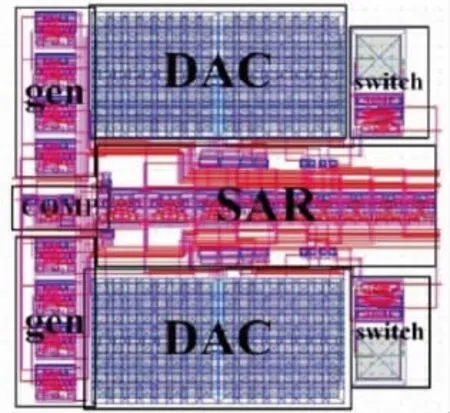

采用本文提出的DAC结构设计了一款8位51MS/s的SAR ADC,ADC版图见图9,ADC版图的面积为170 μm×150 μm。电路仿真采用 Spectre软件进行,在电源1.8 V、输入信号频率25 MHz、采样频率51 MHz的条件下对整体电路进行仿真。

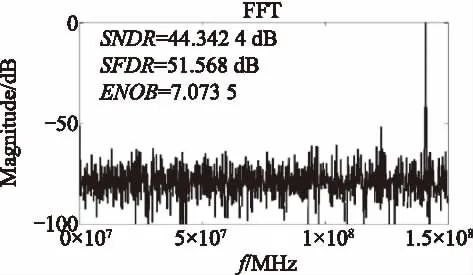

通过快速傅里叶变换(FFT)进行频谱分析。由图10的频谱分析图可知信号噪声失真比(SNDR)为44.3dB,无散杂动态范围(SFDR)为51.6 dB,有效位数(ENOB)为7.07,获得了较好的性能参数。

图9 SAR ADC版图

图10 SAR ADC输出信号频谱图

随着采样频率的变化,ADC的 ENOB、SNDR、SFDR、功耗的变化情况见图11,随着采样频率的增大,ENOB、SFDR和SNDR均有所下降。

图11 ADC在不同采样频率下的性能

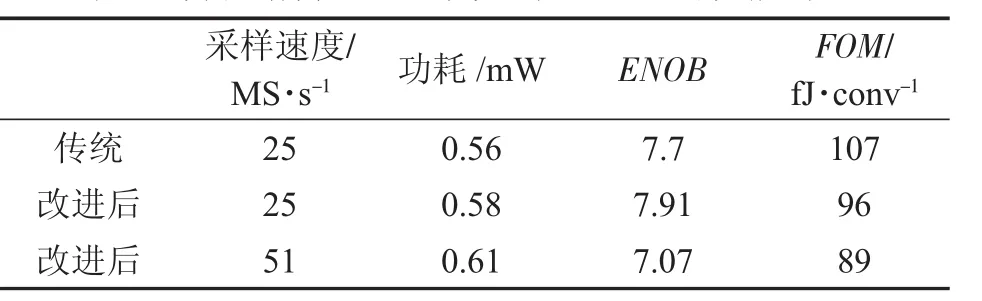

从表1中可以看出传统结构ADC与改进后ADC的性能对比,为了增加对比性,对改进后的ADC同样做了25 MS/s采样速度的仿真。传统ADC的采样速度为25 MS/s,功耗为0.56 mW,FOM值为107 fJ/conv。增加了一个SAR寄存器后,ADC的采样速度提高了一倍,而ADC的功耗仅增加了0.05 mV,FOM值也减小了18 fJ/conv。改进后的ADC在51 MHz的采样频率下工作时有效位数只有7.07,这是因为采样频率高了,有效位数会有所降低。改进后的ADC在25 MHz的采样频率下有效位数为7.91,因此改进后的ADC不仅能提高转换速度,也能提高精度。

表1 传统结构ADC与改进后ADC的性能对比

由上述分析可知,改变DAC中最高位电容与寄存器的连接,可实现相对于传统结构更高的转换速度,实现了51MS/s的采样速度,同时减小了ADC的FOM值。

5 结论

本设计改进了传统结构的ADC,实现了51 MS/s的采样频率,0.61 mW的功耗,89 fJ/conv的FOM值,7.07 dB的有效位数。与传统结构相比,本文不改变DAC中的电容大小、个数,仅仅在差分结构两端的最高位各增加一个寄存器资源,在其他模块电路不用改变的条件下,改进了DAC与寄存器的连接,提高了SARADC的转换速度。本设计中的方法同样也适用于其他有电容充放电问题的电路中,以提高电路的速度。