MTM反熔丝薄膜单项工艺DOE试验设计开发方法

郑若成,曾庆平,吴素贞,王印权,吴建伟,徐海铭,洪根深

(中国电子科技集团公司第五十八研究所,江苏无锡 214072)

1 引言

反熔丝电路因其具有高集成度、高速、低功耗、高保密性、高可靠性[1]、抗辐射特性好[2-4]、与传统CMOS工艺兼容等优点,近年来在业界获得广泛的研究和应用。其产品广泛应用于军事、航空、航天等领域。MTM反熔丝单元是一种典型的反熔丝器件,由上下金属电极和两电极之间的反熔丝薄膜介质层组成,其结构如图1所示。MTM反熔丝单元在未编程状态下处于高阻状态,阻值通常大于1 GΩ,编程后单元则处于低阻状态,阻值通常小于100 Ω,可用于非易失性存储器(PROM)及可编程逻辑器件(FPGA)电路中。由于MTM反熔丝单元的非挥发性,电路不会因辐射导致数据丢失,因此常被用于对抗辐射特性有较高要求的空间应用系统中,已经成为空间领域的主流技术之一。

图1 MTM单元结构示意图

目前国际上研究MTM反熔丝的单位以美国ACTEL公司为代表,经过近几十年的技术积淀,工艺水平已达到0.15 μm。国内方面,中国电科第58所在MTM反熔丝工艺方面也进行了较深入的研究,技术能力达到0.18 μm工艺技术水平。

MTM反熔丝薄膜工艺是MTM反熔丝单元最关键的单项工艺,直接决定反熔丝单元的常态、编程、可靠性以及抗辐照等特性。该薄膜工艺可以采用PVD(Physical Vapor Deposition)设备、蒸发设备或者CVD(Chem ical Vapor Deposition)工艺设备进行开发。不同工艺形成的MTM薄膜介质特性会有一定差异。鉴于MTM薄膜介质对于MTM反熔丝单元的重要性,本文基于CVD工艺设备,提供一种采用DOE试验设计进行单项工艺开发的方法,为科研生产工作中各种关键单项工艺的开发提供参考和借鉴。

2 DOE试验设计

本次试验基于工艺线CVD设备进行薄膜工艺菜单开发,主要工艺参数包括温度、射频(RF)、反应气体1流量、基座间距、淀积时间等。其中射频和反应气体1流量、基座间距等对MTM介质特性影响较大。在进行DOE试验设计前,一般需要有一个基准菜单,这个菜单可以基于工艺线经验或者工艺线类似的菜单(对于新引进设备,一般可以要求供应商提供一个基准菜单),基准工艺菜单如表1所示。

表1 基准工艺菜单

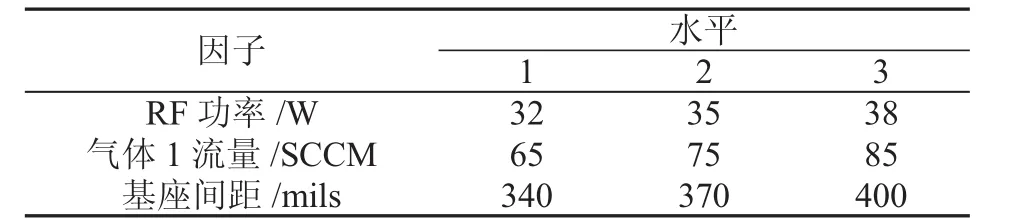

根据机理分析和工艺需要,选定射频功率、气体1流量和基座间距作为DOE试验的输入因子,对薄膜特性影响显著的薄膜厚度均匀性、折射率以及应力作为工艺响应因子,DOE试验设计如表2所示。

表2 DOE试验的因子和水平设置

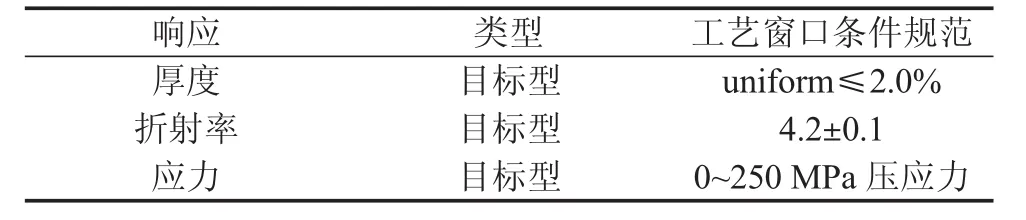

厚度均匀性规范为2%以内,折射率4.2±0.1,应力小于250 MPa,DOE响应参数规范设置如表3所示。

表3 DOE试验的响应设置

3 试验与数据分析

3.1 初步工艺调试

MTM介质淀积速率、均匀性等随基座间距、RF功率、反应气体1流量变化如表4所示。RF增加,淀积速率增大,均匀性变差,RF=40 W时均匀性均不满足规范要求,需要进一步降低射频功率。气体1流量减小淀积速率减小,均匀性变差,但流量在75 sccm时部分条件均匀性满足规范要求,可进一步增大拉偏确认工艺窗口。但各参数之间存在交互影响,因此需要更多验证以综合考虑。基座间距减小,淀积速率增加且均匀性变好,基座间距400 mils及以下均匀性均满足规范条件,实际需进一步降低拉偏。引起均匀性变化的主要原因是边缘点厚度变化,当基座间距减小和RF减小时,边缘处厚度增加并接近均值。基座间距变小,边缘增加的厚度较多,弥补了原来中心与边缘极差较大的情况,改善了均匀性。射频功率减小,均匀性增加,趋势相仿。另外由表4中的数据可知,淀积时间越长,淀积速率越大,薄膜均匀性和折射率略有减小,但变化不大,因此淀积时间对薄膜介质特性影响较小,且实际工艺中时间主要由薄膜厚度决定,因此在后续各工艺参数确认过程中将主要考虑基座间距、射频功率和气体1流量3个主要因素。

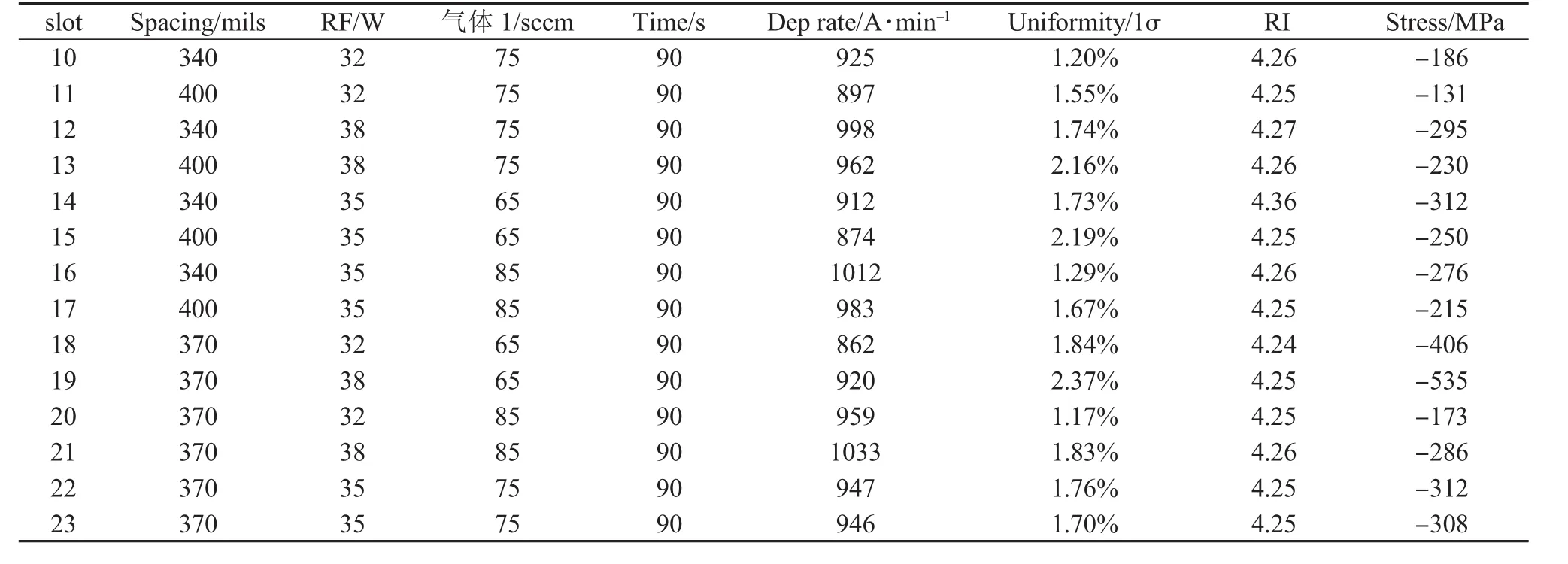

3.2 工艺窗口确认

通过工艺初步调试,与均匀性、折射率、应力有关的主要因素包括工艺基座间距、射频和气体1流量。根据初步调试的结果可知,基座间距以370 m ils为中心进一步降低拉偏,射频功率以35 W为中心进一步降低拉偏,气体1流量进一步增大拉偏,工艺拉偏条件及参数测试结果如表5所示。

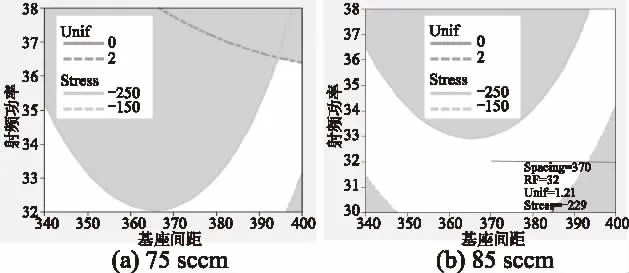

根据表5中的试验结果可知,采用交互影响的二阶效应对射频功率与基座间距对均匀性和应力的影响进行分析,当气体1流量固定在65 sccm时,基座间距从340 mils到400 mils,射频从32 W到38 W没有工艺窗口。当反应气体1流量固定在75 sccm时,工艺窗口较小。将气体1固定在85 sccm时,基座间距从340 mils到400 mils,射频从32 W到38 W存在良好的工艺窗口,如图2所示。故推荐工艺条件为图2(b)中空白区域的中心位置,即基座间距=370 mils、RF=32 W、反应气体1的流量为85 sccm。

表4 初步工艺调试结果

表5 工艺窗口确认试验结果

图2 气体1流量为75 sccm、85 sccm时窗口确认结果

3.3 工艺一致性验证

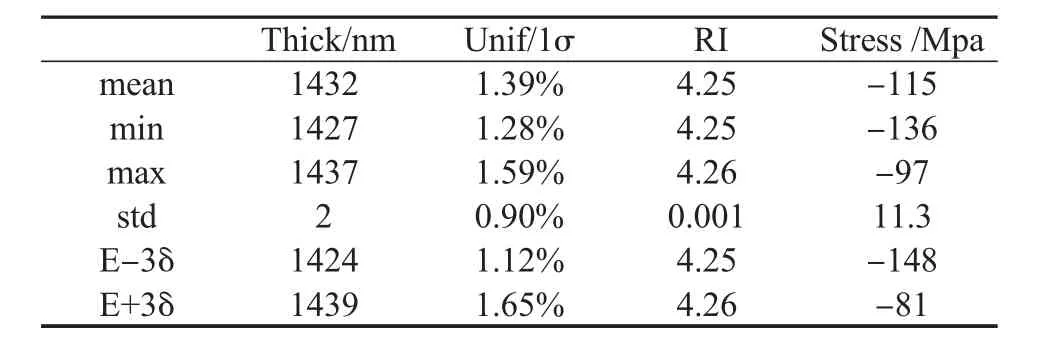

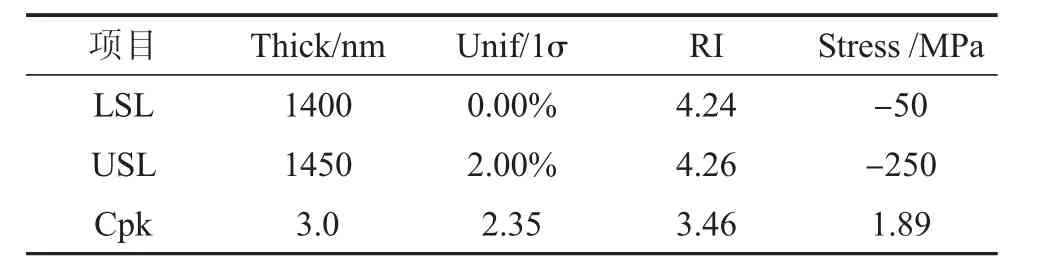

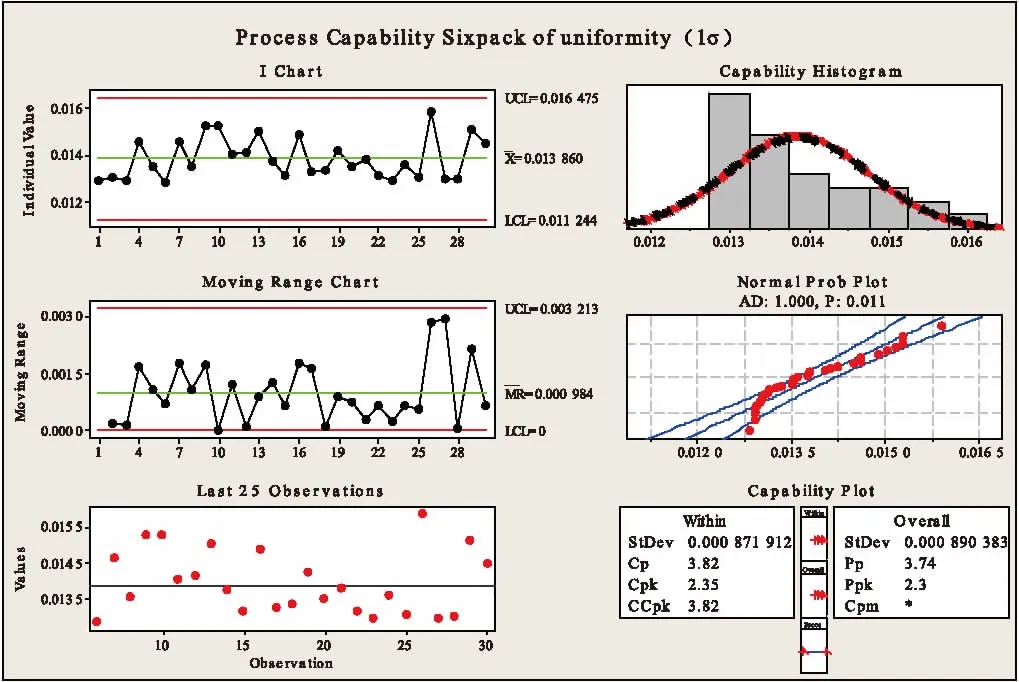

根据DOE试验最佳工艺条件基座间距370 mils、射频功率32 W、气体1流量85 sccm,进行30片wafer流片验证重复性,对此工艺重复性验证的30片wafer进行膜厚、均匀性、折射率、应力参数重复性统计分析,如表6所示,对应的30片wafer膜厚均匀性统计如图3所示。由表6可知,重复流片验证各项参数均满足指标要求,根据重复流片验证3σ确定各参数控制规范。

表6 重复性流片验证统计分析结果

根据多批次流片结果统计制定的规范以及相应的Cpk值见表7。

表7 各监控参数规范与相应的Cpk值

4 结论

基于工艺线CVD工艺设备,通过对MTM薄膜特性影响较大的输入因子射频RF、气体1流量以及基座间距等进行试验设计,针对厚度均匀性、折射率以及应力3种工艺参数响应,初步找到了“最佳”的工艺条件:基座间距约370 m ils,射频功率约32 W,反应气体1流量约85 sccm。

图3 介质均匀性重复性统计分析结果

本文进行的DOE试验设计还有几个输入因子,如工艺温度和反应气体2的流量等,为简化数据分析,将其设为一个定值;在响应上,除了工艺参数响应之外,还需考虑反熔丝单元的电特性响应,包括常态特性、编程特性以及可靠性等,因此基于工艺参数响应确定的“最佳”工艺条件并不是已经完全确定的具体值,而是具有一定容宽范围的,对此容宽范围的反熔丝单元进行电特性评价,当反熔丝单元电特性满足要求后,反熔丝薄膜工艺菜单才最终确定下来。尽管本文提供的DOE试验设计还不完善,但不影响基于DOE试验设计在单项工艺开发中的应用。

基于PVD设备,采用DOE试验设计单项工艺开发方法,本单位完成了反熔丝薄膜介质工艺菜单的开发,根据该工艺制作的MTM反熔丝单元漏电和击穿一致性良好,编程前开态电阻、编程后电阻以及可靠性均满足产品使用要求。