基于脉冲方法的超短栅长GaN基高电子迁移率晶体管陷阱效应机理∗

周幸叶 吕元杰 谭鑫 王元刚 宋旭波 何泽召 张志荣 刘庆彬 韩婷婷 房玉龙 冯志红

(河北半导体研究所,专用集成电路国家级重点实验室,石家庄 050051)(2018年3月18日收到;2018年5月7日收到修改稿)

1 引 言

作为新一代高频、高温和大功率固态电子器件,宽禁带GaN基高电子迁移率晶体管(HEMTs)在半导体领域引起了广泛关注,并在微波功率应用领域取得了巨大成功,一些性能优良的电子器件与集成电路已经进入市场[1].然而,这类器件的潜在优势却受到电流崩塌及自热效应等其他可靠性问题的制约[2−19],器件性能难以达到理论值.器件中缺陷的存在被认为是这些寄生效应的主要原因,材料缺陷会作为陷阱中心引起器件性能的退化.多年来,世界各国的研究人员已经投入大量时间和精力来研究分析深能级陷阱效应.脉冲I-V测试经常被用于表征和分析GaN基器件的电流崩塌情况[2−7].除此之外,瞬态技术也是研究GaN基HEMT中深能级陷阱的一种非常有效的方法,文献[4–8]采用瞬态方法研究了深能级陷阱对GaN基器件动态特性的影响.基于二维数值仿真可以进一步分析器件中的陷阱效应物理机制[9−17],Miccoli等[11]将栅延迟和漏延迟现象分别归咎于施主型表面陷阱和受主型体陷阱.然而,随着器件频率越来越高,器件尺寸变得越来越小,对小尺寸器件中深能级陷阱的表征变得越发困难.目前,对GaN基HEMT中深能级陷阱的研究大都是基于大尺寸器件,对小尺寸器件的可靠性研究工作较少.

本文基于脉冲I-V测试和二维数值瞬态仿真对超短栅长(Lg=80 nm)AlGaN/GaN金属氧化物半导体高电子迁移率晶体管(MOSHEMT)的动态特性进行了深入研究,测试了不同静态偏置条件下的脉冲I-V特性曲线,提取出了器件电流崩塌与静态偏置电压之间的依赖关系,分析了深能级陷阱对AlGaN/GaN MOSHEMT器件动态特性的影响.结果表明,AlGaN/GaN MOSHEMT器件的电流崩塌与栅极静态偏置电压之间为非单调变化关系,这是由栅漏电注入和热电子注入两种陷阱机制共同作用的结果.为了进一步抑制电流崩塌,可通过改善栅介质的质量以减小栅漏电或提高外延材料质量以减少缺陷密度等措施达到抑制陷阱效应的目的.

本文第2部分主要描述器件样品的结构和制备工艺;第3部分对AlGaN/GaN MOSHEMT的脉冲测试和数值仿真结果进行详细的分析和讨论;第4部分对本文工作进行总结.

2 器件结构与制备

图1给出了所制备的AlGaN/GaN MOSHEMT器件结构示意图,外延材料通过在2英寸(1英寸=2.54 cm)(0001)面蓝宝石衬底上采用金属有机化学气相淀积方法(MOCVD)制得,AlGaN/GaN异质结构从下至上包括2µm厚的无人为掺杂GaN缓冲层、1 nm厚的AlN插入层和24 nm厚的Al0.24Ga0.76N势垒层,室温下霍尔测试显示二维电子气(2DEG)浓度和电子迁移率分别为9.5×1012cm−2和2014 cm2·V−1·s−1.

器件样品的制备始于台面隔离,首先通过耦合等离子体(ICP)干法刻蚀获得器件台面,然后采用Ti/Al/Ni/Au复合金属形成源/漏电极,并在氮气氛围下850°C快速退火30 s形成欧姆接触.通过电子束直写曝光将栅的光刻胶图形定义好后,采用电子束蒸发在样品表面淀积一层3 nm厚的金属铝,并将其置于空气中24 h,使金属铝发生氧化,从而形成Al2O3作为栅介质,之后淀积Ni/Au金属并剥离,形成栅电极.基于自氧化的Al2O3可实现栅介质的自对准[20−22],即仅在栅电极下方存在栅介质.最后,器件采用50 nm厚的SiNx进行钝化.T型栅位于源漏之间,栅长Lg=80 nm,源漏间距Lsd为4µm.

所制备的80 nm栅长AlGaN/GaN MOSHEMT器件样品的直流测试结果如图2所示,图2(a)和图2(b)分别为器件的转移特性曲线和输出特性曲线,同时图2(a)给出了相应偏置电压下的栅电流曲线.值得注意的是,在关断状态下器件的栅漏电大于源漏电流,表明器件在关断状态下的漏电流Ids主要由栅电流Igs决定,如图2(a)所示.此外,由于栅长较短,器件存在一定的短沟效应,即随着漏端电压的增大,漏电流随之增加,如图2(b)所示.

图1 AlGaN/GaN MOSHEMT器件结构示意图Fig.1.Schematic cross-section structure of AlGaN/GaN MOSHEMT.

图2 80 nm栅长AlGaN/GaN MOSHEMT器件的直流特性曲线 (a)转移特性曲线;(b)输出特性曲线Fig.2.I-V characteristics of AlGaN/GaN MOSHEMT with 80 nm gate length:(a)Transfer curves;(b)output curves.

3 结果与讨论

为了研究深能级陷阱效应对小尺寸短栅长AlGaN/GaN MOSHEMT动态特性的影响,我们对所制备的器件样品进行了不同静态偏置条件下的脉冲I-V测试,并对器件进行了二维数值瞬态仿真,分析了深能级陷阱导致的电流崩塌的内在物理机制.本节中我们对脉冲I-V测试结果和瞬态仿真结果进行详细的分析和讨论.

3.1 脉冲I-V测试

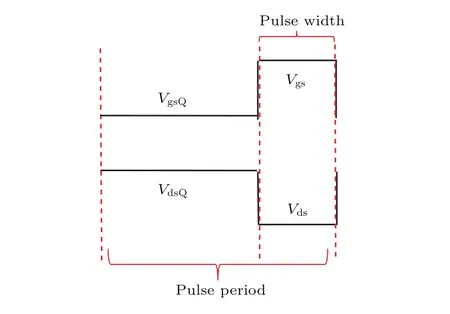

在脉冲I-V测试时,在每个脉冲周期,器件的栅极和漏极首先被偏置在静态点(VgsQ,VdsQ)进行陷阱填充,在此期间,器件中的陷阱被电子填充,然后偏置电压从静态偏置点跳到测试点(Vgs,Vds),被俘获的电子随着时间的推移得到释放,从而得到被测器件的脉冲I-V特性曲线.脉冲I-V测试的偏置条件如图3所示,为了使陷阱在静态偏置阶段俘获更多的电子,我们选取了较长的脉冲周期和较短的脉冲宽度,除非特殊说明,本文中的脉冲周期和脉冲宽度分别选取10 ms和1µs.

图3 脉冲I-V测试电压偏置条件Fig.3.Bias voltage setup for pulsed I-V measurement.

图4给出了不同静态偏置条件下AlGaN/GaN MOSHEMT的脉冲输出特性曲线,图4(a)为不同静态偏置条件下的脉冲I-V曲线,栅压从−9–1 V之间变化,可以看出,与初始状态(VgsQ,VdsQ)=(0 V,0 V)相比,不同静态偏置点的饱和电流由于陷阱效应都发生了下降,即出现了电流崩塌现象.图4(b)给出了栅压Vgs=1 V时不同栅极静态偏置条件下的脉冲I-V测试结果,栅极静态偏置电压VgsQ从−8–0 V之间变化.结果表明,电流崩塌与栅极静态偏置电压有着密切的依赖关系.

为了进一步研究陷阱效应对AlGaN/GaN MOSHEMT动态特性的影响,我们对器件样品在漏端静态偏置点VdsQ分别为0,5和10 V时进行了脉冲I-V测试,并提取出了相应的电流崩塌与栅极静态偏置电压VgsQ的依赖关系,如图5所示.电流崩塌在此定义为栅压Vgs=1 V,漏压Vds=10 V时不同静态偏置条件 (VgsQ,VdsQ)下与初始状态(VgsQ,VdsQ)=(0 V,0 V)相比饱和电流的减小量.同时,图中给出了相应偏置条件下的栅泄漏电流或亚阈区的漏源电流,Vgs(Q)和Vds(Q)分别表示栅极和漏极的静态偏置电压VgsQ和VdsQ或测试电压Vgs和Vds.

图4 不同静态偏置条件下AlGaN/GaN MOSHEMT的脉冲I-V特性曲线 (a)不同栅压;(b)栅压为1 VFig.4.Pulsed I-V characteristics of AlGaN/GaN MOSHEMT with different quiescent bias voltages:(a)Pulsed output curves with various gate voltages;(b)pulsed output curves with Vgs=1 V.

从图5可以看出,当漏极静态偏置电压为VdsQ=0 V时,电流崩塌随着栅极静态偏置电压VgsQ的增加而单调减小(如图5(a));而当漏极静态偏置电压增大为VdsQ=5 V时,电流崩塌随着栅极静态偏置电压VgsQ的增加并非单调变化,即电流崩塌先是随着栅极静态偏置电压VgsQ的增加而缓慢下降,然后逐渐增加并达到一个峰值,随后又开始减小(如图5(b));图5(c)表现出与图5(b)类似的变化趋势.此外,可以看出,随着漏极静态偏置电压VdsQ的增加,电流崩塌随之增大.

图5 电流崩塌与栅极静态偏置电压的依赖关系 (a)VdsQ=0 V;(b)VdsQ=5 V;(c)VdsQ=10 VFig.5.Current collapse as a function of gate quiescent bias voltage:(a)VdsQ=0 V;(b)VdsQ=5 V;(c)VdsQ=10 V.

电流崩塌与栅极静态偏置电压的这种非单调变化依赖关系可以通过两种陷阱效应机制的共同作用来解释:1)栅漏电注入相关的陷阱机制;2)热电子注入相关的陷阱机制.当VdsQ=0 V时,器件内部没有沟道电流或热电子,所以栅漏电注入相关的陷阱机制对器件的电流崩塌占主导地位,随着静态偏置电压VgsQ的增加,栅漏电减小,从而由于栅漏电注入并被陷阱俘获的电子减少,器件的电流崩塌缓慢减小.图5(a)中给出的电流崩塌与栅泄漏电流的变化趋势相符合,进一步印证了这一理论,该现象与文献[7]中的结果一致.当VdsQ=5 V或10 V时,电流崩塌随着栅极静态偏置电压的增加而非单调变化,当器件处于关断状态时,漏源电流Ids主要由栅电流Igs决定(如图2(a)所示),沟道内没有形成2DEG,从而沟道内也就没有热电子,所以,电流崩塌主要由栅漏电注入陷阱机制导致,此时电流崩塌与栅漏电Igs变化趋势保持一致,如图5(b)和图5(c)所示;随着栅电压增加,器件逐渐开启,沟道内开始形成二维电子气,热电子注入陷阱机制开始占据主导地位,栅极静态偏置电压越大,沟道电流越大,被陷阱俘获的热电子越多,导致电流崩塌增加,此时电流崩塌与亚阈区漏源电流Ids的变化趋势非常符合,且与文献[7]的结果相一致,如图5(b)和图5(c)所示.而且,漏极电压越高,热电子能量越大,越容易被陷阱俘获,从而引起器件电流崩塌越大.但是,与文献[7]结果不同的是,当栅极静态偏置电压继续增加时,电流崩塌不再增加反而开始减小.这可能由多种原因导致:一是栅漏电注入陷阱机制导致的电流崩塌不断减小;二是热电子的能量由于严重的电子散射和自热效应影响而降低,从而使热电子注入陷阱机制导致的电流崩塌减小.

3.2 器件瞬态仿真

瞬态技术是研究AlGaN/GaN HEMT中陷阱的一种非常有效的方法.为了更深入地分析陷阱效应的内在物理机制,我们对GaN基HEMT器件进行了二维数值瞬态仿真.

图6 仿真模型校准结果Fig.6.Calibration of the simulation model.

除非有特殊说明,本模型中采用的参数如下:将极化效应等效为位于材料界面的固定电荷,即位于AlGaN势垒层与GaN缓冲层界面处的正极化电荷(面密度为9.5×1012cm−2),施主型表面陷阱和受主型体陷阱的能级距离导带底(Ec)分别为Ed=0.8 eV和Ea=0.5 eV;施主型表面陷阱位于钝化层和GaN盖帽层之间的界面,浓度为Nd=9.5×1012cm−2,而受主型体陷阱均匀分布于GaN缓冲层,浓度为Na=1×1017cm−3;假设电子和空穴的俘获面积均为σn,p=1×10−15cm2,栅电极的肖特基势垒设为0.9 eV.考虑到热电子在体陷阱效应中所起的作用,采用流体力学模型,模型中包含了电子迁移率退化模型(即high field saturation和doping dependence)、复合模型(即Shockley-Read-Hall,Auger和Radiative)以及热效应模型.

首先,对所建立的器件模型进行校准.图6给出了仿真得到的直流特性曲线与测试数据的对比结果,可以看出,仿真结果与测试数据符合得很好,验证了模型的正确性.

在进行瞬态仿真时,器件栅电压设置为从静态偏置点VgsQ跳变到测试电压Vgs=0 V或1 V,而漏电压Vds保持10 V不变.图7给出了不同栅极静态偏置电压条件下器件的瞬态仿真结果,可见当器件在时间t=1 ms开启后,瞬态电流随着时间的增加而增大,直至达到一个稳定电流值,而且瞬态电流依赖于栅极静态偏置电压,如图7(a).在此,电流崩塌定义为稳定电流值与t=1 ms处的初始电流值之差,从而得到电流崩塌与栅极静态偏置电压的依赖关系,如图7(b)所示.可以看出,仿真得到的电流崩塌随栅极静态偏置电压的变化结果与测试结果具有类似的非单调变化趋势.

图7 器件瞬态仿真结果 (a)瞬态电流;(b)电流崩塌与栅极静态偏置电压的关系Fig.7.The transient simulation results:(a)Transient currents;(b)current collapse as a function of gate quiescent bias voltage.

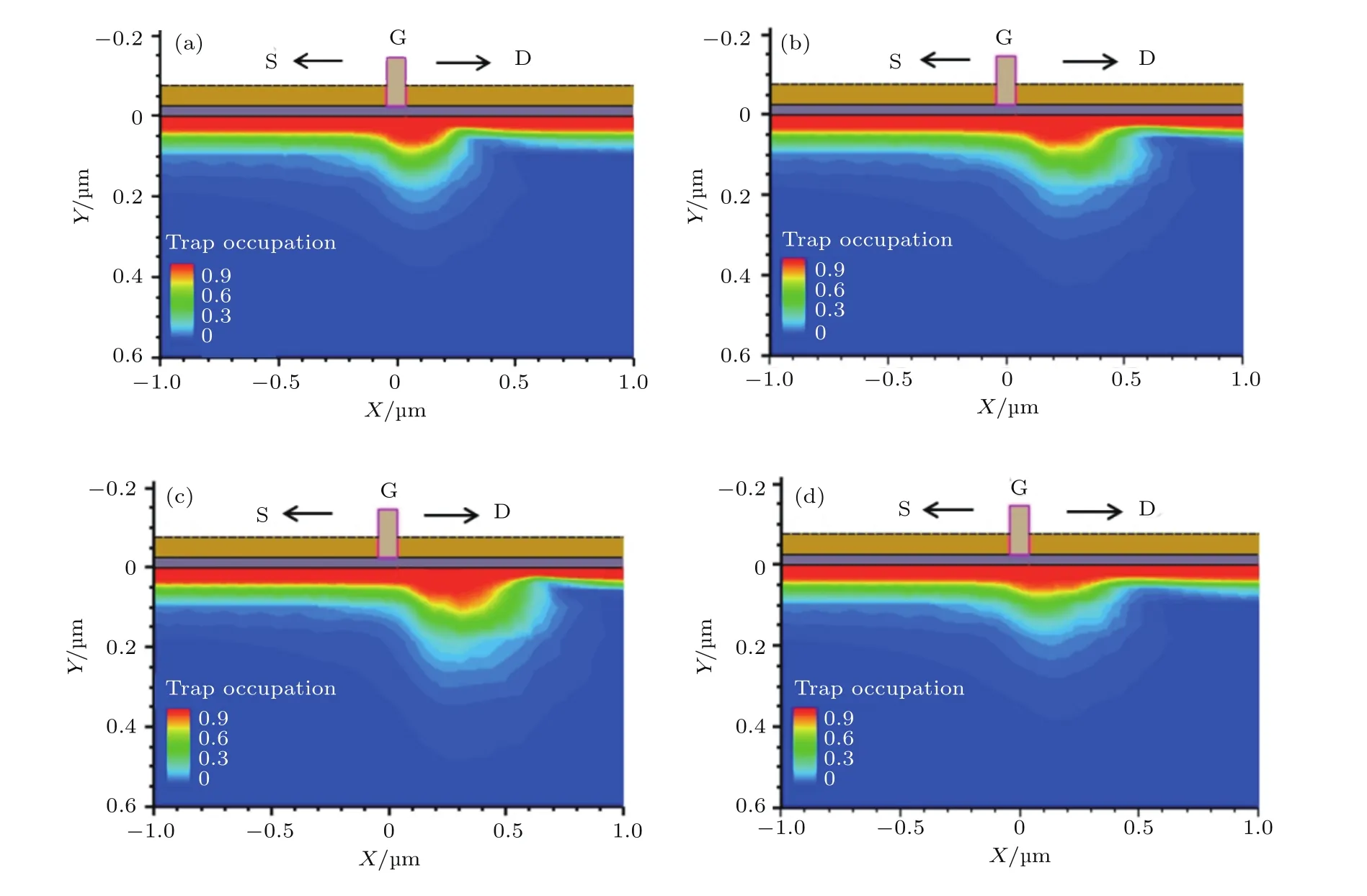

图8 电子填充陷阱分布图 (a)VgsQ=−8 V;(b)VgsQ=−5 V;(b)VgsQ=−4 V;(d)VgsQ=−2 VFig.8.The trap occupation pro file:(a)VgsQ=−8 V;(b)VgsQ=−5 V;(c)VgsQ=−4 V;(d)VgsQ=−2 V.

如之前所述,电流崩塌与栅极静态偏置电压的非单调变化关系是栅漏电注入陷阱机制和热电子注入陷阱机制两者共同作用的结果.仿真得到的电子填充陷阱分布图可进一步证明这一点.图8给出了栅压Vgs开启为0 V时不同栅极静态偏置点器件中电子填充陷阱的分布图,其中,X轴沿沟道方向,而Y轴与沟道方向垂直.可以看出,从−8 V到−4 V,随着栅极静态偏置电压的增加,被俘获的电子增多,但是当栅极静态偏置电压继续增大时(如VgsQ=−2 V),被俘获的电子反而减少,这与测试结果相一致.

4 结 论

基于脉冲I-V测试和二维数值瞬态仿真,对所制备的超短栅长(Lg=80 nm)AlGaN/GaN MOSHEMT的动态特性进行了深入研究,测试了不同静态偏置条件下的脉冲I-V特性曲线,提取出了器件电流崩塌与静态偏置电压之间的依赖关系,并结合二维数值瞬态仿真和测试结果,分析了相应深能级陷阱效应的内在物理机制.结果表明,由于栅漏电注入和热电子注入两种陷阱机制共同作用,导致AlGaN/GaN MOSHEMT器件的电流崩塌随着栅极静态偏置电压的增加呈非单调变化趋势.因此,根据研究结果推断,为了进一步抑制电流崩塌,可通过改善栅介质的质量以减小栅漏电或提高外延材料质量以减少缺陷密度等措施达到抑制陷阱效应的目的.