基于磁电耦合效应的基本电路元件和非易失性存储器∗

申见昕1)2) 尚大山1)† 孙阳1)2)‡

1)(中国科学院物理研究所,北京 100190)

2)(中国科学院大学物理科学学院,北京 100049)

(2018年4月17日收到;2018年4月26日收到修改稿)

1 引 言

现代信息技术的快速发展对信息存储器提出了越来越高的要求.根据数据保持特点,存储器基本上可以分为易失性和非易失性两大类.所谓易失性,即在外电场去除后,存储的数据随即消失;而非易失性意味着在外电场去除后,数据仍然能够保存下来.目前占据存储器市场主流的易失性存储器主要是动态随机存储器(DRAM)和静态随机存储器,非易失性存储器主要是磁性硬盘和快闪存储器.随着科学技术的发展,信息化产品对于存储器的存储密度、擦写速度、功耗以及非易失性等性能提出了更高的要求.为了提高存储性能,人们在现有半导体工艺进一步改进的同时,不断寻求新的存储物理机制,开发新型非易失性存储器件,其中包括利用材料的自发极化开发的铁电存储器(FRAM)[1]、利用磁电阻效应开发的磁性随机存储器(MRAM)[2]、利用材料可逆相变开发的相变随机存储器[3]以及利用电致阻变效应开发的阻变随机存储器(RRAM)等多种非易失性存储技术[4].

多铁性材料是近年来发展出的一类功能材料,它有望实现新型的存储机制.这种材料具有两种或两种以上铁性体的特征(铁电序、铁磁序和铁弹序),并且这些铁序之间存在直接或间接耦合作用,可以是单相材料也可以是两相或多相复合材料[5].其中,铁磁性和铁电性的相互耦合使得电场控制磁性或磁场控制电性成为可能,这种物理特性为信息存储提供了额外的物理状态自由度,在开发高性能存储器方面显示出巨大的应用潜力.例如,在传统的磁存储器和铁电存储器中,逻辑单元中的“0”和“1”依靠不同方向的剩余磁化(M)或剩余电极化(P)来存储;而在具有磁电耦合效应的多铁性材料中,可以利用正、负磁化强度和正、负电极化强度相互组合,进而形成四态存储,大大提高存储密度[6].这一设想最早被Gajek等[7]所实现.他们采用2 nm厚的多铁性La0.1Bi0.9MnO3外延薄膜作为隧道结中的势垒层,形成铁磁/多铁/非磁性金属的多铁隧道结结构,在4 K温度下利用自旋过滤效应和由电极化强度造成的电阻效应,在不同的电场和磁场作用下实现了四种隧穿电阻状态.Garcia等[8]采用铁磁性金属Fe作为电极制备出了Fe/BaTiO3/La0.7Sr0.3MnO3多铁隧道结,利用铁电极化来改变隧穿电流的自旋极化,在4.2 K低温条件下获得了四种非易失性的隧穿磁电阻状态.随后Pantel等[9]在Co/PbZr0.2Ti0.8O3/La0.7Sr0.3MnO3多铁隧道结中,将实现四阻态的温度提高到了50 K.虽然多铁隧道结结构简单,易于实现高密度存储,但是要求铁电或多铁性材料很薄,难以保证器件在使用过程中保持良好的铁电性或多铁性,而且器件工作温度往往低于室温.如果可以利用多铁性材料的磁电耦合效应,通过电场对磁性的调控,有可能将铁电存储器的高速写入、低功耗与磁存储器的非破坏性、高速读取的优点相结合,构建具有电写-磁读功能的磁电随机存储器[10].

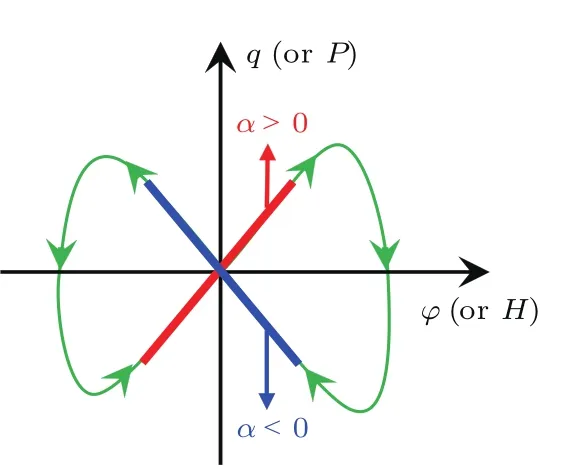

不论是磁存储、铁电存储还是磁电存储,信息都是基于材料的不同物理状态进行保存和记忆的,如磁存储器的磁化(M)和铁电存储器中的电极化(P).多铁性磁电耦合材料除了具有不同的磁化状态和电极化状态之外,还具有一个特别的物理参数——磁电耦合系数(对于正磁电耦合效应表示为α=∂P/∂H;对于逆磁电耦合效应表示为α=∂M/∂E,其中H为磁场强度,E为电场强度),用于表征磁电耦合的强度.实际上,磁电耦合系数的大小和符号与材料的磁化和电极化密切相关,是磁化和电极化在材料中的综合体现.在基于应变调制的磁电耦合异质结中,磁化强度-电场(M-E)关系曲线往往呈现出所谓的蝴蝶形状(butter fl yshaped)[11−15](见图1).蝴蝶形M-E关系的出现主要是由于磁电耦合是通过多铁异质结界面应力的相互作用来实现的.但是,在外电场(或外磁场)去除后,应力不能够保持下来,导致通过应力传递而诱发的磁性变化不能维持,即在外场为零时,所产生的磁化或电极化的变化也回到初始状态.因此,具有蝴蝶曲线型的磁电耦合效应是易失性的,不适合用于非易失性存储.然而,如果考虑磁电耦合系数本身(即M-E曲线的斜率),可以看出当外电场超过某一临界值(如矫顽场)时,电极化方向和磁化方向相互配合使得磁电耦合系数的符号发生改变,并且这种符号变化在外场去除后可以保持.因此,磁电耦合系数具备作为非易失性存储的物理状态所应有的特征.例如,磁电耦合系数的“α>0”和“α <0”可以用于存储信息“0”和“1”.

图1 具有非线性磁电耦合效应的多铁材料q-φ(或P-H)之间形成的蝴蝶形曲线Fig.1.The butter fl y-shaped hysteresis of the q-φ(or P-H)relationship of multiferroics due to the nonlinear magnetoelectric e ff ects.

本文以具有磁电耦合效应的多铁性异质结作为研究对象,利用其独特的非线性电磁关联特性,实现以磁电耦合系数为存储状态的信息存储功能,从全新的角度探索构建基于磁电耦合效应的电写-磁读型非易失性存储器的可能性.在此基础上,发展具有逻辑运算功能和类神经突触记忆特性的新型存储原型器件.

2 基本电路元件关系图

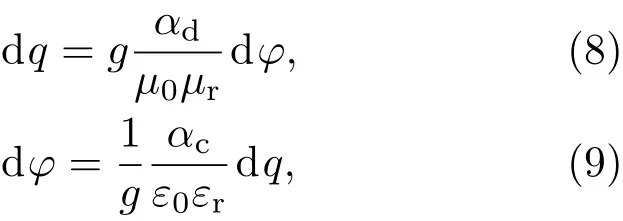

将磁电耦合系数作为信息存储的物理状态,不仅在器件应用方面表现出很大的潜力,而且在基础物理研究和基本电路理论方面也具有重要的意义.在电路理论中,存在三种基本的两端无源线性电路元件,即电容(C)、电感(L)和电阻(R).它们是由电荷(q)、电流(i)、电压(v)、磁通(φ)等四个基本电路变量之间的线性关系来定义的(见图2(a)).1971年,Chua[16]提出存在第四种电路元件可以直接将q和φ联系起来:

由于当时没有真实的电路元件可以真接联系磁通和电荷,Chua对(1)式做了如下变换:

其中,t为时间.因此,可以得到

但是,Chua发现(4)式中M的量纲与电阻R是相同的.为了赋予M一些非平凡的意义,Chua假定M不是一个常数,而是q和t的函数.通过欧姆定律可以定义这种非线性的电阻元件:

M被称为忆阻器(memristor).随后,Chua和Kang进一步将忆阻器的概念拓展到更广泛的非线性动力学系统,称为忆阻系统[17],可以表示为

其中,x代表系统状态变量的一个矢量,f是连续矢量方程.

Chua的工作在当时并没引起人们的关注.在沉寂了近40年之后,美国惠普实验室的Strukov等[18]在2008年宣布发现了满足忆阻器定义的器件.这种忆阻器具有Pt/TiO2/Pt三明治结构,其电学行为表现为具有滞后且过原点的i-v曲线.随后,在忆阻器的启发下,电容和电感所对应的非线性记忆元件,即忆容器和忆感器也被提了出来,并在实验上得到证实[19].但是,忆阻器作为第四个基本电路元件的物理身份仍存在质疑[20].因为,忆阻器实际上是从i-v关系中获得的,而不是来自于最初所提出的φ-q关系,即i-v定义的忆阻器可以在不涉及基本变量φ的条件下正常工作.Mathur[21]指出具有线性磁电耦合效应的材料可以产生M和P的线性耦合,并以此可以推导出φ和q的直接的、线性的关系,应当满足第四个基本电路元件的定义.

对于一个磁电耦合介质,根据Landau理论,其φ-q关系可以表示为[22]

图2 (a)四个基本的电路变量,即电荷(q)、电压(v)、电流(i)和磁通(φ)所构成的三个基本线性电子元器件,即电阻(R)、电容(C)和电感(L);(b)基本电子元器件的完整关系图,基中包括四个线性电子元器件R,C,L和电耦(T)以及四个非线性电子元器件(忆阻器MR、忆容器MC、忆感器ML和忆耦器MT)[22]Fig.2.(a)The four linear fundamental two-terminal circuit elements which correlate a particular pair of the four basic circuit variables,i.e.,charge q,voltage v,current i,and magnetic fl ux φ;(b)a complete relational graph of all the possible fundamental two-terminal circuit elements,both linear and nonlinear;it contains of four linear elements,the resistor(R),the capacitor(C),the inductor(L),the transtor(T),and four nonlinear memelements,the memristor(MR),the memcapacitor(MC),the meminductor(ML),and the memtranstor(MT).Symbols for transtor and memtranstor are introduced to facilitate later usage[22].

其中g为几何因子,ε0为真空介电常数,µ0为真空磁导率,εr为相对介电常数,µr为相对磁导率,αd=dP/dH为正磁电耦合系数,αc=µ0dM/dE为逆磁电耦合系数.我们将这种基于磁电耦合效应的线性元件命名为电耦(T),其值表示为或而认为基于非线性i-v关系的忆阻器可以作为电阻所对应的非线性记忆元件(如同忆容器对应于电容、忆感器对应于电感).相应地,我们预言了对应于电耦的第四个非线性记忆元件的存在,并且将这种基于磁电耦合效应的非线性记忆元件命名为忆耦(MT).随着电耦和忆耦的引入,我们建立了一个完整的基本电路变量之间的关系图(图2(b)[22]),其中包括四个线性元件(电阻、电容、电感和电耦)以及四个非线性记忆元件(忆阻器、忆容器、忆感器和忆耦器).

3 基于忆耦器的非易失性存储器

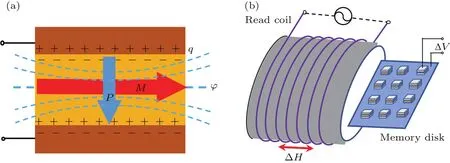

根据忆耦器的定义,可以构建出一种如图3(a)所示的非易失性存储器.该存储器是由一个磁电耦合介质和两个电极组成的简单的三明治结构,其电耦值(T)或者磁电耦合系数(αc或αd)可以有效地存储二进制信息.为了简化存储器的读出和写入操作,我们选择具有面内磁矩和垂直电极化的磁电耦合材料.αc的测量一般需要在磁电耦合材料上施加一个变化的电场(dE),并探测由该电场诱导产生的M变化(dM).然而,这种信息读取方法需要增加磁性隧道结来探测磁矩的改变,所以会使器件的结构变得复杂.这个问题可以通过测量αd来解决.在较低的磁场和电场范围内,磁电耦合效应几乎是线性的,因此αd和αc近似相等,至少具有相同的符号[23].αd的测量相对αc的测量更为简单,可以通过施加一个变化的磁场(dH)来探测该磁场诱导的P的改变(dP).在实际操作中,由于磁电耦合电压系数(αE=dE/dH)正比于αd(αd=dP/dH),因此经常测量材料的αE来代替αd.如图3(b)所示,通过对样品施加一个小的磁场(∆H)并探测诱导出的电压(∆V)的方法来测量αE.这一测量技术已经被广泛应用在复合磁电耦合材料的研究中[24−26],这种测量方法可以让忆耦器的写入和读取操作变得方便和快速.

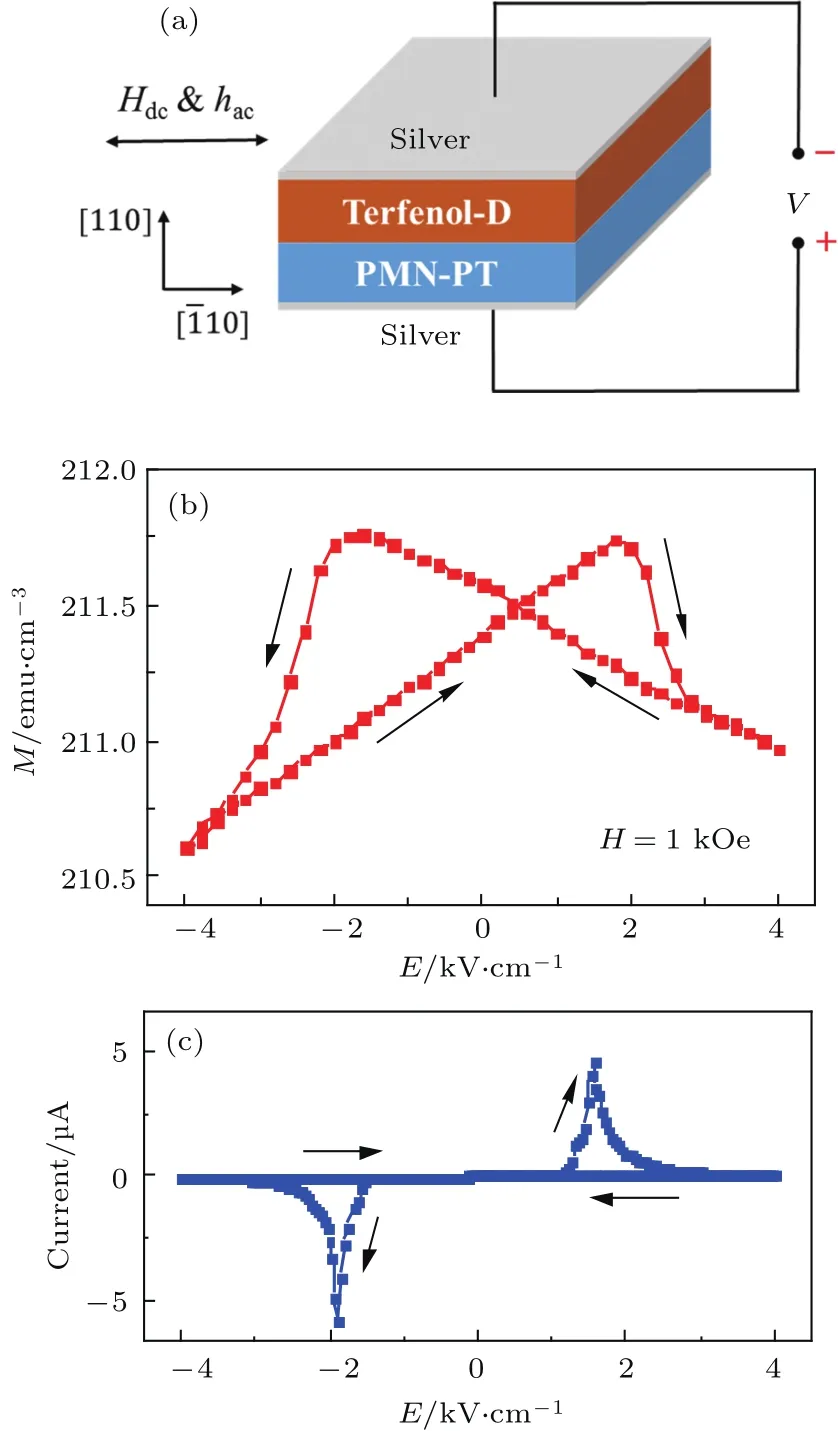

为了验证上述存储原理的可行性,我们制备了[Pb(Mg1/3Nb2/3)]0.7[PbTiO3]0.3(PMN-PT)/Terfenol-D多铁性异质结忆耦器[27].其中,PMNPT是一种常见的铁电材料,具有较大的压电系数.而Terfenol-D是一种具有大的磁致伸缩的材料,该材料是一种由铽(Tb)、镝(Dy)、铁(Fe)三种元素组成的合金,化学式为TbxDy1−xFe2(x∼0.3),磁致伸缩系数超过1000 ppm(1 ppm=10−6),在磁性传感器、换能器以及超声波传感器等领域应用较为广泛.这种多铁性异质结通过界面应力相互耦合,具有较大的磁电耦合系数.图4(a)展示了该器件的结构.电场(E)施加在银电极的两端来翻转PMN-PT的电极化方向,直流磁场(Hdc)施加在异质结的面内方向来改变Terfenol-D的磁矩方向.

图3 基于忆耦器的非易失性存储器的原理图[27] (a)单个存储单元的结构示意图,它是由两个电极和一个忆耦器组成的三明治结构,其中忆耦器具有面内磁矩和面外的电极化;(b)信息读取操作示意图,存储元件的矩阵被置于产生小磁场的读取线圈中,存储的二进制信息可以通过测量磁电耦合系数的方法来读取Fig.3.The principle of the non-volatile memory based on the memtranstor[27]:(a)The schematic structure of a memory element;it consists of a memtranstor medium with in-plane magnetization(M)and out-of-plane electric polarization(P)sandwiched between two electrodes;(b)the illustration of read operation;the array of memory elements is put into a read coil that generates a small magnetic fi eld;the stored binary information is read out by measuring the sign of α.

图4 基于PMN-PT/Terfenol-D忆耦器的存储器件(1 Oe=103/(4π)A/m,1 emu/cm3=103A/m)[27](a)器件的结构和测量参数,电场施加在PMN-PT的[110]方向,直流和交流磁场施加在[¯110]方向;(b)忆耦器的面内磁矩随外加电场的变化,观察到蝴蝶形回滞曲线;(c)忆耦器的I-V曲线,电流的峰值出现在PMN-PT的矫顽场附近(≈±2 kV·cm−1)Fig.4.A memory device made of the PMN-PT/Terfenol-D multiferroic heterostructure[27]:(a)The structure of the device and the measurement con fi guration;the electric fi eld is applied vertically along[110]of PMN-PT and both the dc bias and ac magnetic fi elds are applied in plane along[¯110]of PMNPT;(b)the in-plane magnetization of the device as a function of electric fi eld;a butter fl y-shaped hysteresis is observed;(c)the current-voltage curve of the device;the current peaks re fl ect the reversal of P of PMN-PT at coercive fi elds≈ ±2 kV·cm−1.

图4(b)展示了PMN-PT/Terfenol-D忆耦器的M-E关系.忆耦器在面内方向的磁矩随着施加的垂直方向电场的变化而发生改变,最终ME呈现出蝴蝶形状的回滞曲线.磁矩M的转变点接近±2 kV·cm−1,这与图4(c)中PMN-PT的极化电流峰值的位置相同.这是因为铁电体发生铁电极化翻转时束缚在铁电体两端的电荷会释放出来并积累异号的电荷,从而在电极化翻转过程产生极化电流.因此,极化电流峰的位置附近即对应铁电体的矫顽场.此外,逆磁电耦合系数αc= µ0dM/dE= µ0dM/dεxx·dεxx/dE,其中,εxx为面内方向的应力,dεxx/dE为PMN-PT压电系数的倒数.PMN-PT压电系数的符号与电极化方向有关[28].当电极化P的方向发生翻转后,PMN-PT压电系数的符号发生改变,αc的符号也随之反号.所以磁矩M的转变点与PMN-PT的矫顽场符合.上述实验结果验证了忆耦器作为存储器件的原理:当电极化P翻转后,磁电耦合系数αc跟着发生反号.

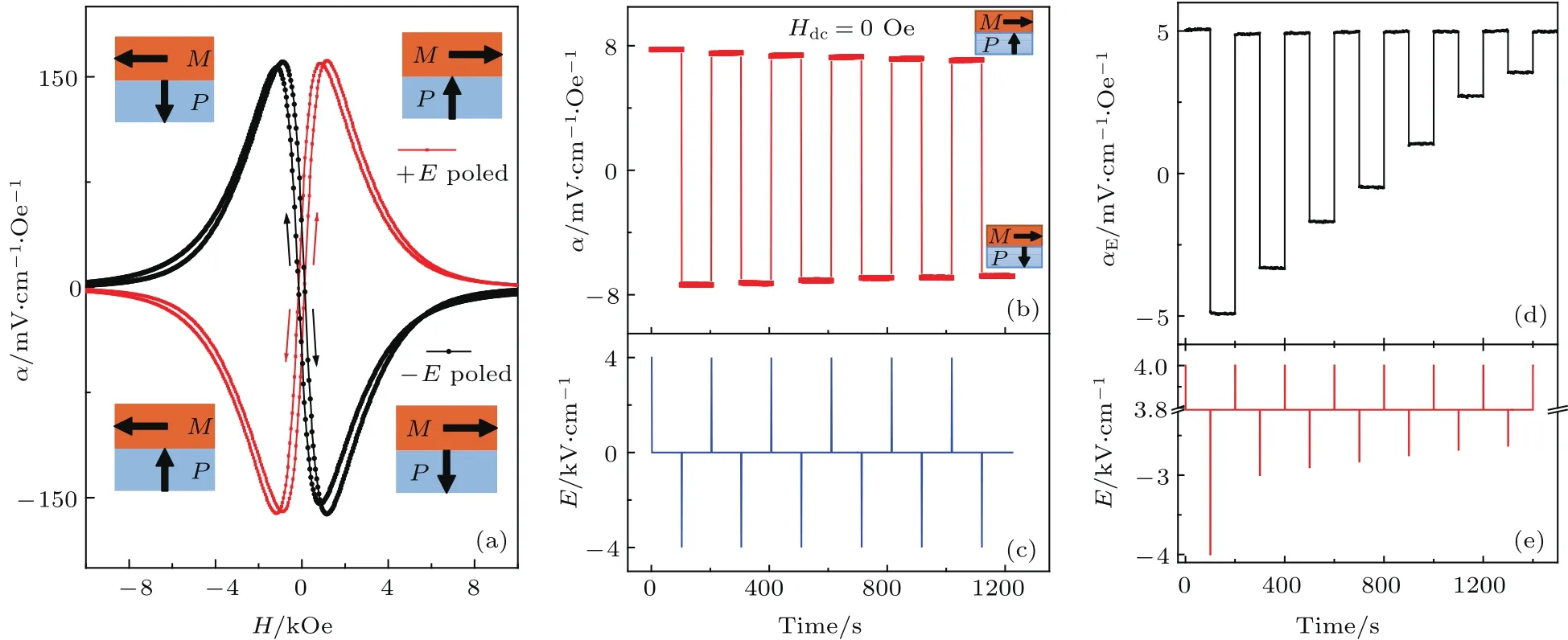

图5(a)展示了忆耦器的磁电耦合电压系数αE随M和P的变化.在测量αE之前,需在忆耦器上施加4 kV·cm−1的电场来设置电极化P的方向.之后,测量αE随面内直流磁场的变化.当P方向向上时(红色曲线),因为在高磁场区域M已经饱和,并且Terfenol-D的磁致伸缩系数接近0,所以αE的数值非常小.当磁场从10 kOe减少到0时,αE逐渐变大,在1 kOe时出现最大值(≈ 160 mV·cm−1·Oe−1), 此时Terfenol-D的磁致伸缩系数也达到峰值.当磁场从正值变化到负值时,αE也由正变为负,并且在−1 kOe时有最小值(≈ −160 mV·cm−1·Oe−1). 当P 方向翻转时(黑色曲线),αE随磁场的变化情况与之前完全相反,αE在正磁场下为负值,在负磁场下为正值.因此,αE的符号依赖于M和P的相对关系:当P的方向固定时,能够通过翻转M的方向来翻转αE的符号;当M的方向固定时,能够通过翻转P的方向来翻转αE的符号.基于第二种情况,忆耦器可以作为一种新型的非易失性存储器.此外,αE随磁场变化的曲线表现出很微弱的回滞现象.因此,当磁场降为0时,αE并不为0,这使得忆耦器在实际应用中更有优势.

变化P的方向能够翻转αE的符号这一现象可通过应力耦合的磁电耦合效应来解释.复合多铁材料的磁电耦合系数可以表示为αd=dP/dH=(dP/dλP)(dλM/dH),其中dλP是铁电层垂直方向应变的变化量,dλM是磁性层受面内小磁场诱导产生的面内方向应变的变化量[24],dλM/dH是磁性层的磁致伸缩系数,dP/dλP是铁电层压电系数的倒数.当P反号时,dP/dλP也会发生反号,而此时dλM/dH保持不变.因此,磁电耦合系数的符号就会翻转.需要指出的是,为了让反转的P不会影响M的方向,忆耦器的磁性层需要足够的厚度.

忆耦器作为记忆元件必须能够重复读取和写入二进制信息.图5(b)展示了忆耦器在没有偏置磁场存在的情况下αE的重复翻转.首先对忆耦器施加+4 kV·cm−1的脉冲电场,测量αE,测量时间100 s;然后再施加−4 kV·cm−1的脉冲电场来翻转P,再测量αE,测量时间100 s;最后多次重复上述过程.由于图5(a)中的微小回滞,αE在0偏置磁场下并没有降为0.尽管直流偏置磁场降为0后,αE的数值随之从∼ 160 mV·cm−1·Oe−1降为∼ 7 mV·cm−1·Oe−1,但是仍然能够清晰地分辨出αE在重复性电场脉冲作用下的连续翻转.

铁电体除了具有传统的上下两种极化状态外还具有多态极化[29].通过调整极化向上和极化向下的铁电畴的比例,可以获得在两个饱和值(+PS和−PS)之间的电极化状态.当M的方向保持不变时,对于不同P的状态,忆耦器的磁电耦合系数αE也具有不同的值.因此,通过使用磁电耦合系数来存储信息,可以实现多态非易失性存储.

图5 (a)忆耦器的磁电耦合系数随施加的直流偏置磁场的变化;(b)在无偏置磁场下忆耦器的α随时间的变化及(c)相应的施加电场随时间的变化;(d)αE的八态转换及(e)相应的施加电场随时间的变化[27,30]Fig.5.(a)The magnetoelectric coefficient α of the memtranstor as a function of dc bias magnetic fi eld;(b) α of the device as a function of time measured without a dc bias magnetic fi eld;(c)the applied electric fi eld as a function of time;(d)eight-level switch of αE;(e)the applied electric fi eld as a function of time[27,30].

可以通过仔细调节电场E的大小来实现αE的多态(2n)非易失性翻转[30].图5(d)和图5(e)展示了αE的八态(23)翻转.首先施加+4 kV·cm−1的电场将αE设定到正的最大值,并将其作为初始状态.向忆耦器施加设定的负电场脉冲来全部或者部分翻转铁电畴从而使αE处于不同的状态.每个电场脉冲施加过后,αE的状态得到了保持,并没有明显的衰减.因此,我们能够在αE的正、负最大值之间选择合适的中间态,从而实现多态非易失存储.需要指出的是,为了确保每次施加负电场脉冲后获得的αE数值相同,在写入不同的状态之前需要施加+4 kV·cm−1的电场脉冲来将忆耦器重置到初始状态.

忆耦器的两态和多态存储原理在P(VDFTrFE)有机铁电薄膜与Metglas所构成的多铁异质结中也得到了验证[31].由于铁电极化翻转电压可以随铁电薄膜厚度的减小而大幅降低,因此,薄膜忆耦器更具有实用性.此外,除复合多铁材料外,基于六角铁氧体的单相多铁材料的忆耦器也被制备出来,并演示了非易失性存储的功能[32].

鉴于磁电耦合材料自身的物理特性,采用忆耦器进行信息存储具有以下几方面的潜在优势.首先是结构简单.存储单元可以采用传统的三明治结构,其包括上、下两个电极与中间的磁电耦合存储介质材料.电场通过电极作用到磁电耦合材料上.其次,从材料选择上来看,目前已发现的磁电耦合材料中,铁磁/铁电复合构成的多铁异质结通常在室温就可以得到较大的磁电耦合系数,特别是在共振频率时,并且多铁异质结的材料选择范围广泛,易与现有的半导体工艺相兼容.再者,写入操作通过在电极两端施加脉冲电压来实现,这与FRAM和RRAM类似.读取过程避免了FRAM中对材料电极化的破坏性读取和MRAM中对M的间接读取,所以忆耦器有利于获得高的读写次数.此外,在功耗方面,由于所采用的材料都为绝缘体材料,依靠电场进行信息的写入,操作过程不涉及电流的引入.因此,存储器的功耗有望大大降低.尽管读取过程涉及到产生一个小的脉冲磁场(∼1 Oe),但是并行读取的方式使得读取大密度存储器的每一个存储单元平均消耗的能量大大降低.

4 基于忆耦器的布尔逻辑运算

随着信息技术的发展,对计算机的信息存储和处理能力都有了更高的要求,而由于半导体工艺已经逼近物理极限,因此在后摩尔时代急需发掘新的信息存储和运算的原理.现代计算机采用运算器和存储器分离的冯·诺依曼架构,这种架构使得运算器与存储器之间的数据传输成为限制系统性能的瓶颈(称为冯·诺依曼瓶颈),大大限制了计算机性能的提高;同时,现代计算机采用的运算器和主存储器(如DRAM)都是易失性器件,不仅在断电后信息不能保存,并且具有较高的能耗.因此,在过去的几十年里,人们为发展逻辑和记忆共存的非冯·诺依曼架构的计算系统付出了巨大的努力,包括阻变存储器、磁性隧道结、相变存储器等各种非易失性存储器都被用来尝试发展非易失的逻辑功能[33−39].忆耦器的多态非易失性存储性能具有发展为非易失性逻辑门的潜力.

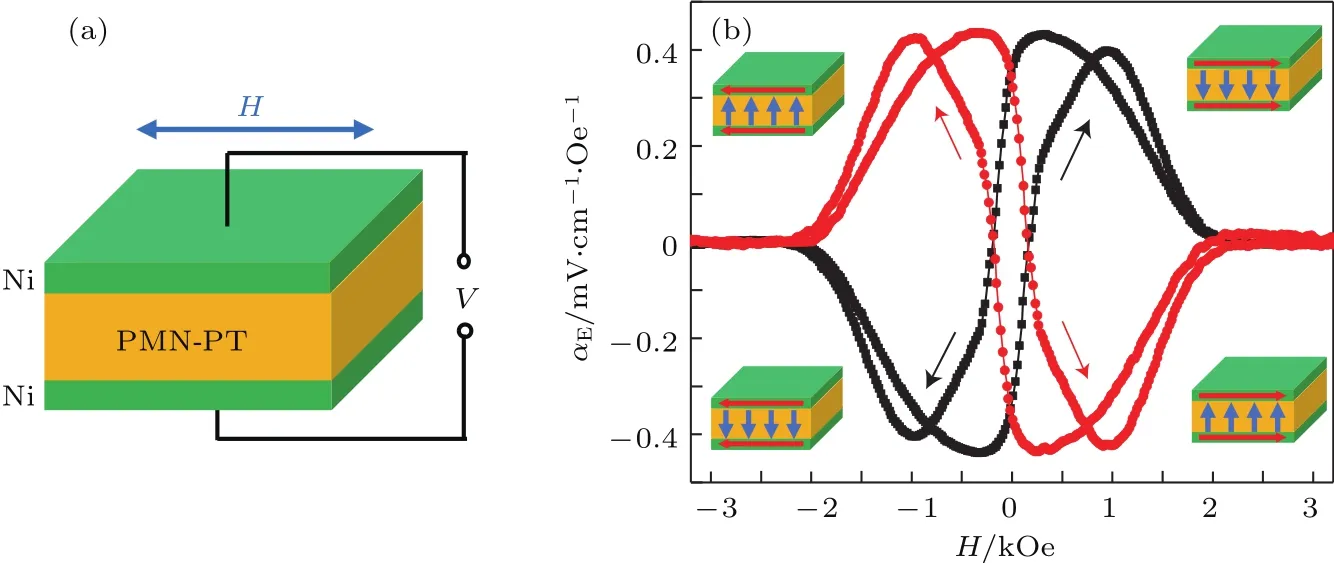

如图6(a)所示,Ni/PMN-PT/Ni忆耦器[40]采用简单金属Ni作为磁性层来替代复杂的Terfenol-D.我们使用磁控溅射的方法在200µm厚的PMNPT单晶上、下两面分别溅射厚度为1µm的金属Ni,从而形成Ni/PMN-PT/Ni这样一个三明治结构.此时,Ni不仅是磁性层,也可以作为忆耦器的电极.图6(b)展示了Ni/PMN-PT/Ni忆耦器的磁电耦合系数随外界直流磁场的变化.在测量αE之前,忆耦器的铁电极化被翻转到同一方向.与PMN-PT/Terfenol-D忆耦器相比,Ni/PMN-PT/Ni忆耦器的αE有更宽的滞后曲线,并且在零磁场下仍有较大的磁电耦合系数.αE在零磁场下的偏置被称为自偏置(self-bias),由于αE∝ αd=dP/dH=(dP/dλP)(dλM/dH),其中dP/dλP是与磁场无关的项,因此αE∝dλM/dH对于磁致伸缩材料λ∝M2,故而αE∝dM2/dH[41].由于Ni与Terfenol-D的磁畴结构不同,Ni具有更宽的M-H回线,导致(dM2/dH)-H曲线的洄滞更大,从而形成更明显的自偏置.在实际应用中,直流磁场的加入会增加器件的复杂性,并且容易对其他器件产生干扰.零磁场下大的磁电耦合系数可以避免直流磁场的存在,因此对于忆耦器的实际应用更为有利.

图7展示了使用单个Ni/PMN-PT/Ni忆耦器来实现或非(NOR)和与非(NAND)逻辑门.NOR是一个具有两路输入的通用布尔逻辑门.当两路同时输入逻辑“0”时,NOR逻辑门会输出“1”,输入除此以外的其他逻辑时,都会输出“0”.逻辑操作被分为三个阶段:首先,初始化忆耦器,使得αE处于正的最大值状态.之后,输入两个电压脉冲X1和X2组成的脉冲序列.输入的电压脉冲的数值高低被分别定义为逻辑“1”和“0”.最后,通过读取磁电耦合系数的方法来读出计算结果.

图6 (a)Ni/PMN-PT/Ni忆耦器的结构与测试示意图;(b)忆耦器的αE随外界直流磁场和电极化方向的变化[40]Fig.6.(a)Schematic of the Ni/PMN-PT/Ni memtranstor structure and the measurement con fi guration;(b)the magnetoelectric voltage coefficient αEas a function of dc magnetic fi eld with the PMN-PT layer pre-poled to+PS and−PS,respectively[40].

图7 基于单个忆耦器的非易失性逻辑门[40] (a)器件的结构和操作示意图;(b)NOR和NAND逻辑的真值表;(c)Ni/PMN-PT/Ni忆耦器的演示NOR逻辑的实验结果;(d)Ni/PMN-PT/Ni忆耦器的演示NOR逻辑的实验结果Fig.7.Nonvolatile NOR logic based on a single memtranstor[40]:(a)The schematic of the device structure and operations;(b)the truth table of NOR operation;(c)experimental results obtained on the Ni/PMN-PT/Ni memtranstor demonstrating the NOR operation;(d)experimental results obtained on the Ni/PMN-PT/Ni memtranstor demonstrating the NAND operation.

如图7(c)所示,忆耦器在初始化后,当输入的X1和X2都为低值(10 V)时,因为没有改变忆耦器的状态,因此输出的磁电耦合电压保持正的高值.当X1和X2中仅有一个为高值(60 V)时,一部分铁电畴翻转,αE从正的高值降为正的低值.当X1和X2都为高值(60 V)时,更多的铁电畴发生翻转,αE成为负值.在此方案中,高的磁电耦合电压被定义为逻辑“1”,低的和负的磁电耦合电压被定义为逻辑“0”.最终,计算结果与NOR的真值表相符(图7(b)).

NAND是另一个具有两路输入的通用布尔逻辑门.当两路同时输入逻辑“1”时,NAND逻辑门会输出“0”,输入除此以外的其他逻辑时,都会输出“1”.图7(d)展示了忆耦器实现NAND逻辑的原理和实验结果.忆耦器在初始化后,两个电压脉冲序列X1和X2被依次输入.低的输入电压(10 V)被设定为逻辑“0”,高的输入电压(58 V)被设定为逻辑“1”.输出的正磁电耦合电压被认定为逻辑“1”,输出的负的磁电耦合电压被认定为逻辑“0”.输入的低电压(10 V)不会影响铁电畴的方向,因此输出的磁电耦合电压会保持正的高值(逻辑“1”).输入一个高电压(58 V)和一个低电压(10 V)会导致部分的铁电畴翻转,但是磁电耦合电压仍然维持正值(逻辑“1”).只有输入的均为高电压(58 V)时,大部分的铁电畴才会翻转,从而导致输出的磁电耦合电压为负值(逻辑“0”).最终,计算结果与NAND的真值表相符(图7(b)).

以上的实验成功地演示了使用单个忆耦器实现非易失性逻辑门NOR和NAND.NOR和NAND是通用逻辑门,其他的逻辑门都可以基于它们来实现.相比于传统的COMS逻辑门,忆耦器的逻辑操作有些不同之处.首先,基于忆耦器的逻辑门是非易失的,能够降低逻辑器件静态能耗.其次,基于忆耦器的逻辑门采用顺序操作而不是COMS中常

用的并行操作.许多基于忆阻器的逻辑器件也采用顺序操作[35,36,38,39,42].尽管顺序操作可能会使得完成一个逻辑操作所消耗的时间更长,但是可以通过减少单个器件所占据的面积来提高整个芯片的处理能力.与忆阻器一样,忆耦器也能够在同一个芯片中同时兼顾记忆和运算,从而大大降低数据从记忆电路传输到逻辑电路所需的时间.值得注意的是,存在其他一些利用磁电耦合效应来实现逻辑功能的方法[43−45],这些逻辑功能常常基于外场控制下的电阻状态的改变.此外,忆耦器是高度绝缘的,因此通过磁电耦合系数来实现逻辑功能有望进一步降低器件能耗.

5 忆耦器模拟人工神经突触可塑性

人类的大脑是一个高效的信息存储与计算系统,而且具有非常低的功耗(约20 W).这主要来自于人脑对信息独特的处理方式.人脑是一个由约1011个神经元和1015个突触构成的高度互连、大规模并行、结构可变的复杂网络.在神经网络中,神经元被认为是大脑的计算引擎,它并行地接受来自与树突相连的数以千计的突触的输入信号.突触可塑性即是通过特定模式的突触活动产生突触权重变化的生物过程,这个过程被认为是大脑学习和记忆的源头[46].可以看出,人脑是一种典型的非冯·诺依曼构架,即存储与计算于一体的并行信息处理模式,并且还具有自适应学习能力、高的容错能力和抗干扰能力.随着计算数据复杂度的提高,神经网络型信息处理模式的效率将会明显优于传统计算机[47].为了实现这种神经形态信息存储与计算特性,人们已经尝试采用传统硅基器件和电路来模拟神经形态存储与计算功能[48].由于模拟单个神经元功能所需要的器件多、电路复杂,在大规模集成方面仍然面临着高密度和低能耗的挑战.近年来,忆阻器在模拟人类大脑神经突触的功能方面展现了巨大潜力[49−51].随着忆阻器的出现,利用单一电子器件实现神经突触可塑性和计算功能的模拟引起了人们的极大兴趣,形成了一个新的前沿研究方向——突触电子学(Synaptic Electronics)[52].

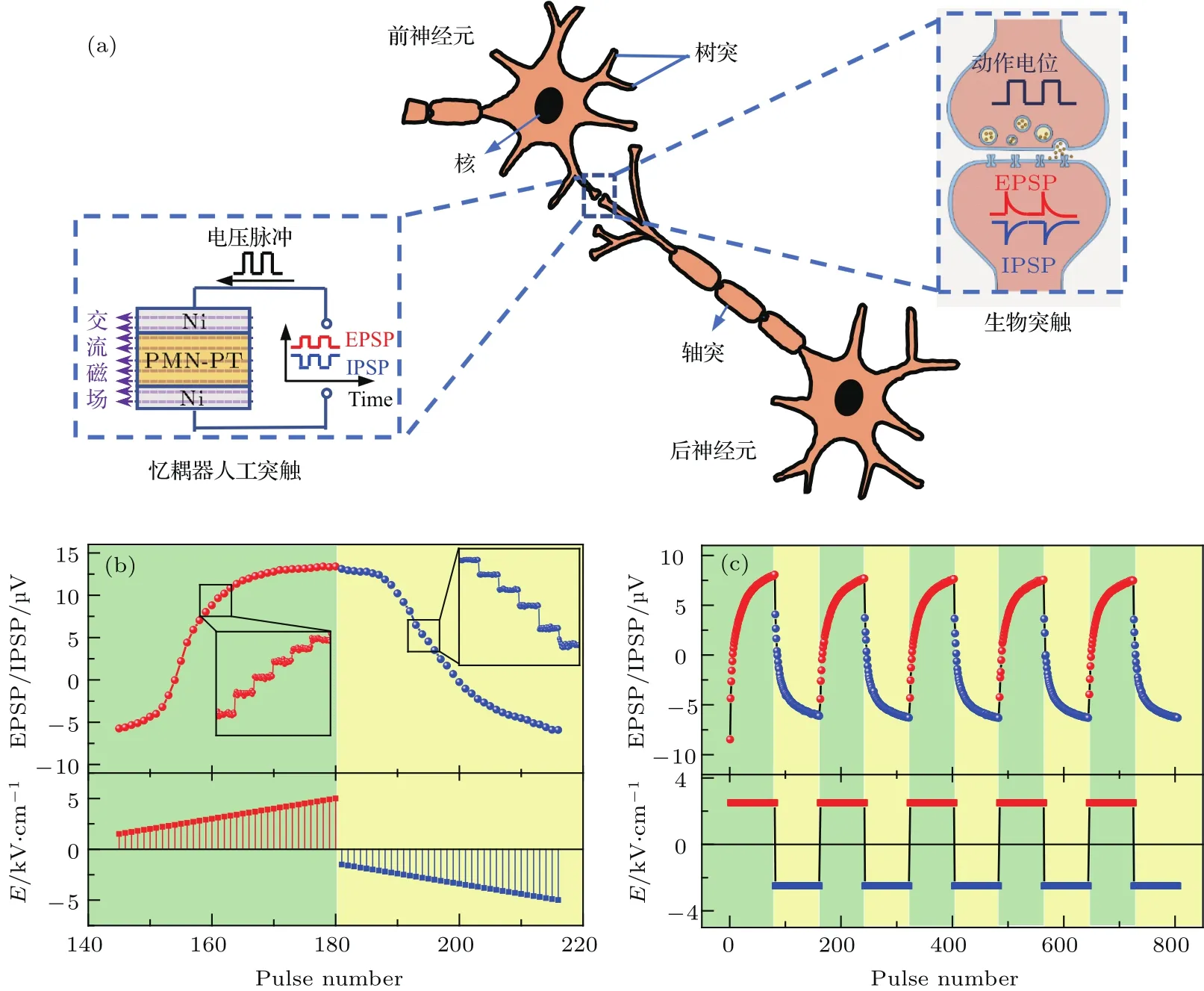

忆耦器与忆阻器具有相似的功能,可用于突触可塑性的模拟[53].图8(b)显示了在电压脉冲作用下,Ni/PMN-PT/Ni磁电耦合电压VME的变化.可见,随着脉冲电压的升高,VME从负值(−5µV)逐渐增加至正值(13µV).在反向电压脉冲的作用下,VME逐渐降低至−5µV.所得到的每一个VME值都具有很好的稳定性和保持性(见图8(b)内插图).在合适的脉冲电压条件下,VME的变化还可以通过只改变脉冲数目实现(见图8(c)).这种VME的连续可逆变化与生物学中突触的信息传递行为非常相似.在生物学中,突触是连接前神经元和后神经元的部位(见图8(a)).在外界刺激下,前神经元产生动作电位并经过突触传递至后神经元,并产生兴奋性后神经元电位(EPSP)或抑制性后神经元电位(IPSP),同时突触的权重(即连接强度)发生变化.信息的记忆和学习就是突触权重变化的结果.我们可以把忆耦器作为一个人工突触器件,其中电耦值相当于突触权重,所产生的VME相当于EPSP或IPSP.外加电压脉冲起到了动作电位的作用.因此,VME的增加和减小分别对应于突触权重的增强和抑制,即突触的可塑性.

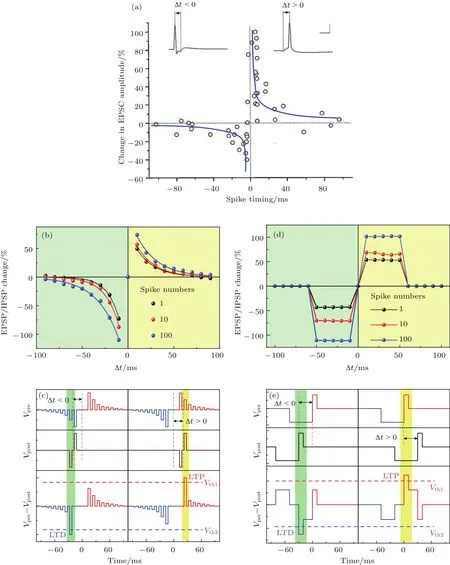

神经生物学研究表明,神经突触的学习功能取决于连接突触前后神经元的激发相对时间,当前、后神经元激发相差时间小时,权重变化较大.随着相差时间的延长,权重变化逐渐减弱(见图9(a)).这种行为称为脉冲时间依赖可塑性行为(spikingtime-dependent plasticity,STDP)[46].为了模拟突触的STDP行为,我们设计了两个Ni/PMN-PT/Ni忆耦器的脉冲电压触发序列,分别对应于突触的前、后激发脉冲(见图9(c)).前激发脉冲序列包含7个抑制(负电压)脉冲(脉冲宽度为10 ms,脉冲电压从−1 V逐渐变化到−25 V)和7个增强(正电压)脉冲(脉冲宽度为10 ms,脉冲电压从25 V逐渐变化到1 V),脉冲间隔为10 ms.后激发脉冲序列包含两个脉冲宽度为10 ms、脉冲间隔10 ms的脉冲,脉冲电压分别为25 V和−25 V.前、后两个脉冲序列在不同时间下的叠加结果反映了作用在忆耦器上的有效电压大小.例如,当前激发脉冲序列比后激发脉冲序列提前20 ms时(∆t=20 ms),后激发脉冲序列的正电压部分与前激发脉冲序列的第二个增强脉冲叠加,叠加后的脉冲电压超过增强阈值电压(Vth1)使得忆耦器突触的权重增强.而当前激发脉冲序列比后激发脉冲序列落后20 ms时(∆t=−20 ms),后激发脉冲序列的负电压部分与前激发脉冲序列的第二个抑制脉冲叠加,叠加后的脉冲电压超过抑制阈值电压(Vth2)使得忆耦器突触的权重减弱.忆耦器突触权重的变化大小可以通过调节前、后激发脉冲序列的相对时间∆t以及作用的脉冲数目来调节.通过改变∆t的值(从−90 ms至90 ms),突触STDP学习行为可以在忆耦器中模拟出来(见图9(b)).由于忆耦器的VME值在脉冲电压不变的情况下可以通过改变触发脉冲数目实现,因此可以对前激发脉冲序列进行简化.如图9(e)所示,采用两个极性相反但宽度不同的脉冲(分别为60 ms和10 ms)构成前激发脉冲序列.此时,由于前、后激发脉冲序列中的脉冲电压均为常数,相叠加后也为常数.因此,突触权重的变化只取决于作用的脉冲个数与∆t的正负(见图9(d)).

图8 (a)生物神经元和突触示意图,右插图为信息的传递通过作用电势释放神经递质,引发激发后突触电势(EPSP)和抑制后突触电势(IPSP)来完成,左插图为外加电压脉冲改变忆耦器中的极化状态,随即改变忆耦器磁电耦合状态,使得磁电耦合电压(VME)改变,VME起到EPSP/IPSP的作用;(b)EPSP/IPSP(即VME)在变电场脉冲序列(脉冲宽度10 ms,间隔100 s)作用下的变化;(c)EPSP/IPSP(即VME)在恒电场(2.5 kV/cm)脉冲序列(脉冲宽度10 ms,间隔100 s)作用下的变化[53]Fig.8.(a)Schematic illustration of biological neurons and synapses.Right inset:the information transmission between neurons occurs via propagation of action potentials through the axon and release of neurotransmitters,which causes excitatory postsynaptic potentials(EPSP)and inhibitory postsynaptic potentials(IPSP)that would in turn propagate in the postsynaptic axon.Left inset:the memtranstor-based synapse transmits information by applying voltage pulses to change the polarization and subsequently change the magnetoelectric coupling to produce the VMEvariation.The VMEplays a role of either EPSP(increase of VME)or IPSP(decrease of VME)in the postsynaptic axon.(b)The evolution of the EPSP/IPSP(i.e.,VME)by applying trains of voltage pulses(bottom part)with a fi xed time width of 10 ms spaced 100 s apart and increasing amplitude.The VMEwas measured at the pulse spacing.Insets in(b)present enlarged views of each obtained EPSP/IPSP that shows good stability and can last for a certain period of time(100 s for each step).(c)The evolution of the EPSP/IPSP(i.e.,VME)by applying voltage pulses with 10 ms width and a constant amplitude of E=2.5 kV·cm−1[53].

利用这种简化的STDP学习行为,我们构建了一个忆耦器阵列来模拟神经网络的学习行为.这个神经网络有16个前神经元和1个后神经元.16个前神经元通过16个突触与后神经元连接,每一个突触权重对应于一个4×4图像的像素点.我们采用了一种随机噪声学习方法,将图像和噪声交替地用于神经网络学习,图像和噪声的出现概率各占50%.其中噪声由两个随机出现的像素点构成(见图10(a)).在学习过程中,我们设定对应于图像的前神经元将激发一个前脉冲至后神经元,并在间隔∆t时间后(∆t<50 ms),后神经元对所有的前神经元激发一个后脉冲.这时,后脉冲与前脉冲产生叠加,使对应于图像的突触得到增强.而其他非对应图像的突触由于没有叠加产生而不发生变化.前神经元在上一个前脉冲结束后立即激发另一个对应于噪声图像的前脉冲,其与上一个后脉冲相叠加,使得对应于噪声的突触权重得到抑制.以上两个前脉冲和一个后脉冲的激发,称为一个学习过程(见图10(b)).图10(c)显示了对三种图像依次进行学习的结果.在初始条件下,突触权重被随机赋值.在对图像1进行300次学习后,突触权重分布与所学习的图像基本符合.此后依次对图像2和图像3进行学习,在300次学习后,突触权重分布分别对应于图像2和图像3的形状.如图10(d)所示,学习准确率可以达到91.3%.随着噪声图像点的增加,学习下降为86.9%,表明忆耦器神经网络的学习效率对于不可控噪声输入具有一定的抵抗能力.

图9 (a)海马神经元在重复相关激发下的后突触电流变化;(b)表现出经典STDP特性的实验数据与(c)对应的脉冲序列;(d)表现出简化STDP特性的实验数据与(e)对应的脉冲序列;Vth1和Vth2分别为可以诱发突触增强和抑制的阈值电压[46,53]Fig.9.(a)The measured change in excitatory postsynaptic current(EPSC)of rat hippocampal neurons after repetitive correlated spiking;(b)the experimental data showing the conventional STDP characteristic and(c)the corresponding voltage pulse scheme;(d)the experimental data following a simpli fi ed STDP characteristic and(e)the corresponding voltage pulse scheme.Vth1and Vth2are the threshold voltage that can induce potentiation and depression of synapses,respectively.By superimposing pre-and post-spike potentials,the overall potential on the synapse will be above the Vth1/Vth2,resulting in the change of the synaptic weight[46,53].

图10 (a)神经网络模拟示意图,前神经元层中16个神经元分别通过16个突触权重为wi的忆耦器突触与后神经元相连,三种形状的图片和一张随机噪声图片用来学习;(b)一次学习过程,其包括一次图片学习和一次噪声学习,图片学习产生长程增强(LTP),噪声学习产生长程抑制(LTD);(c)忆耦器突触权重分布随学习次数的变化;(d)忆耦器网络学习的准确度随噪声图片中噪声像素点数的变化[53]Fig.10.(a)Schematic illustration of the simulated neuromorphic network.The pre-neuron layer with 16 neurons is fully connected to one post-neuron through 16 memtranstor synapses with synaptic weight wi.Three patterns and one random noise image are used for learning.The pre-neuron layer derives pre-spikes in response to the presentation of pattern or noise.(b)Schematic illustration of the pulse scheme in one epoch where one pattern and then one noise are presented.Long-term potentiation(LTP)and long-term depression(LTD)that occurs in the case of pattern and noise presentation,through the simpli fi ed STDP learning.(c)Evolution of the synaptic weight map during learning.Initial synaptic weights are set randomly.(d)The saturation value of the learning accuracy as a function of the pixel number in noise.The red circles represent the average value from 1000 to 2000 epochs where the accuracy values reach the saturation level.The blue and the green dashed lines indicate the maximum and minimum values obtained in the simulations,respectively,and the other results lie within the shaded cyan area[53].

6 总结与展望

信息技术的高速发展需要开发高性能存储器与之相适应,而寻找材料中新的物理状态作为信息存储媒介是开发新型存储器件的物理基础.具有磁电耦合效应的多铁性材料为信息存储提供了更多的自由度,其磁电耦合系数作为磁电耦合材料中的重要参量,体现了材料磁化和电极化的综合性能,具备非易失存储的物理状态特征.本文介绍了一种基于磁电耦合效应的基本电路元器件——忆耦器的提出以及以磁电耦合系数为存储状态的非易性存储器件的工作原理.忆耦器的多态非易性存储不仅可以使忆耦器实现逻辑运算功能,而且可以模拟神经突触的可塑性.利用忆耦器的这些特点,可以将存储和计算在同一忆耦器中实现,有望开发具有非冯·诺依曼结构的神经形态计算系统.针对忆耦器在实际中的大规模应用,未来需要进一步提高磁电耦合系数,并不断优化忆耦器的尺寸和结构设计.例如,制备高质量的铁电薄膜来组成忆耦器的三明治结构,以减小器件尺寸、降低操作电压、减轻衬底的夹持效应等.这些研究结果进一步证明了忆耦器理论模型的正确性,为忆耦器在真实电路中的应用提供了可能,同时,也从基本电路元件的角度重新看待研究已久的磁电耦合效应,为磁电耦合效应的应用开辟了新的途径.

[1]Scott J F 2000 Ferroelectric Memories(Berlin:Springer-Verlag)pp23–51

[2]Chappert C,Fert A,van Dau F N 2007 Nat.Mater.6 813

[3]Wuttig M,Yamada N 2007 Nat.Mater.6 824

[4]Waser R,Dittmann R,Staikov G,Szot K 2007 Nat.Mater.6 833

[5]Dong S,Liu J M,Cheong S W,Ren Z 2015 Adv.Phys.64 519

[6]Scott J F 2007 Nat.Mater.6 256

[7]Gajek M,Bibes M,Fusil S,Bouzehouane K,Fontcuberta J,Barthélémy A,Fert A 2007 Nat.Mater.6 296

[8]Garcia V,Bibes M,Bocher L,Valencia S,Kronast F,Crassous A,Moya X,Enouz-Vedrenne S,Gloter A,Imho ffD,Deranlot C,Mathur N D,Fusil S,Bouzehouane K,Barthélémy A 2010 Science 327 1106

[9]Pantel D,Goetze S,Hesse D,Alexe M 2012 Nat.Mater.11 289

[10]Bibes M,Barthélémy A 2008 Nat.Mater.7 425

[11]Song C,Cui B,Li F,Zhou X J,Pan F 2017 Prog.Mater.Sci.87 33

[12]Thiele C,Dorr K,Bilani O,Rödel J,Schultz L 2007 Phys.Rev.B 75 054408

[13]Ma J,Lin Y,Nan C W 2010 J.Phys.D:Appl.Phys.43 012001

[14]Chen Y,Gao J,Fitchorov T,Cai Z,Ziemer K S,Vittoria C,Harris V G 2009 Appl.Phys.Lett.94 082504

[15]Xuan H C,Wang L Y,Zheng Y X,Li Y L,Cao Q Q,Chen S Y,Wang D H,Huang Z G,Du Y W 2011 Appl.Phys.Lett.99 032509

[16]Chua L O 1971 IEEE Trans.Circuit Theory 18 507

[17]Chua L O,Kang S M 1976 Proc.IEEE 64 209

[18]Strukov D B,Snider G S,Stewart D R,Williams R S 2008 Nature 453 80

[19]Di Ventra M,Pershin Y V,Chua L O 2009 Proc.IEEE 97 1717

[20]Vongehr S 2012 Adv.Sci.Lett.17 285

[21]Mathur N D 2008 Nature 455 E13

[22]Shang D S,Chai Y S,Cao Z X,Lu J,Sun Y 2015 Chin.Phys.B 24 068402

[23]Lou J,Pellegrini G N,Liu M,Mathur N D,Sun N X 2012 Appl.Phys.Lett.100 102907

[24]Fiebig M 2005 J.Phys.D 38 R123

[25]Eerenstein W,Mathur N D,Scott J F 2006 Nature 442 759

[26]Nan C W,Bichurin M I,Peterburgskaya B S,Dong S X,Viehland D,Srinivasan G 2008 J.Appl.Phys.103 031101

[27]Shen J X,Cong J Z,Chai Y S,Shang D S,Shen S P,Zhai K,Tian Y,Sun Y 2016 Phys.Rev.Appl.6 021001[28]Park S E,Shrout T R 1997 J.Appl.Phys.82 1804

[29]Lee D,Yang M S,Kim T H,Jeon B C,Kim Y S,Yoon J G,Lee H N,Baek S H,Eom C B,Noh T W 2012 Adv.Mater.24 402

[30]Shen J X,Cong J Z,Shang D S,Chai Y S,Shen S P,Zhai K,Sun Y 2016 Sci.Rep.6 34473

[31]Lu P P,Shang D S,Shen J X,Chai Y S,Yang C S,Zhai K,Cong J Z,Shen S P,Sun Y 2016 Appl.Phys.Lett.109 252902

[32]Zhai K,Shang D S,Chai Y S,Li G,Cai J W,Shen B G,Sun Y 2018 Adv.Func.Mater.28 1705771

[33]Wang J,Meng H,Wang J P 2005 J.Appl.Phys.97 10D509

[34]Khajetoorians A A,Wiebe J,Chilian B,Wiesendanger R 2011 Science 332 1062

[35]Borghetti J,Snider G S,Kuekes P J,Yang J J,Stewart D R,Williams R S 2010 Nature 464 873

[36]Wang Z,Zhao W,Kang W,Zhang Y,Klein J O,Ravelosona D,Zhang Y,Chappert C 2014 IEEE Trans.Magn.50 9100604

[37]Li Y,Zhong Y P,Deng Y F,Zhou Y X,Xu L,Miao X S 2013 J.Appl.Phys.114 234503

[38]Linn E,Rosezin R,Tappertzhofen S,Böttger U,Waser R 2012 Nanotechnology 23 305205

[39]Siemon A,Breuer T,Aslam N,Ferch S,Kim W,van den Hurk J,Rana V,Ho ff mann-Eifert S,Waser R,Menzel S,Linn E 2015 Adv.Funct.Mater.25 6414

[40]Shen J X,Shang D S,Chai Y S,Wang Y,Cong J Z,Shen S P,Yan L Q,Wang W H,Sun Y 2016 Phys.Rev.Appl.6 064028

[41]Zhou Y,Yang S C,Apo D J,Maurya D,Priya S 2012 Appl.Phys.Lett.101 232905

[42]Cassinerio M,Ciocchini N,Ielmini D 2013 Adv.Mater.25 5975

[43]Binek C,Doudin B 2005 J.Phys.Condens.Matter.17 L39

[44]Chen X,Hochstrat A,Borisov P,Kleemann W 2006 Appl.Phys.Lett.89 202508

[45]Hu J M,Li Z,Lin Y H,Nan C W 2010 Phys.Status Solidi RRL 4 106

[46]Bi G Q,Poo M M 1998 J.Neurosci.18 10464

[47]Mead C 1990 Proc.IEEE 78 1629

[48]Indiveri G,Chicca E,Douglas R A 2006 IEEE Trans.Neural Netw.17 211

[49]Yang J J,Strukov D B,Stewart D 2013 Nat.Nanotechnol.8 13

[50]Jo S H,Chang T,Ebong I,Bhadviya B B,Mazumder P,Lu W 2010 Nano Lett.10 1297

[51]Yang C S,Shang D S,Liu N,Shi G,Shen X,Yu R C,Li Y Q,Sun Y 2017 Adv.Mater.29 1700906

[52]Kuzum D,Yu S,Wong H S P 2013 Nanotechnology 24 382001

[53]Shen J X,Shang D S,Chai Y S,Wang S G,Shen B G,Sun Y 2018 Adv.Mater.30 1706717