一种4 M-Pixel/s 4通道X射线CCD读出电路

余 茜,王克柔,易 婷,陆 波,陈 勇,洪志良

(1.复旦大学 专用集成电路与系统国家重点实验室,上海 201203; 2.中科院高能物理研究所,北京 100049)

提高CCD传感器的读出速率而又不会降低其噪声性能的一个方法是: 增加CCD阵列的读出节点,实现多通道并行读出处理.采用分立器件实现的CCD读出电路需要大面积的片上无源电容与电阻,在多通道应用下,需要消耗较大芯片面积和功耗.因此高读出速度、多通道的CCD读出电路需要采用专用集成电路芯片(Application Specific Integrated Circuit, ASIC)实现.

文献[1]中设计了一个单通道X射线CCD ASIC,这款芯片基于增量型ΣΔ ADC(Incremental ΣΔ ADC, I-ΣΔ ADC)实现.与奈奎斯特ADC类似,增量型ΣΔ ADC的数字输出码字与模拟输入信号直接存在一一对应关系[2],适合于采样不连续的CCD信号.而增量型ΣΔ ADC有着噪声整形和过采样的优点,相较于普通奈奎斯特ADC,更容易实现较高精度.由于ΣΔ ADC的噪声滤波可以在数字域完成,因此可以移除独立的模拟CDS模块,将CDS操作完全放到ΣΔ ADC中完成,这样减小了芯片面积.本论文的设计针对一款有着4个读出节点的CCD传感器的输出信号处理,旨在采用离散时间增量型ΣΔ调制技术,实现高读出速率、低读出噪声的X射线CCD读出系统.

1 CCD读出系统

1.1 CCD读出系统结构

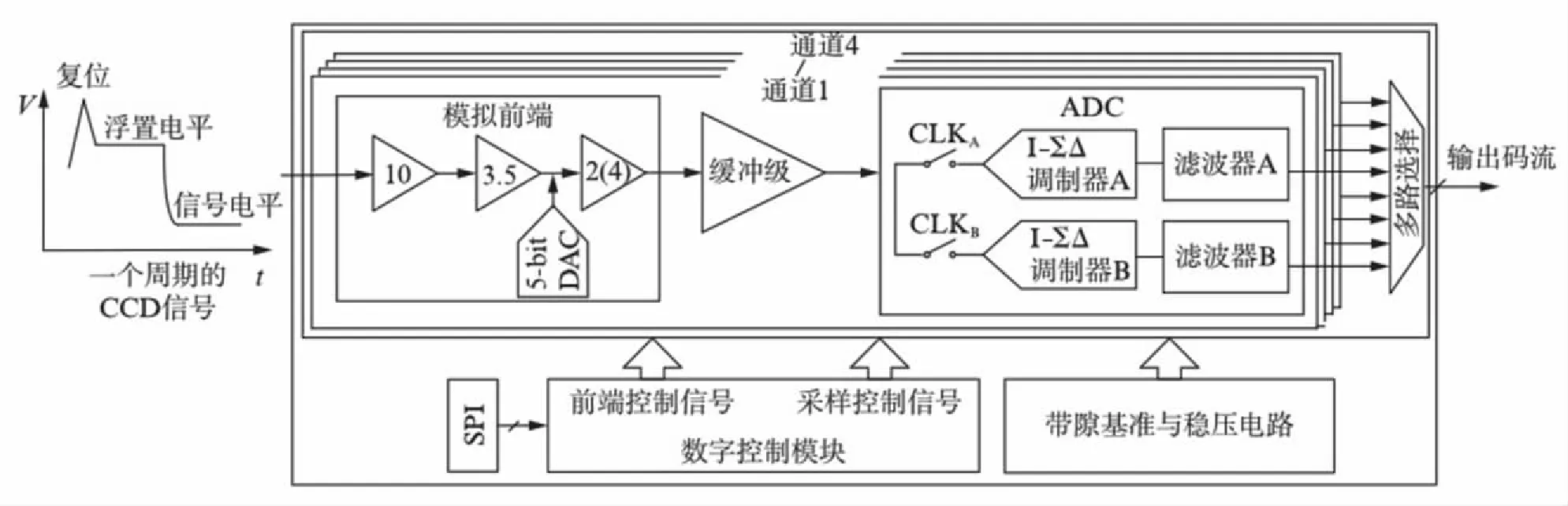

4通道CCD信号读出系统框图如图1(看第244页)所示,系统由4个通道组成,每个通道均包含了1个低噪声模拟前端和驱动级电路、2个增量型ΣΔ调制器以及2个降采样滤波器.这4个通道并行工作,由CCD提供的复位信号进行同步.

一个周期的CCD输出信号包含复位、浮置电平以及信号电平3个部分,CCD读出系统需要量化出浮置电平与信号电平的电压差.CCD输出信号幅值很小,要由前端放大器将其放大,以便充分利用后级ADC的动态范围[3].CCD信号中的直流分量较大,前端放大器通过电容耦合将其去除.在本设计中前端放大器可实现70倍与140倍2档可调增益,这个增益通过3个运放级联实现.第1级运放为10倍固定增益,第2级运放为3.5倍固定增益,第3级运放有2倍与4倍增益2种选择.模拟前端中使用了1个5-bit数模转换器(Digital to Analog Converter, DAC),可进一步调整CCD信号的动态范围[4].

放大后的CCD信号经驱动级送入增量型ΣΔ调制器,在调制器中转换为数字码流.每个通道有A和B 2个3阶3位增量型调制器,这2个调制器交替采样CCD信号.调制器的转换精度与一个转换周期的采样次数相关,一个转换周期所需的采样次数依据MATLAB SIMULINK行为级仿真决定.将4个通道的A和B调制器分别编为2组,同组的4个调制器使用相同的时钟控制信号.调制器产生的数字码流经由特殊定制的数字滤波器进行降采样和滤波,每个调制器的数据都有一个独立的降采样滤波器进行处理.经过一个多路选择开关,8个ADC的模数转换结果依次串行输出.

ADC需要的参考电压和偏置电流均由片上的带隙基准源及稳压电路产生.整个读出系统需要的控制信号全部由数字控制模块提供,此外,串行外设接口(Serial Peripheral Interface, SPI)根据不同的应用与测试环境提供了诸多可配置的模式.

图1 CCD读出系统框图Fig.1 Architecture of the CCD readout system

1.2 增量型调制器拓扑结构

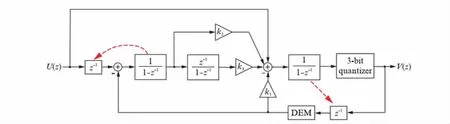

本设计中调制器选择了具有高线性度的前馈结构.多位量化器的使用进一步降低了对各级积分器线性度的要求,但是多位反馈DAC的非线性直接限制了整个ADC的精度,需要采用动态元件匹配(Dynamic Element Match, DEM)技术来减少反馈DAC的非线性.前馈结构中,需要1个加法器来对所有的前馈通路求和.无源加法器使用电容阵列求和,不需要额外的运放,但是寄生电容和量化器的回踢噪声会降低求和结果的精度.而有源加法器的求和精度更高,但是需要使用一个运放,经权衡采用有源加法器.多条前馈通路使得这个运放的反馈系数较小,加法器中的运放应具有高的单位增益带宽才能满足速度要求.

关于RFCA的最佳麻醉方法目前尚未确定[7]。世界范围内各中心手术所采用的麻醉方案并不一致,甚至同一中心也可能采用不同的麻醉方案。对于镇静和全身麻醉方案下RFCA的利弊,虽有各方学者对其进行比较和研究,但仍存在一些问题:大部分相关研究均来自单中心,研究结果的可靠性受到一定限制;麻醉方案对手术并发症的影响鲜有报道;消融术后Af复发率的问题,各学者的研究结果也存在一定差异[4-6]。

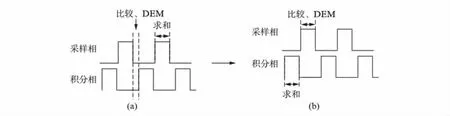

离散时间ΣΔ ADC工作由采样相和积分相两相非交叠时钟控制.在传统前馈结构中,为了给加法器足够的建立时间,分配了位于采样相的半个时钟周期的时间用于加法器求和,如图2(a)所示.而反馈DAC的输入又必须在积分相开始前建立,因而比较和DEM操作只能在积分相和采样相的非交叠时间完成,加法器求和得到保证.

图2 (a)传统前馈结构的时序图和(b)SLD结构时序图Fig.2 (a) Timing schematic of conditional feed-forward architecture and (b) timing schematic of SLD architecture

采用传统前馈结构,由于比较与DEM操作需要占用额外时间,这使得调制器中积分器、量化器、DEM逻辑单元的速度要求更加苛刻.为了缓解时序的紧张,在反馈路径上引入了额外环路延时[5].如图3所示,最后一级积分器的单位延时移到反馈通路上,因此比较与DEM操作可以在这个单位延时中完成.环路延时迁移(Shifted Loop Delay, SLD)结构的时序如图2(b)所示,比较与DEM操作从非交叠时间移到了采样相,因而非交叠时间可以减少,从而避免了较多的非交叠时间给调制器各模块带来的速度挑战.SLD结构中,最后一级积分器在积分的同时完成求和操作,节省了1个有源加法器.

在图3可以看到,第1级积分器的延时也被移到输入信号通路上.输入信号U经由前馈支路、最后一级积分器、量化器、DEM,然后反馈到第1级积分器输入时,与输入信号通路上同样有一个单位延时的输入信号U相减,这样使得环路滤波器的净输入只有量化噪声,从而保留了前馈结构高线性度优点.

图3 3阶3位SLD调制器框图Fig.3 Third-order three-bit SLD modulator architecture

为了避免SLD造成的不稳定,增加了一条从比较器输出到最后一级积分器输入的反馈支路,这条反馈支路的系数为k1.图3中3阶SLD结构调制器的信号传输函数(System Transfer Function, STF):

(1)

其中:

(2)

要保留前馈结构的低失真的特性,需要使得信号传输函数STF=1,代入式(1)得到:

k1=1.

(3)

式(3)表明: 增加的这条反馈支路的系数应常为1.在积分器中,运放是一个含有反馈网络的闭环系统.假设这是一个单极点运放,要实现ω0的闭环3dB带宽,则运放的增益带宽积(Gain-Bandwidth Product, GBW):

(4)

其中β为反馈系数.式(4)表明,ω0一定时,反馈系数β越大,所需要的GBW越小.在噪声传输函数相同的前提下,SLD结构求和运放的反馈系数大于传统前馈结构求和运放的反馈系数.因而,虽然SLD结构在最后一级级联了需要更长稳定时间的无延时积分器[6],它对求和运放GBW的要求可以比传统前馈结构低.

2 电路设计

2.1 模拟前端

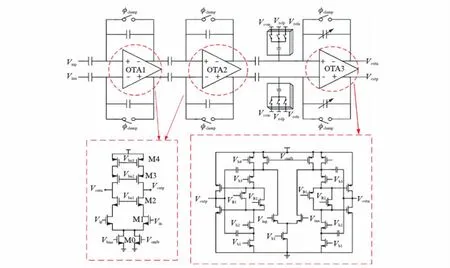

CCD读出系统的前端电路实现如图4所示,前端放大器通过3个运算放大器(Operational Trans-conductance Amplifier, OTA)级联实现.这3个放大器采用电容反馈,通过钳位(clamp)开关为运放的高阻输入点提供直流偏置.

图4 模拟前端结构框图及电路图Fig.4 Analog front-end architecture and schematic

套筒式运放能提供足够大的直流增益,结构简单而功耗相对较小,因而前两级运放采用了套筒式结构,如图4所示.套筒式运放能实现的最大输出摆幅为:

ΔV=VDD-Vdstat0-Vdstat1-Vdstat2-Vdstat3-Vdstat4,

(5)

其中:VDD为电源电压;Vdsat0~Vdsat4分别为M0~M4管的过驱动电压.式(5)表明套筒式运放的输出摆幅较小,因此需要大输出摆幅的第3级运放采用了两级电压放大结构,如图4所示.该两级运放的第1级为折叠共源共栅结构,采用高直流增益的NMOS作为输入对管;第2级为大输出摆幅的AB类结构.AB类输出级采用跨导线性环(Trans-linear Loop)偏置,它的静态电流较小,但可以提供较大的动态电流驱动容性负载.

2.2 数字滤波器

本设计中的数字滤波器工作在64MHz时钟频率下,为了获得较小的面积,本文提出了一种特殊定制的滤波器结构.该降采样滤波器的系数hn应满足:

(6)

其中:Vm为信号电平与浮置电平的差Vin的实测值;Vful为转换器满量程输入;xn为调制器一个转换周期的输出码流,一个转换周期有100次采样,因而1≤n≤100.在Matlab行为级仿真中,改变Vin的大小,得到对应的输出码流xk,i(1≤k≤N,1≤i≤100),每一组输出码流xk,i与输入电压测量值Vm,k的关系都应满足式(6).通过N次仿真,可得到N组关于滤波器系数的方程:

(7)

通过多元线性回归分析可得到滤波器系数hn(1≤n≤100),受硬件条件限制,滤波器的系数只能用有限的字长表示.Matlab仿真表明,13-bit量化字长可使滤波器以较小的硬件开销实现系统所需的滤波性能.依据实际输出码流的特点及滤波器系数大小,通过仿真可以得出滤波器的输出字长为21bits.

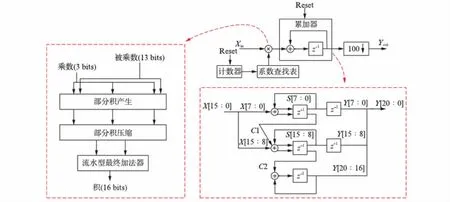

滤波器的结构如图5所示.每个转换周期开始时,计数器和累加器被Reset信号复位.复位结束后,计数器、累加器重新开始工作,查找表依据计数器的值给出对应的滤波器系数.数字输入Xin乘以相应滤波器系数后,在累加器中进行累加.在该转换周期结束时,滤波器输出此时的累加结果,得到输出码字Yout.

滤波器数字输入Xin的字长为3bits,滤波器系数的字长为13bits,因此滤波器中的乘法器要完成13-bit被乘数与3-bit乘数的乘法.为了满足速度要求,乘法器采用流水线结构,如图5所示.乘法操作被分解为4级: 第1级产生3个部分积,第2级将部分积深度压缩为2,第3级与第4级构成流水线加法器以完成最终相加.

图5 降采样滤波器结构Fig.5 Decimation filter architecture

图6 芯片版图Fig.6 The chip layout

为了在15.625ns内完成最高21bits的累加,累加器同样使用流水型加法器,如图5所示.累加器输入X与累加器前一时刻输出S的加法分为3段:X[7∶0]与S[7∶0]相加,产生的进位经1个时钟周期延时记为C1;X[15∶8]、C1与S[15∶8]相加,产生的进位经1个时钟周期延时记为C2;Y[20∶16]与前一周期产生的进位C2相加.该累加器完成100个数的累加需要102个周期,最后2个额外的周期,其输入X为0,只对前一时刻的进位进行累加.

3 芯片版图与性能

3.1 芯片版图

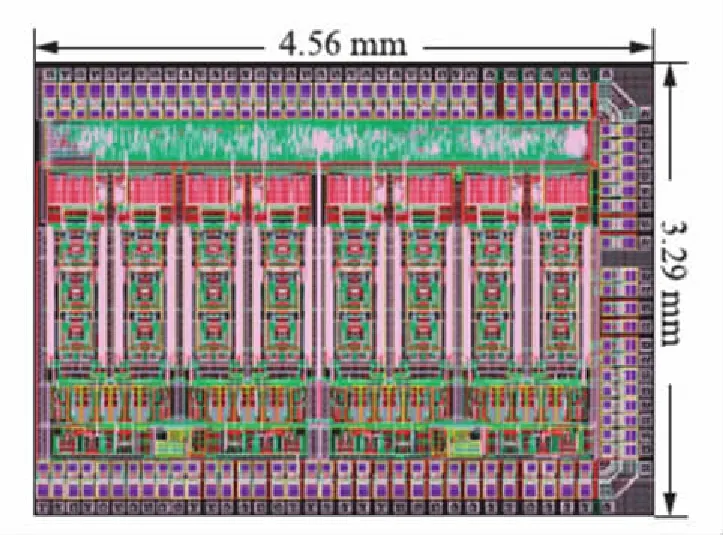

本设计实例采用0.35μm 2P4M CMOS工艺实现,芯片版图如图6中所示,芯片面积为4.56mm×3.29mm,内核面积为4.18mm×2.53mm.其中数字滤波器面积为4.18mm×0.32mm,仅占有约1/8的内核面积.流片由中科院高能物理研究所与其他电路一起工程流片时进行.

3.2 电路性能

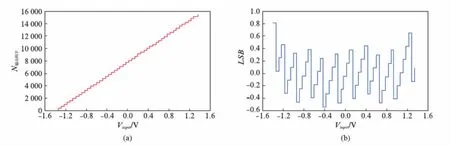

电路工作的电源电压为3.3V,时钟频率为64MHz.仿真中采用的输入信号来源于中科院高能物理研究所提供的实际CCD输出数据.输入信号的频率为1MHz,信号电平与浮置电平的差从0mV均匀变化到20mV,经前端放大器放大,范围变为-1.4~1.4V.图7(a)画出了采集到的1组输出码字与ADC输入电压的对应关系.图7(b)中画出了由这组数据计算出的余量(LSB),表中LSB=1.2μV,得到本设计的积分非线性为0.0096%.后仿真还得到等效输入积分噪声为13.53μV,整个模拟模块的功耗为1.12W,数字滤波器功耗234.06mW.

图7 (a)读出系统的输出数字码字和(b)余量Fig.7 (a) Output digital code and (b) output residual of the readout system

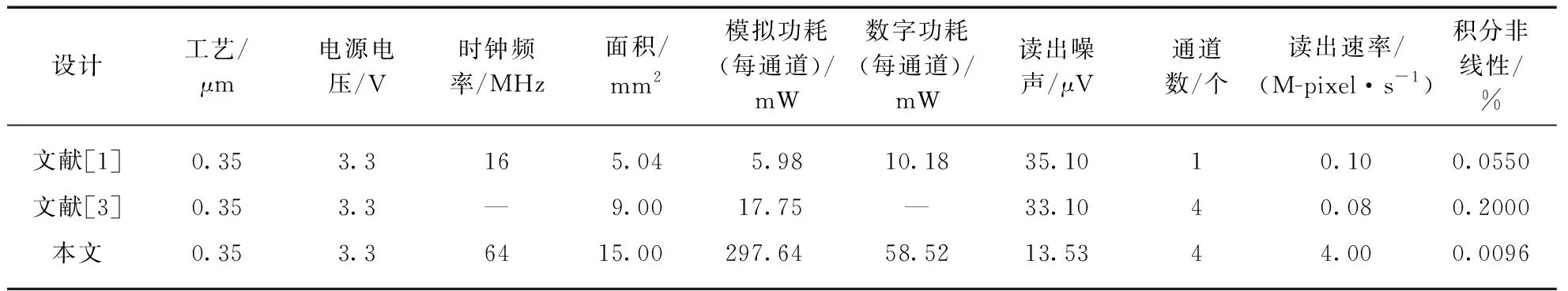

表1中总结了本设计的后仿真性能,并与同类X射线CCD读出芯片的测试结果进行了对比.本设计后仿真精度分别是文献[1]和[3]测试精度的5.7倍和20.6倍,单通道读出速率分别是10倍和50倍.为了实现上述精度和读出速率,本设计消耗了一定的功耗与面积,单通道模拟功耗分别是文献[1]和[3]的50倍和17倍,单通道面积分别是3倍和1.7倍.

表1 与同类X射线CCD读出系统的性能比较

注: 1) 本研究数据均为后仿真结果,文献数据为测试结果;2) “—”表示文献中无相关数据.

4 结 论

本文设计了一种4 M-pixel/s 4通道X射线CCD读出电路.本设计采用了SLD结构调制器,来缓解高速设计中时序紧张的问题.由查找表、流水型乘法器和流水型累加器构成的数字滤波器结构,避免了消耗较大的数字面积.

后仿真结果表明,本设计具有较好的精度与噪声性能,读出速率明显快于同类CCD读出电路[1,3].

参考文献:

[1] WANG Y, CAO X, YU Q, et al. A fully integrated 0.055% INL X-ray CCD readout ASIC with incremental ΔΣADC [J].IEEETransactionsonNuclearScience, 2016,63(3): 1733-1739.

[2] CAO X, WANG Y, FU Z, et al. A 95-dB DR second order incremental ΣΔ ADC for multi-channel healthcare application [J].AnalogIntegrCircSigProcess, 2015,82: 393-400.

[3] MATSUURA D, NZAWA H, MIYATA E, et al. Development of an analog LSI for readout of X-ray CCDs [J].NuclearInstrumentsandMethodsinPhysicsResearchA, 2007,570(1): 140-148.

[4] 曹骁飞.基于增量型Sigma-Delta模数转换器的X射线CCD读出系统的研究与设计 [D].上海: 复旦大学,2015.

[5] MENG X, CAO J, HE T, et al. A 19.2-mW, 81.6-dB SNDR, 4-MHz bandwidth delta-sigma modulator with shifted loop delays [C]∥2015 European Solid-State Circuits Conference (ESSCIRC). Graz, Austria: IEEE press, 2015: 221-224.

[6] XIN M, ZHANG Y AND HE T, et al. Low-distortion wideband delta-sigma ADCs with shifted loop delays [J].IEEETransactionsonCircuitsandSystemsI:RegularPapers, 2015,62(2): 376-384.