并联DC/DC系统中高速无线通信接收装置的设计

汪 涛,刘 升,葛芦生

(安徽工业大学电气与信息工程学院,马鞍山243000)

DC电源已广泛应用了分布式电源系统代替集中式电源,用小功率DC-DC变换器并联,以满足大功率负载要求[1]。随着并联DC/DC分布式电源系统研究的深入,一些先进的通信手段被用于电力电子系统中,无线通信作为未来通信的主流,DC/DC采用无线通信技术能够减少复杂的物理连线,拓展分布式电源系统的适用范围和简易系统的维护等。

将无线通信技术应用于DC/DC并联电源控制系统中,则设计一个高速基带信号处理无线收发硬件平台[2]尤为重要。目前基带信号处理作为软件无线电的关键技术之一备受青睐,国内外常采用单个处理器,如DSP、ASIC、FPGA等来处理基带信号;单个处理器均无法较好地满足软件无线电对高速基带处理平台的要求。因此,本文设计一种基于DSP+FPGA架构的基带信号处理平台。相比单个处理器,此硬件平台可以充分结合DSP与FPGA各自的优点,更好地发挥整体性能。

1 系统硬件平台设计

1.1 系统方案

针对DC/DC并联电源控制系统单次数据传输量小、信息高频的特点,本文设计以FPGA+DSP架构为核心,依托于高性能器件和高速接口搭建一个高速基带信号处理硬件平台。该平台具有灵活的处理结构,对不同结构的算法都有较强的适应能力,尤其适合实时信号的处理。基于DSP+FPGA架构的无线通信硬件平台整体结构如图1所示。

图1 无线传输硬件平台整体结构Fig.1 Overall structure of wireless transmission hardware platform

整体数字信号传输主要经基带信号处理、数模/模数转换、射频(RF)前端及智能天线收发。基带处理模块实现信号高速传输的正确收发、存储及实时处理,射频前端模拟正交上/下变频将基带信号调至工作频段。基带信号处理主要由DSP与FPGA来完成,而射频处理由射频前端电路来实现。

1.2 信号传输处理过程

由图1可知,无线数据传输硬件平台包括发射和接收两部分,本文主要研究接收装置部分,其系统架构如图2所示。

图2中,FPGA芯片完成基带信号处理及与射频前端衔接,完成数字下变频和数据预处理任务,还需完成对高速数据的接收、缓存以及配置控制的功能。此接收装置经智能天线接收到信号进入射频前端模拟正交下变频模块处理后送至A/D模块,FPGA通过高速接口接收A/D转化后的数据,先对数据进行数字下变频到基带,包括NCO、滤波、抽取等;再根据需要对基带数据进行预处理,如信号同步、解调、解帧等;最后通过并行输出至PC机显示控制界面。发射装置工作原理与其相反,不再赘述。

图2 接收装置系统架构流程Fig.2 Flow chart of the receiver's system architecture

2 硬件模块选择及接口设计

2.1 主要器件的选型

本系统高速的信号处理能力取决于信号处理各模块的选型。①DSP采用TI公司的TMS320C6713芯片,它是一款高性能浮点型芯片,主频达300 MHz,最高运行速度可达2 400 MIPS,且采用超长指令字结构,具有出色的运算能力、高效的指令集、智能外设、大容量的存储空间及大范围的寻址能力,专门面向复杂数据处理。②FPGA选用ALTERA公司的Stratix II系列芯片EP2S90F1020I4,该芯片拥有丰富的I/O引脚资源,方便与外围器件进行连接,门数资源也相当丰富,可以满足目前绝对大多数的信号处理硬件编程和控制能力。③AD采用Analog Device公司的AD9233芯片,它是一款单芯片,12位采样精度,125MSPS模数转换器(ADC),最高采样率可达125 MHz,模拟带宽最高可达650 MHz,可以做射频直接带通采样。④正交下变频模块选用ADI公司的AD8347芯片,它是一款单芯片、宽带800 MHz至2.7 GHz正交解调器。

2.2 基带处理模块接口设计

基带信号处理是由FPGA和DSP完成的。由图2可知,DSP芯片依靠EMIF接口与FPGA相连。在TMS320系列DSP上具有一种高速的接口EMIF,其设计是为了实现DSP与外部扩展存储器进行高速连接。本系统通过EMIF接口与FPGA相接,经FPGA与其他外部设备相连,使FPGA变成中转站,其他数据处理芯片可以通过FPGA将信号传输至DSP。DSP芯片只要通过EMIF接口就能实现对复杂系统的控制。DSP与FPGA接口连接如图3所示。

图3 DSP与FPGA的接口连线Fig.3 Connections at the interface between DSP and FPGA

图3中,DSP通过32位数据总线ED[31;0]、20位地址总线EA[21:2]及控制线CE[3:0]与FPGA相连。另外,DSP还有2根读、写信号线。DSP的读入/写出采用中断方式控制,当FPGA开始写出数据后,向DSP发送读中断请求,DSP响应中断读取数据。而当DSP要开始写出数据时,向FPGA发送接受中断请求,将处理好的数据放在总线上,等待FPGA的读入。

2.3 FPGA与射频前端接口设计

目前常见的RF前端架构有超外差架构和零中频架构,本设计采用的零中频架构[3](直接下变频架构)是由RF直接变成基带,而不经过中频的架构。接收装置RF前端完成主要功能有滤波,功率放大,正交下变频,I/Q解调,其结构框图如图4所示。来自智能天线的RF信号,经RF带通滤波器选择出有用信号后送入LNA放大,然后送入正交混频器,与可调频率的两路本振信号混频,直接产生正交(I)、同相(Q)两路信号输出,并分别经过低通滤波后送到ADC,然后通过A/D转换后送至高速基带处理模块。

以产生1 575 MHz波段为例,接收装置射频前端电路本文采用1 575 MHz无源发射接收智能天线(内含带通滤波器)、AD9233(双通道12位AD芯片)、AD8347(正交下变频芯片)、SI4133(本地振荡器芯片)和HMC476SC70(低噪声放大器LNA)等器件。FPGA通过SPI接口配置SI4133,则接收装置射频前端的硬件连接如图5所示。

图4 零中频架构接收机Fig.4 Channels in the receiver with zero-IF architecture

图5 接收机射频前端的硬件连接Fig.5 Hardware connections at the receiver's RF front-end

3 系统软件设计

系统采用基于BPSK的软件无线电开发平台[4]进行测试,此平台如图6所示。

图6 基于BPSK的软件无线电开发平台Fig.6 Software radio development platform based on BPSK

该无线电平台不包含复杂的通信算法,为减小开发周期,DSP不参与整个通信链路。将FPGA作为基带处理的核心芯片和整个链路的控制核心,与A/D、正交下变频模块和智能天线等组成完整的射频接收机电路。基带信号处理部分由FPGA完成,其他部分由对应的硬件电路完成。FPGA芯片的处理过程如下。

由于传统异步串口通信方式延时较长及速度慢问题,本文采用并行通信方式来发送和接收信号。在模块化的FPGA设计中[5],调用FIFO的IP core核作为并行数据收发的缓存寄存器,部分主要程序如下:

而FPGA通过SPI接口配置本振SI4133模块产生1 572 MHz的本振信号,对模拟正交下变频模块AD8347进行作用,如图5所示。顶层模块例化子模块程序如下:

在数字信号传输中BPSK解调和数据解帧是基带处理的核心,而数字下变频模块作用是对来自A/D数字化采样的高频信号进行下变频至基带,其中CIC滤波器模块用于对高频采样速率进行抽取、滤波,同时获得数据解帧时的码速率(CIC_OUT_ ENA),码速率即为每一位数据传输时的速率。而科斯塔斯环模块用于相干解调,恢复发送端发射的原始基带信号。由数字下变频模块中产生载波频率fn= 3 MHz的控制字计算公式[6]N=(fn/(2 fs))·232,得到N= 32’h7AE147B。顶层模块例化各子模块程序如下:

科斯塔斯环模块用于解调出基带信号 ZF_ BIT,例化程序如下:

数据解帧模块对解调出的基带信号进行串并转换,通过输出端口FIFO_WDATA与FIFO模块的输入端口data相连进行数据传输,例化程序如下。

4 测试结果

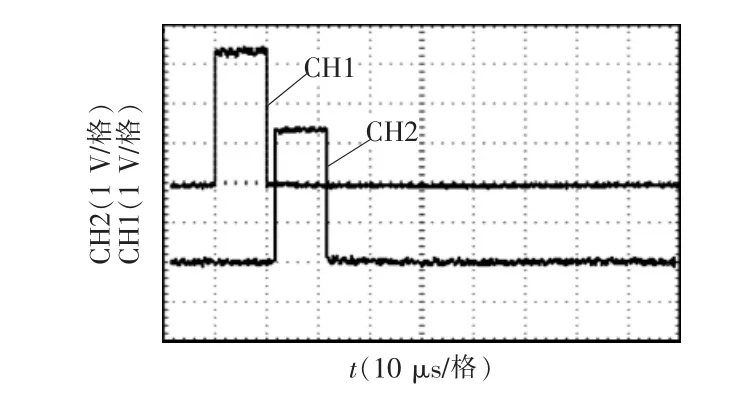

本系统时钟采样频率为fs=100 MHz,码速率为12.5 MHz,在完成程序模块化的编程之后,通过软件quartus II 11.0将程序配置到 FPGA中完成测试。由并行接口接收传输的数据,接收装置接收来自发射装置发送的数字“1”(00000001B),发射数据开关频率为100 kHz。通过FPGA的通用自由I/O端口引出RXD[0]、TXD[0]连接示波器,所采集的发射端和接收端的波形如图7所示。无线网络通信延迟是难以避免的,本实验延时t=12 μs,为1.2个传输周期。实验验证了基于FPGA+DSP无线通信接收装置进行实时基带处理的可行性,满足目前并联DC/DC电源系统中对无线传输的要求。

图7 CH2接收数字“1”(000000001B)Fig.7 Digit“1”(000000001B)received by CH2

5 结语

本方案能充分利用FPGA与DSP各自的优势,与常见的无线接收模块相比,无论软件的可编程性,还是硬件平台的通用性,都能满足科研项目对无线接收平台的要求。此外,无线接收模块在整体通信系统中至关重要,通过验证与优化的通信平台,使整个通信系统性能得到进一步的优化。

[1]Huang Yuehui,Tse C K.Circuit theoretic classification of parallel connected DC-DC converters[J].IEEE Transactions on Circuits and Systems I:Regular Papers,2007,54(5):1099-1108.

[2]谭左红,田增山.基于FPGA+DSP的高速基带信号处理平台的设计[J].科学技术与工程,2014,14(3):239-242,267.

Tan Zuohong,Tian Zengshan.The design of FPGA+DSP-based high-speed baseband signal processing platform[J]. Science Technology and Engineering,2014,14(3):239-242,267(in Chinese).

[3]林杰.2.4 GHz接收机射频前端的研究及设计[D].重庆:重庆大学,2010.

Lin Jie.Study and design of radio-frequency front-end of 2.4 GHz receiver[D].Chongqing:Chongqing University,2010(in Chinese).

[4]杨小牛,楼才义,徐建良.软件无线电技术与应用[M].北京:北京理工大学出版社,2010.

[5]夏宇闻.Verilog数字系统设计教程[M].3版.北京:北京航空航天大学出版社,2013.

[6]张阿宁,赵萍.基于FPGA的正交数控振荡器 (NCO)的设计与实现[J].电子设计工程,2011,19(17):149-151.

Zhang Aning,Zhao Ping.Design and implementation of orthogonal numerical control oscillator(NCO)based on FPGA [J].Electronic Design Engineering,2011,19(17):149-151(in Chinese).