基于FPGA的高速高效率数字下变频

戴曜泽,张 棋,徐小淇

(中国航天科工集团8511研究所,江苏 南京210007)

0 引言

数字下变频(DDC)的实现主要有2种途径:1)采用已有的专用DDC芯片;2)采用FPGA或DSP通用芯片直接构建DDC平台。但专用芯片一般要求数据率小于150 MHz,如AD6620正常工作的数据率小于70 MHz,HSP50016正常工作的数据率小于75 MHz。DSP芯片可高速执行乘累加操作,但只能实现串行操作,在高速并行数据实时处理方面能力较低,故数据处理速率难以满足使用要求。FPGA芯片可实现并行处理,但由于多个乘法器(DSP48E)级联造成的线延时和速度限制,难以实现数字下变频的高速处理,数据率一般不大于400 MHz[1]。

本文基于抽取器的等价原理,对数字下变频结构进行简化,可有效解决数据率过高引起的瓶颈问题,极大减少了数字下变频的计算量和FPGA片内资源消耗,是一种高速高效的数字下变频的实现结构。

1 数字下变频结构

1.1 数字下变频基本结构

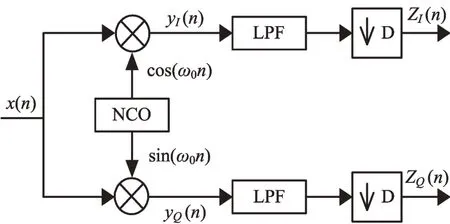

数字下变频基本结构是将中频信号转换为基带信号,基带信号的正交性由数控振荡器(NCO)本振来保证,经下变频后的数字基带信号处于严重的过采样状态,经过下变频滤波后抽取处理[2],其结构如图1所示。

图1 数字下变频基本结构

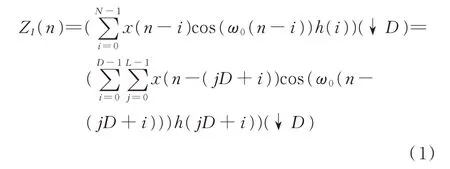

图1中,x(n)为经过A/D采样的数字中频信号;cos(ω0n)、sin(ω0n)为NCO生成的正交信号;LPF代表低通滤波器,滤除x(n)与NCO混频的高频信号;ZI(n)、ZQ(n)为经过D倍抽取的I、Q2路基带信号。数字下变频I路输出[3]ZI(n)可表示为:

式中,x(n-i)为x(n)延时i的输出;cos(ω0(n-i))为NCO第n-i时刻的输出,其中ω0=2πf0/fs,f0为信号的中频频率,fs为信号的采样频率;h(i)为滤波器的第i个系数;N为滤波器的阶数;L=N/D为每个通道滤波器阶数。

在工程实现中,为提高系统信噪比,需进行信号的高速采样,造成中频数据处理速率低;为了降低数字信号处理数据量,需进行数据抽取操作,过高的抽取倍数会导致很高的滤波器阶数,造成大量资源消耗[4]。为了解决速度和资源问题,本文提出了一种数字下变频改进结构。

1.2 数字下变频改进结构

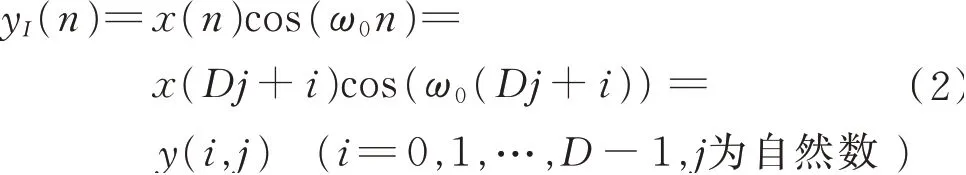

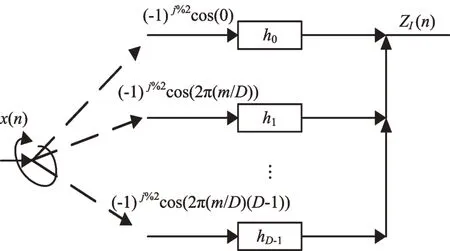

根据抽取器的对等关系[5]与式(1)对应的数字下变频基本型I通道的等效结构如图2所示。

图2 数字下变频基本型I通道的等效结构

在图2中,y(n)表示为:

当抽取倍数D为n的整数倍时,则式(3)可简化为式(4),其对应的数字下变频改进型I通道结构如图3所示。

图3 数字下变频改进型I通道结构(D为n的整数倍)

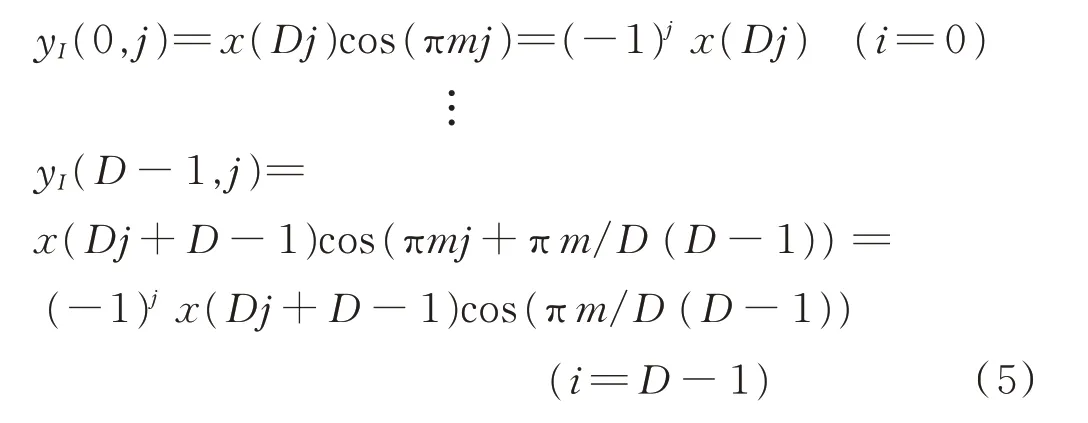

当抽取倍数D为n/2的奇数倍时,则式(3)可简化为式(5),对抽取数据对2取模,余数为0时数据不变;为1时数据取反,其对应的数字下变频改进型I通道结构如图4所示。

图4 数字下变频改进型I通道结构(D为n/2的奇数倍)

由图3—4可知,与数字下变频基本结构相比,数字下变频改进结构在滤波器前抽取,使数据量降低到原有的1/D,并将串行数据流转换为并行数据流,从而使系统数据处理速率提高D倍。

综上所述,在数字下变频结构设计时,需统筹考虑滤波器阶数N、数字中频频率f0、抽样频率fs以及抽样倍数D,使得抽样倍数D满足上述2个条件,从而选择相应的数字下变频改进结构。

2 数字下变频改进结构工程实现

2.1 Matlab仿真

假设输入信号x(n)为中频频率f0=50 MHz,带宽B=1 MHz的窄带信号。根据中频采样定理fs≥2B及1.2节所述可知采样频率满足式(6),可采用数字下变频改进结构设计实现中频信号到基带信号的转换。

假设n=0,则fs=4f0=200 MHz,抽取倍数D为4满足中频采样定理。

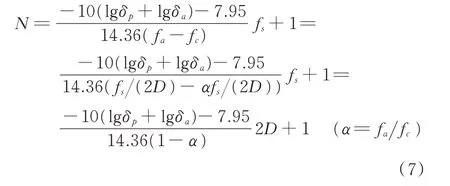

假设数字下变频低通滤波器的窗函数为凯塞窗,则滤波器阶数N为:

式中,δp为通带纹波系数,取90 d B;δa为阻带纹波系数,取90 d B;fa为阻带起始频率,取2.66 MHz;fc为通带截至频率,取1 MHz。由式(7)可知,滤波器阶数N为64阶。

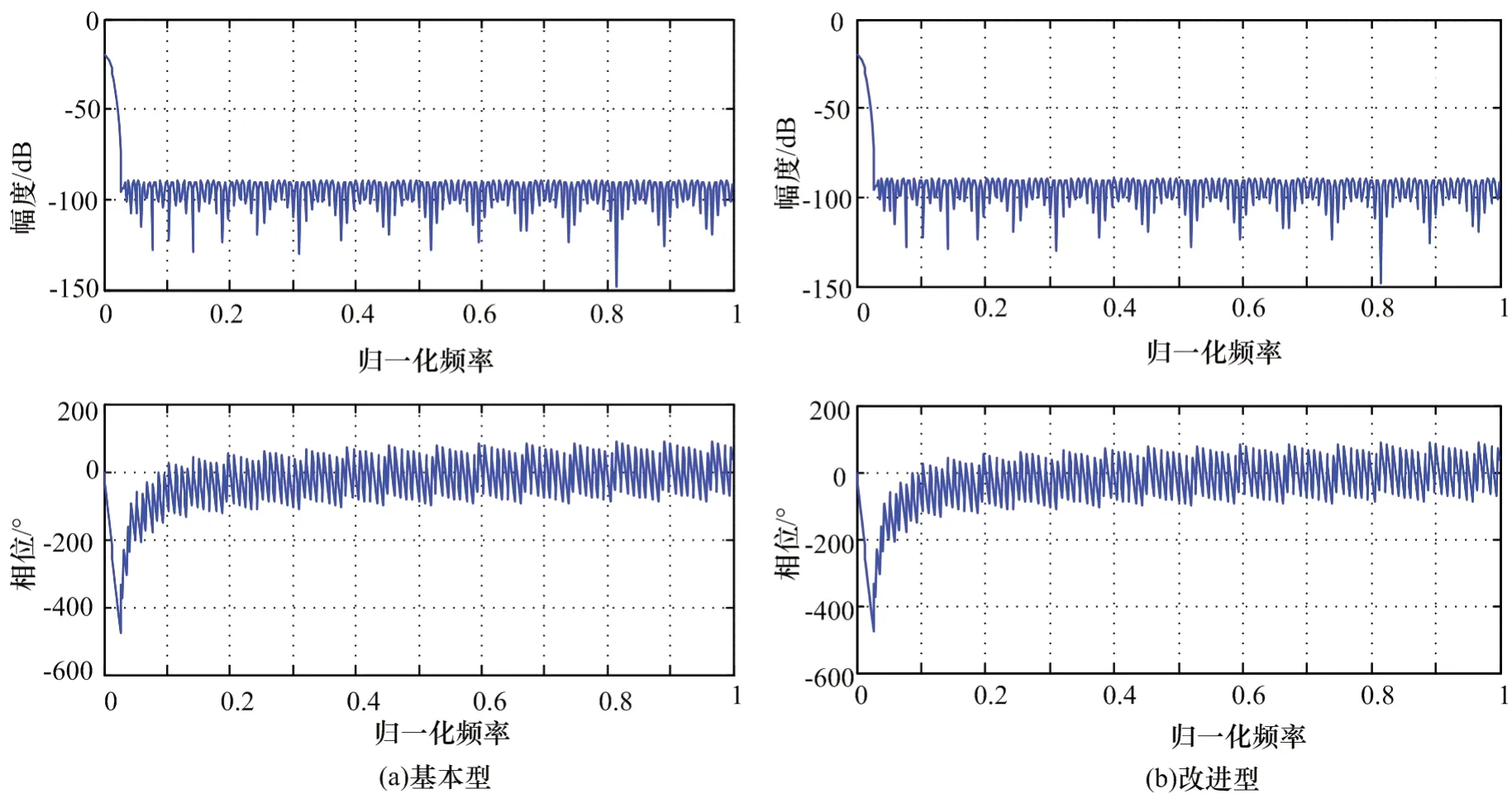

基于以上参数进行Matlab仿真,数字下变频基本结构和改进型结构I通道的Matlab仿真结果如图5所示。

图5 数字下变频基本型和改进型I通道Matlab仿真结果

由图5可看出,数字下变频的基本结构和改进型结构的时域及频域的输出结果是一致的,因此该改进型结构可完全代替数字下变频的基本结构。

2.2 FPGA实现

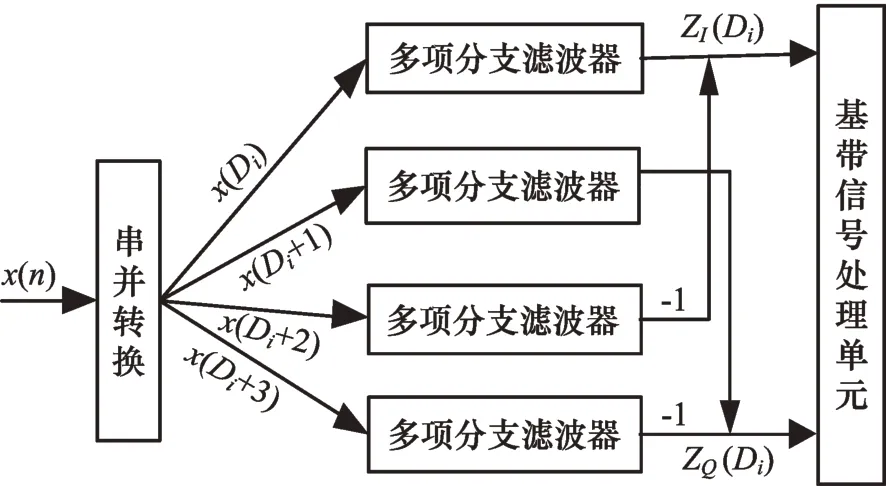

基于Matlab仿真结果,4倍抽取倍数的数字下变频改进结构的FPGA实现框图如图6所示。

FPGA芯片采用Xilinx公司的XC4VSX55(速度为-10),数字下变频基本结构和改进结构滤波器达到的最高时钟速率分别为222.561 MHz和247.610 MHz。在改进结构中,抽取倍数D为4,其数据处理速率可达到时钟的4倍,因此数字下变频改进结构可支持约900 MHz的数据率,从而解决中频数据处理速率低的问题。

图6 4倍抽取倍数的数字下变频改进结构FPGA实现框图

采用VHDL语言对数字下变频基本结构和改进结构进行FPGA软件实现,并采用Modelsim进行仿真,仿真结果如图7和图8所示。图中counter_out代表时延计数,out_i代表数字下变频I通道的输出。将图7、图8与图5比较可得,FPGA仿真结果与Matlab仿真结果一致,但数字下变频基本结构的FPGA实现存在40个时钟周期时延,而改进型结构仅存在24个时钟周期的时延,因此数字下变频改进结构的数据响应时间较快。

图7 数字下变频基本结构的FPGA仿真

图8 数字下变频改进结构的FPGA仿真

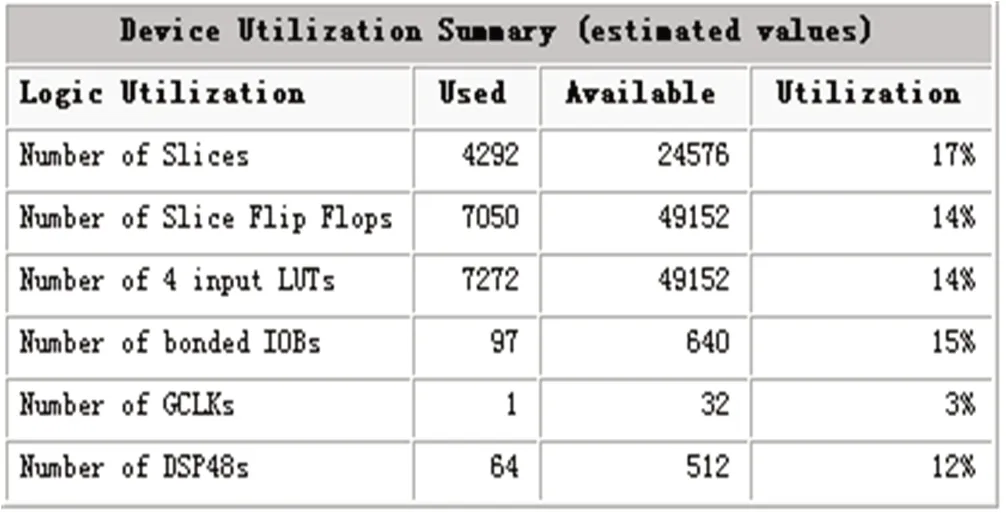

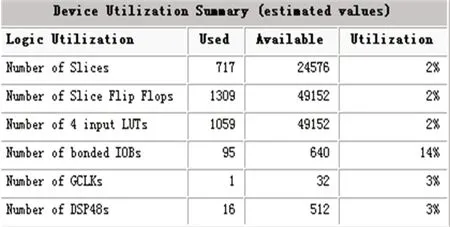

数字下变频基本结构和改进结构的FPGA芯片资源消耗分别如图9和图10所示。可以看出,改进型结构消耗的资源仅为基本型结构的1/4左右,在很大程度上降低了资源消耗,解决了FPGA片内资源问题。

图9 数字下变频基本型FPGA资源消耗

图10 数字下变频改进型FPGA资源消耗

3 结束语

本文针对数字接收机数字下变频基本结构数据处理速率低、数据响应速度慢及资源消耗大等问题,提出了一种高速高效的数字下变频改进结构。该结构利用抽取器的等价原理,对数字下变频结构进行简化,并通过FPGA工程实现,具备数据处理速率快、数据响应速度快及资源消耗小等优点,具有很好的实用价值和应用前景。