PCIe接口的BAC时统节点设计

(江苏自动化研究所,江苏 连云港 222061)

PCIe接口的BAC时统节点设计

郑波祥

(江苏自动化研究所,江苏连云港222061)

针对BAC时统节点在PCIe计算机系统中的应用,基于新型线性隔离和PCIe端点硬核应用和BAC码转换解析,实现了一种BAC时统节点设计;实现了该节点的总体电路设计,同时实现了BAC输入信号的线性隔离电路、迟滞比较输出BAC信号采样点电路、BAC信号的A/D转换采集电路、ALTERA FPGA的FIFO和PCIe端点硬核应用设计;基于FPGA实现的PCIe接口、FIFO和控制逻辑计以及实现的线性隔离,在简化节点设计的同时,也大大提高了适用性。

BAC;时统;PCIe;线性隔离;FPGA

0 引言

在电子信息控制系统中,用于提供给各个任务节点的同步时间信息的时统设备应用非常广泛,时统的制式主要包括PPS、IRIG-BDC、IRIG-BAC等。在某些环境恶劣、传输可靠性要求高的特殊场合中,仍在广泛使用BAC时统。由于BAC时统采用模拟正弦载波方式传输信息,作为任务节点的时统接收设备,需要完成信号隔离、数据采集、比较计算、存储输出等。在时统节点设计时,基于线性光隔离器件实现了信号隔离和比例功能,基于AD7610实现了数据采集,基于FPGA实现了比较计算等逻辑控制和运算等,基于ALTERA的FPGA的FIFO的应用设计[1],实现了时间数据的存储,特别是基于ALTERA的FPGA的PCIe端点设计方法,实现了X4的PCIe接口,并在FPGA内部,通过AVALON总线的主端和从端配置设计,实现了PCIe接口对FIFO的访问。同时,PCIe接口的实现,可以使该BAC时统设备能方便的应用于目前主流的计算机系统中,且该时统设备组成简单,可靠性高,大大提高了BAC时统设备的适用性。

1 电路组成

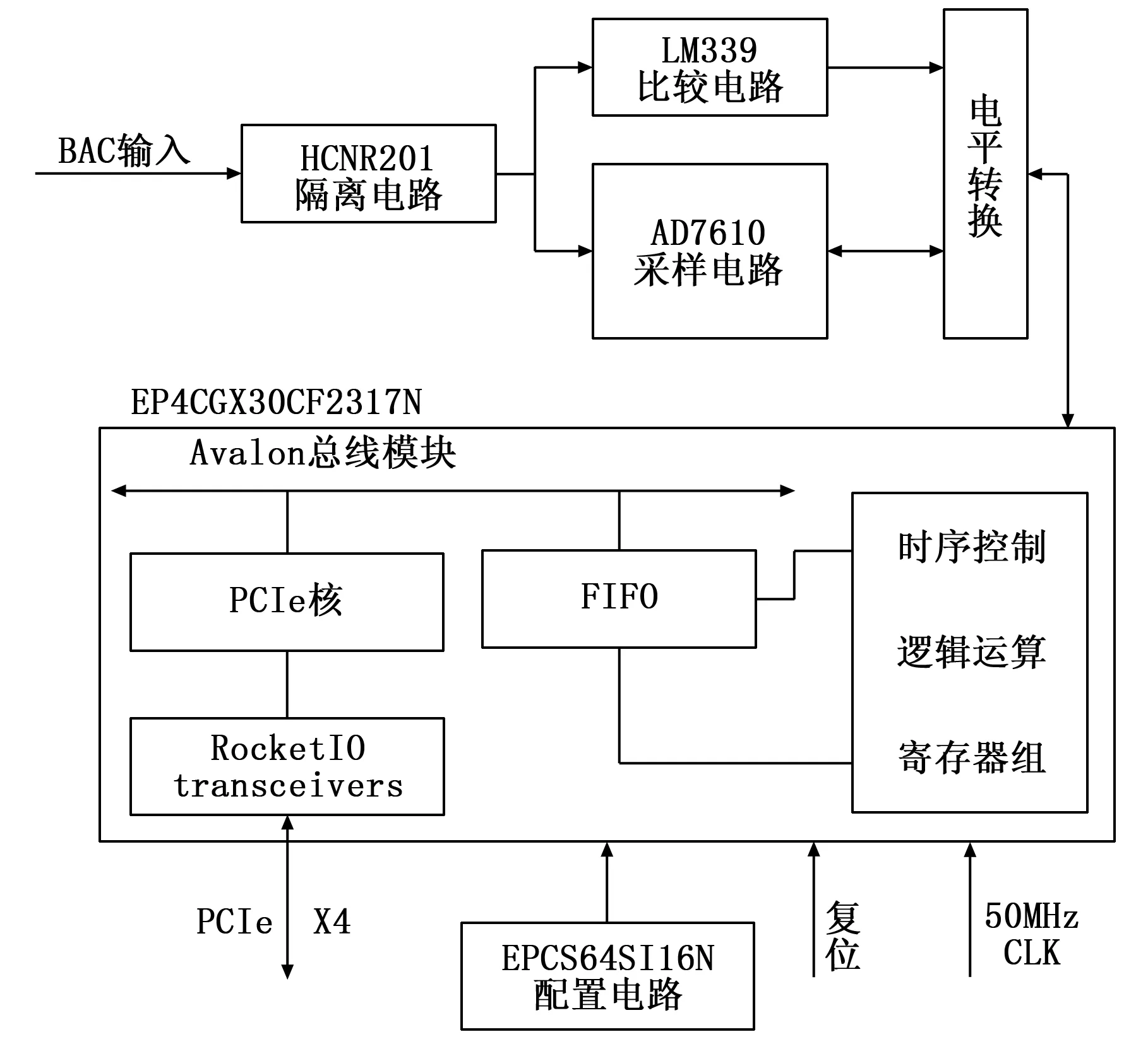

PCIe接口的BAC时统节点设计组成包括基于HCNR201的模拟信号线性隔离电路[2],基于LM339的比较输出采集触发沿信号电路,基于AD7610的双极性信号模数转换电路,适配5 V逻辑电平和3.3 V逻辑电平的转换电路,基于FPGA的模数转换控制逻辑、时统数据的运算和FIFO存储、PCIe硬核的PCIe端点等设计等,电路组成详见图1。其中,隔离电路主要实现对BAC输入输出的电气隔离,提高产品的环境适应性;比较电路主要实现AD转换控制的条件信号;AD转换主要实现采集BAC峰谷值,而FPGA逻辑主要实现AD转换时序逻辑和BAC码元识别,并根据码元计算获取时间值,同时实现PCIe端点接口。

图1 电路总体组成

2 电路设计

该时统节点的主要设计包括隔离电路、迟滞比较输出电路、转换和采集电路、码元识别和时间获取、PCIe接口等设计。

2.1 隔离电路

BAC时统输入信号为标准调制比为10:3、载频为1 kHz、高幅峰值最大为10 V的正弦波形的载波。光隔离器件HCNR201,具有0.01%的低非线性度、-65 ppm/℃的低增益温度系数、不小于1 MHz的带宽等特性[8]。线性隔离电路主要实现双极性载波信号的输入隔离和峰值适配调整输出。电路组成详见图2。

图2 线性隔离电路组成

为了保证满量程输出,先对BAC输入信号进行4/5分压,跟随滤波后再进行隔离,即-4 V≤Vin1≤4 V。根据HCNR201的线性隔离特性[9],需要保证其内部受敏管i1≤50 μA,所以正极性输入Vin1/R1≤50 μA,而负极性输入Vin1/R2≤50 μA,所以R1≥80 kΩ,R2≥80 kΩ,为保证满量程,一般取R1=R2=100 kΩ。同时根据HCNR201的线性隔离特性和运放U5虚短特性,BAC信号的正极性部分的隔离输入输出关系:

为了使输出信号Vout的幅值为-5~5 V,而-4 V≤Vin1≤4 V,所以R5+Rk=125 kΩ,选择定值电阻R5=80 kΩ,可调电阻Rk=50 kΩ,通过可调电阻调节,可以调整隔离输出信号的幅值为-5~5 V,图2中即为设计的各个电阻阻值配置。

由于HCNR201内部LED的反向电压不能超过9 V,电路中的二极管的主要作用是保护非工作的HCNR201内部LED不被击穿。如二极管D1采用常用的1N4148,主要实现负极性信号输入时,通过自身导通电压进而保护HCNR201(U3)内部的LED不被反向电压击穿,二极管D2的作用同理。如当输入为正极性BAC信号时,运放OPA1177(U1)的输出为负电压,通过限流电阻R6用以驱动光隔HCNR201(U3)的内部LED,使光隔HCNR201(U3)隔离电路工作[5],正信号隔离输出,二极管1N4148(D1)两端因为加反向电压而不导通;此时,运放OPA1177(U2)的输出为负电压,HCNR201(U4)隔离电路不工作,同时由于二极管1N4148(D2)两端加正向电压而导通,使得运放OPA1177(U2)的输出被钳位在约-0.7 V,保证了光隔HCNR201(U4)的LED反向电压不超过其反向击穿电压9 V。当输入为负极性BAC信号时,二极管D1起到同样的作用。

隔离输出通过运放输出分成两路,一路进入比较器电路,另一路进入AD转换和采集电路。

2.2 迟滞比较输出电路

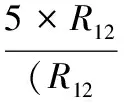

隔离输出后的信号是模拟正弦信号,为了得到正弦信号波峰和波谷对应的边沿信号,需要把隔离输出的一路引入比较器LM339,实现和正弦信号零点对齐的沿信号输出。LM339是一种最大±36 V供电的电压比较器,具备nA级的偏置电流和偏移电流,比较输出是开漏电极OD门,兼容TTL、CMOS、MOS电平输出。

隔离输出后的信号通过10 K欧姆R11的平衡电阻和比较器LM339的正端相连,通过10 K欧姆电阻R12和210 K欧姆电阻R13组成正反馈电路,构成一个迟滞比较电路,电路组成见图3。设计正反馈电路,一方面可以避免因为输入信号中叠加的门限值附近干扰,引起的比较输出电压的抖动;另一方面也加大了比较器的响应速度。LM339的比较输出为开漏电极OD端,通过5V上拉电阻输出TTL电平。

当比较器输出为逻辑低时,比较器正端VT-=0V;

所以比较迟滞门限窗口VT=0.218V。

由于是反向比较,所以输出和输入正好反相,需要在FPGA内部进行逻辑取反并倍频后作为AD转换控制信号。LM339的输出频率为1 kHz的逻辑信号到FPGA,经FPGA输出反向的频率为2 kHz的逻辑信号,该逻辑信号的下沿对齐BAC输入信号的峰峰和峰谷处。

图3 迟滞比较电路组成

2.3 转换和采集电路

转换电路主要是把隔离输入的BAC信号进行模拟和数字的转换,通过FPGA时序逻辑控制以及FIFO存储完成码元的识别和时间信息的采集。AD转换采用了AD1764转换器,该转换器的特性是12位数字输出,单次采样时间10 us,支持-5~5 V(分辨率0.002 44 V)和-10~+10 V(分辨率0.004 88 V)的双极性模拟信号输入。实际工作时,利用-5~5 V(分辨率0.002 44 V)输入端口;供电为5 V逻辑电压和±15 V模拟电压;工作模式为模拟双极性输入和STAND-ALONE模式。所有的控制线经过电平转换输入FPGA处理。在STAND-ALONE工作模式下,控制信号CE、12/8拉高处理,,控制信号CS、A0拉低处理,AD转换和数字数据输出由R/C(AD输入,下沿启动AD转换)和STS(AD输出,指示转换完成和数据输出)控制。

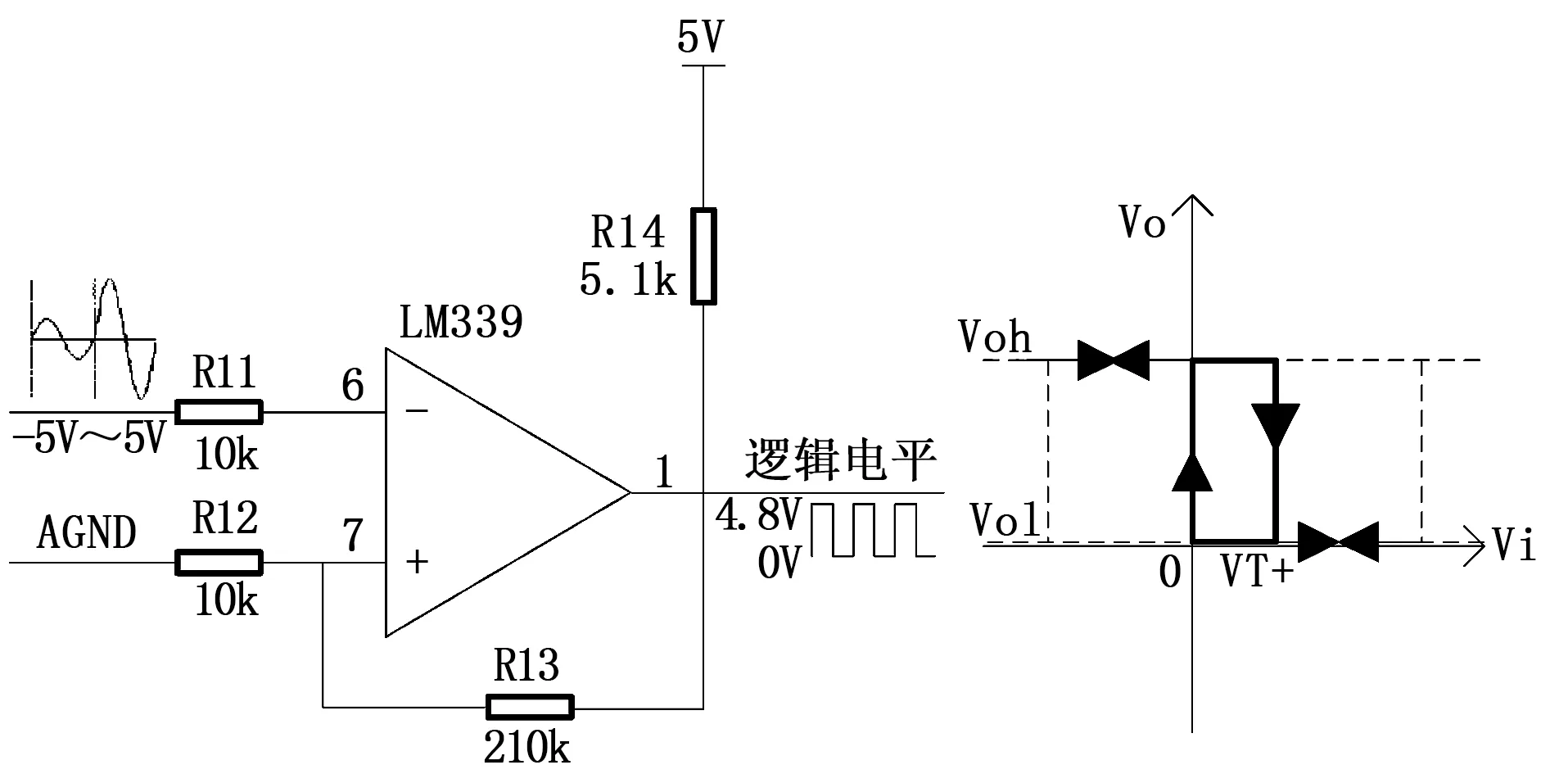

AD转换的输入信号是最大幅值-5~5 V的正弦,AD7610的转换触发信号为/CNVST输入信号,该信号可以通过连接FPGA输出的反相倍频迟滞比较信号,实现AD转换控制,即/CNVST出现下沿,AD7610开始转换。/CNVST信号抖动要非常小,所以走线时应该用地屏蔽,并在驱动此线路的器件输出端增加一个低30欧姆始端匹配阻值,减少反射振荡。对AD转换后的数据采集需要通过FPGA设置AD7610的/CS、/RD端一直处于低有效状态,FPGA以AD7610的BUSY信号的下降沿为数据采集触发信号,实时采集AD转换后的16位数据。AD转换和采集电路的关键信号时序设计详见图4。

图4 采集转换时序设计组成

实际转换和采集过程中,需要对BAC正弦信号每个周期的峰峰值和峰谷值进行转换和采集[3],以峰峰值和峰谷值的差值作为计算码元的数据,一方面可以提高比较用的基准阀值[4],另一方面也减少了码元计算的误码率。

比较输出是个边沿对应BAC信号零位的1 kHz频率的方波信号,输入FPGA经倍频后输出1 kHz频率的方波信号,该方波信号下降沿按周期对应BAC信号波峰和波谷,由于需要采样的就是BAC信号波峰和波谷,所以该方波信号可以作为AD7610的转换触发信号。而AD7610的BUSY输出信号作为转换数据读信号/RD和片选信号/CS的条件,当BUSY输出信号为低时,即AD转换结束后,FPGA置/RD和片选信号/CS为有效低信号,从而读取AD7610输出的16位转换数据。

2.4 码元识别和时间获取

采集BAC时统输入信号后,需要根据幁格式要求,识别出幁内的码元信息,进而获取秒、分、时、天等时间信息。首先需要识别码元,码元识别要素是在10 ms的20次AD转换和采集周期内,识别连续高幅正弦波个数,如连续2个高幅正弦波为0码元,连续5个高幅正弦波为1码元,连续8个高幅正弦波为P码元,而且码元特征是连续高幅的正弦波在前。

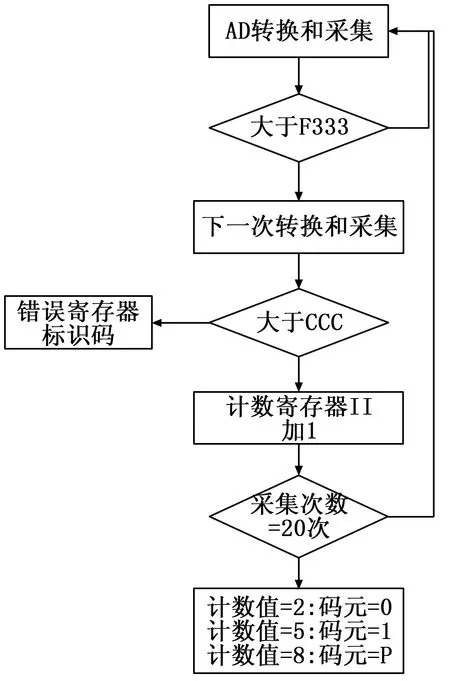

为了在转换采集过程中能准确的识别BAC正弦信号的波峰和波谷值,在FPGA内部设置一个AD采样阈值寄存器,支持设置一个12位的阈值,作为12位AD采样的数值的输出比较参照,若AD采样值大于该阈值,输出为“1”,若小于该阈值,输出为 “0”。该阈值可设置,D11-D0为阈值数值,同时可以通过读取WR8,读回该阈值数值量。实际工作中,AD转换和采集高幅正弦波的峰值大于阀值FFFF(+4.5 V)则有效,如果检测到有效的高幅正弦波的峰峰值,则进入下次转换和采集,如果检测到有效的高幅正弦波的谷值小于阀值CCC(-4.5 V),则计数寄存器II内容增加1,直到完成20次转换、采集和检测,并根据计数寄存器的值识别出码元。码元识别流程见图5。

图5 码元识别流程

识别出码元后,可以根据BAC信号的幁格式,获取时间信息。首先分辨出幁的起始头即两个连续P码元,确认是有效幁开始,按位获取码元值即可。

在FPGA内部设置一个32位BAC码时间寄存器,时间寄存器为只读,无论有无外部BAC码时统输入,都可以通过读取该寄存器,来获取当前时间信息,若无外部输入,可设置BAC码初值设置的时间信息,依据本模块的晶振逐秒增加自守时,一旦判断有外部BAC时间输入且有效,该值就会跟踪BAC码输入值,如果再次BAC输入消失或无效,则进入自守时,依次类推,也可以通过读取该寄存器,可以读取当前时间状态,该寄存器位号信息包括D29~D20(共10位),表示BAC码的0到365天时间信息;D19~D14(共6 位),表示BAC码的0~23小时时间信息;D13~D7(共7 位),表示BAC码的0到59分钟时间信息;D6~D0(共7 位),表示BAC码的0到59秒钟时间信息。

当无外部BAC时间输入时,为了自守时,在FPGA内部设置一个32位BAC码时间初值设置寄存器,时间初值设置寄存器为只写,当无外部BAC码时间输入时,为了自守时,通过主机向该寄存器写入一个时间初值,作为自守时的时间初始值,该寄存器需配合时间初值设置load寄存器的写操作一起工作,该寄存器位号信息同时间寄存器。

同时,为了存储时间信息,以及实现数据采集通道的数据缓冲,实现速率匹配,需要基于ALTERA公司提供的FIFO Core定制一个异步的4 KB的32位宽FIFO[5],用于存储时间信息,该FIFO应该是可以在不同的时钟信号下进行异步的读写。其中FIFO的读相关信号如read、readdata、reset、分别与AVALON总线相同命名的信号线相连,readclk与AVALON总线中clk相连,写相关信号wr_n、rd_n、writedata等由FPGA时序逻辑产生,把BAC码时间寄存器同步写入FIFO,供主机通过PCIe接口读FIFO以获取时间信息。

2.5 PCIe端点设计

PCIe端点是基于ALTREA FPGA上实现设计的,ALTREA公司提供了PCIe的IP核,IP核完全符合 PCIe 协议的各个层级要求,包括物理层、数据链路层和事务层。PCIe IP核具备高性能、高灵活性、高可靠等特点,支持 x1、x2和x4多种链路宽度,支持链路和极性的错序连接。PCIe IP核包括用户逻辑接口、配置接口、物理层和系统接口,基于用户逻辑接口,可以根据应用要求编写本地总线逻辑,进而实现应用与 IP 核的通信,配置接口只要用于主机对IP 核进行配置或读取状态信息,物理层就是高速差分信号的通道,系统接口包括时钟和复位信号。

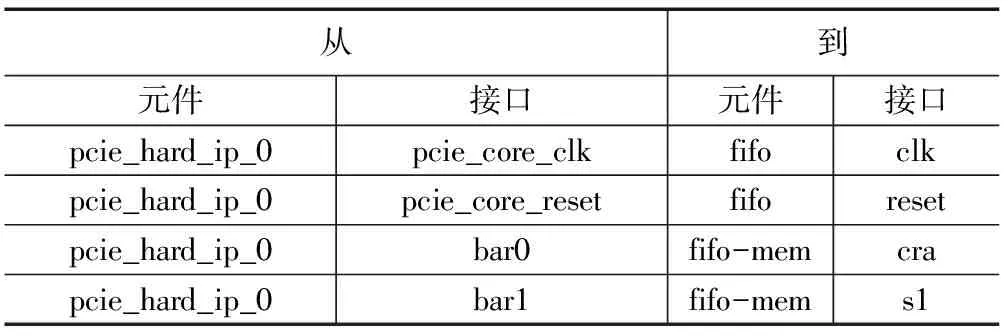

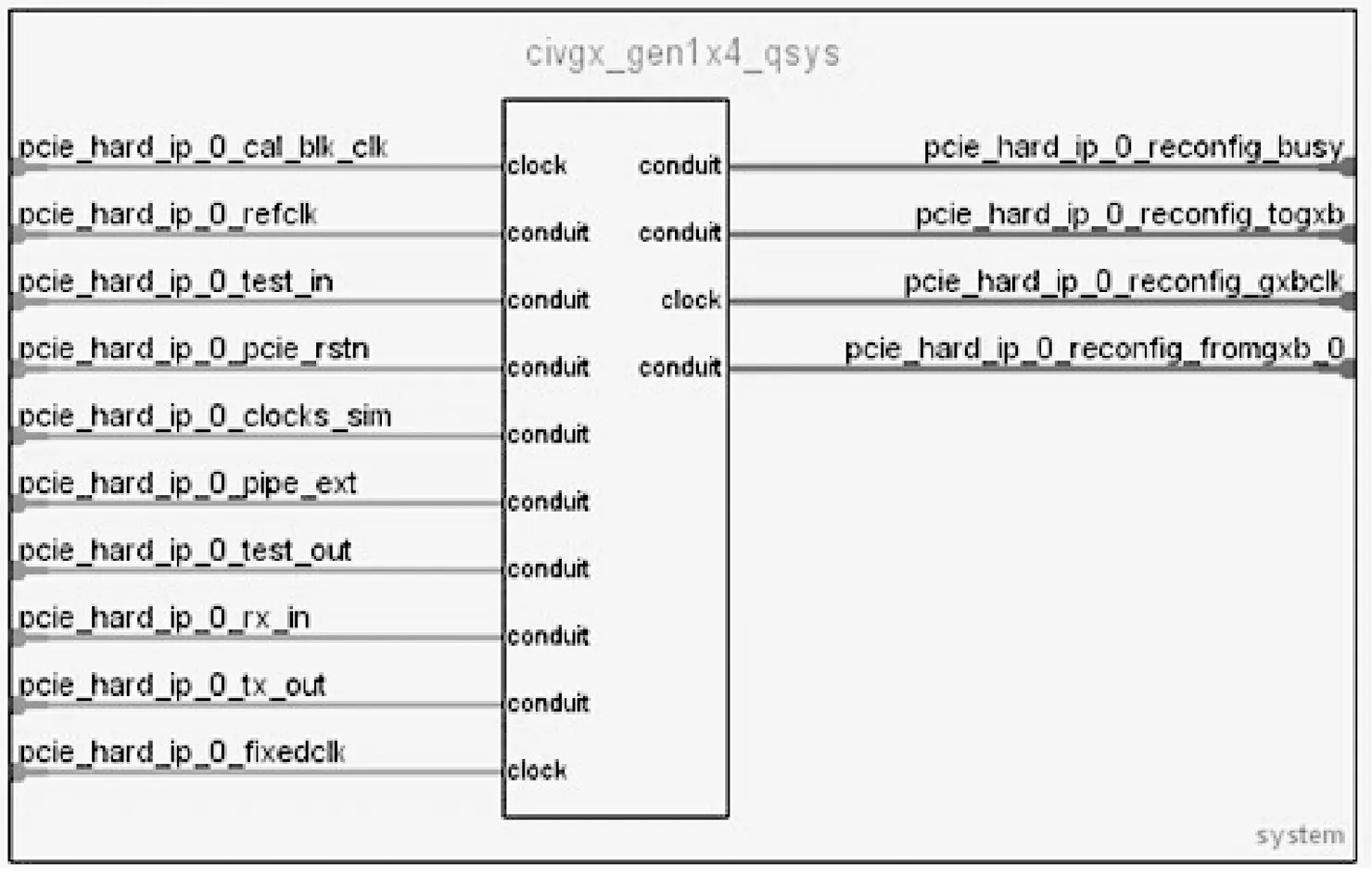

所使用的FPGA为Altera最新的CycloneIV GX FPGA器件EP4CGX30CF2317N,内部集成了8个3.125-Gbps收发器。基于ALTERA的QuartusII和Qsys软件实现PCIe端点的过程中,主要配置的参数包括:参考时钟、链路宽度、设备 ID、基址寄存器、TLP 大小,以及包含设备在总线域使用的地址范围的BAR基址寄存器。基于ALTERA的PCIe端点硬核实现了PCIe接口设计[6],主要是在Quartus II中完成 器件型号EP4CGX30CF2317N选择和工程创建,在 Qsys中完成如x4 Lane、100 MHz Reference clock 等PCIe硬核通用配置以及基地址寄存器[7]、端点配置只读寄存器、访问寄存器的Avalon-MM接口、Avalon地址转换等配置。地址转换配置时,把地址转换表配置选择动态转换表,地址页选择2,每页地址范围选择1 MByte~20 bits,通过这些设置控制Avalon-MM到PCI Express的地址转换,实现了Qsys系统内部的数据传输是如何转换为PCIe的请求的。由“pcie_hard_ip_0”的PCIe硬核已经基本完成,之后需要对PCIe硬核的在Avalon总线上的不同接口进行连接,如将PCIe的输出时钟pcie_core_clk连接到片内FIFO的clk端口等[8],详见表1。最后完成基地址分配和中断挂接等,生产的X4 PCIe硬核如图6所示。

表1 PCIe硬核的主要接口连接

图6 PCIe硬核接口组成

3 结论

基于上述设计成果研制了6U结构的CPCIe时统接口模块产品,目前该产品已经应用于某船载控制系统中,该模块作为某CPCIe加固计算机的接口组成,一方面接收外部时统系统以BAC码形式发送的授时信息,并且该模块具有对时功能,另一方面根据CPCIe计算机主模块的控制指令要求及相应的VxWorkS接口函数,通过PCIe接口向主模块提供了天时分秒等时统信息。

同时,通过利用识别的BAC信号帧头的同步沿信号,即同步于BAC解调输出的信号,可以供计算机时间同步中断使用。在FPGA内部设计中断用寄存器,而且根据同步频率和同步宽度要求,可以向主机输出时统系统的同步中断。可选频率分别为:1 MHZ,100 kHz,10 kHz,1 kHz等4种频率,脉宽也可以软设置,频率选择是由一个32位频选寄存器控制,其中D15-D0为正脉宽计数值,可以设置输出时钟脉宽,D31-D16:频率计数值 ,可以设置输出频率。也可以从频选寄存器中读取相应的数字。该CPCIe时统接口模块在没有外部时统信号输入时,通过板载温补晶振,提供守时脉冲信号,具有自守时功能。时统接口控制界面组成见图7所示。

图7 时统接口控制界面组成

通过CPCIe时统接口模块在CPCIe计算机系统中的应用验证,一方面很好的适应了计算机新型系统总线PCIe的发展应用需求,另一方面基于FPGA实现了PCIe接口和控制逻辑,可以更好的根据应用需求进行适用性改进,提高了产品的应用能力。

[1] 潘 松,黄继业,曾 毓.清华大学出版社SOPC技术实用教程[M].2005:30-31.

[2] 王 远.模拟电子技术.机械工业出版社,1997:55-57.

[3] 张明迪. 基于FPGA的IRIG-B码解码设计[D].哈尔滨工程大学,2011,45-47.

[4] 王丽娜.基于FPGA的IRIG_B码基带接收电路的实现[D].苏州大学,2014:18-20.

[5] ALTERA.Avalon Memory-Mapped Interface Specification.2007.

[6] 严 华. IPTV技术与发展探讨[J].计算机应用,2008(2):59-61.

[7] 李晓含,张 航,倪光华.基于Avalon-MM突发传输的PCI从接口设计[J].无线电工程,2015,45(6):38.

[8] 沈 辉,张 萍.FPGA在PCIExpress总线接口中的应用[J]. 现代电子技术,2010.33(14):110.

[9] 李木国,黄 影,刘于之.基于FPGA的PCIe总线接口的DMA传输设计[J].计算机测量与控制,2013, 21(1):235.

DesignofBACTimeNodeforPCIeInterface

Zheng Boxiang

( Jiangsu Automation Research Institute, Lianyugang 222061, China)

In view of the application about BAC time node in the PCIe computer system, Based on the PCIe endpoint hard core and BAC conversion with code parsing , a BAC time node design is implemented.The overall circuit of the node is realized,which is including BAC input signal linear isolation circuit, hysteresis comparison output circuit for BAC signal sampling ,and A / D conversio n acquisition circuit.FIFO storage and PCIe endpoint are also realized based on ALTERA FPGA. The node has simple composition and Good applicability through linear isolation and FPGA integration design about PCIe,FIFO and control logic.

BAC;time system;PCIe;linear isolation;FPGA

2017-07-09;

2017-08-23。

郑波祥(1977-),男,浙江上虞人,硕士研究生,主要从事抗恶劣环境计算机方向的研究。

1671-4598(2017)11-0220-04

10.16526/j.cnki.11-4762/tp.2017.11.056

TP336

A