栅氧化方式对NMOS器件总剂量电离效应的影响

刘佰清,刘国柱,吴健伟,洪根深,郑若成

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

栅氧化方式对NMOS器件总剂量电离效应的影响

刘佰清,刘国柱,吴健伟,洪根深,郑若成

(中国电子科技集团公司第五十八研究所,江苏无锡 214035)

基于抗辐射0.6 μm CMOS工艺,对5 V/20 Vamp;LV/HV NMOS器件进行了总剂量加固结构设计,并采用叠栅氧工艺成功制备了抗总剂量能力≥500 krad(Si)高低压兼容的NMOS器件。重点研究了不同的栅氧化工艺对NMOS器件总剂量辐射电离效应的影响作用。研究发现,在抗总剂量电离能力方面,湿法氧化工艺优于干法氧化工艺:即当栅氧厚度小于12.5 nm时,LVNMOS器件因总剂量电离效应引起的阈值电压漂移ΔVtn受栅氧化方式的影响甚小;当栅氧厚度为26 nm时,HVNMOS器件因总剂量电离效应引起的阈值电压漂移ΔVtn受栅氧化方式及工艺温度的影响显著。在500 krad(Si)条件下,采用850℃湿氧+900℃干氧化方式的HVNMOS器件阈值电压漂移ΔVtn比采用800℃湿氧氧化方式的高2倍左右。

栅氧化;总剂量电离效应;阈值电压漂移ΔVtn

1 引言

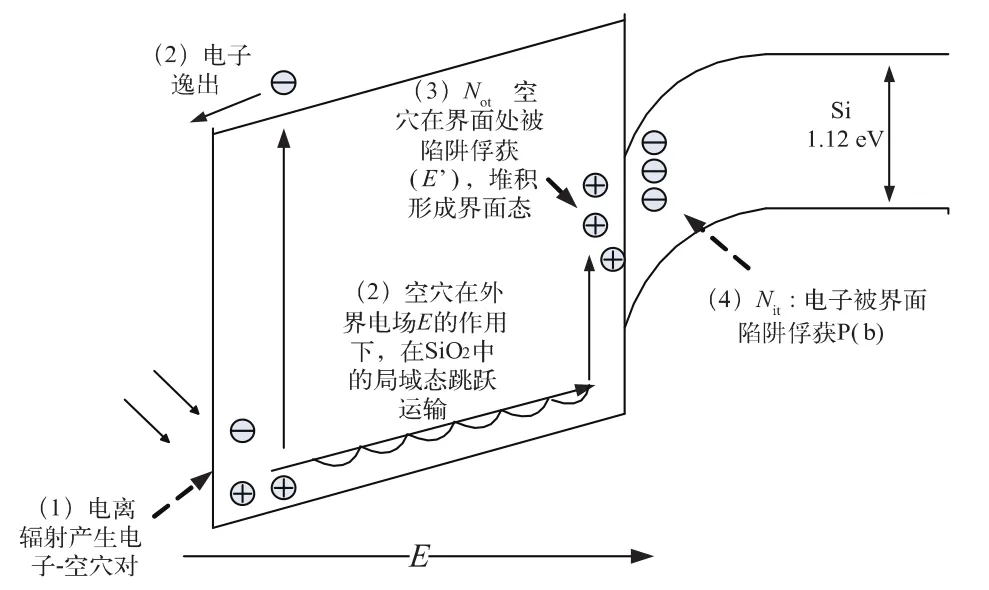

总剂量效应(Total ionizing dose effects,TID)由辐射源产生的γ光子或高能离子在集成电路材料中电离产生电子-空穴对,电子空穴随即发生复合、扩散和漂移,最终在氧化层中形成氧化物陷阱电荷或者在氧化层与半导体材料的界面处形成界面陷阱电荷,使器件的性能降低甚至失效。总剂量电离辐射产生的电荷或非平衡载流子的输运、复合、俘获、积累、退火与电场、温度、杂质、缺陷、界面结构和电离辐射方式等密切相关[1~3]。辐射的基本原理如图1所示,高能粒子轰击二氧化硅,诱发产生大量电子-空穴对,由于电子迁移率远大于空穴迁移率,在电场的作用下,电子快速移出SiO2层,而空穴由于输运速度慢,则在SiO2体内跳跃输运,由于在Si/SiO2界面处有很多因氧原子空位和晶格失配形成的空穴陷阱中心,其中一部分空穴跃迁至Si/SiO2界面附近时被氧化层陷阱俘获,形成正电荷积累。实际上电子也会有少量被SiO2中的深电子陷阱俘获形成负的空间电荷,由于数量上相对较少,因此整个二氧化硅层的电荷量表现出正电荷。同时辐射在SiO2/Si界面处打破共价键,形成界面陷阱电荷。这两种机制所形成的电荷积累均会对CMOS器件产生影响,并导致CMOS电路的性能、功能和电流产生较大影响,随着剂量的增加,器件性能逐渐降低,当剂量积累到一定程度时,器件发生功能性失效。

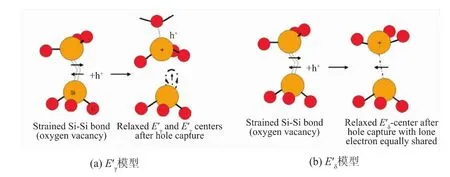

据文献[1,6,7]介绍,总剂量辐照对氧化层中产生的正电荷主要是由于中性的氧空位(陷阱中心)俘获了空穴,即 E′陷阱中心,其主要包括 Eδ′和 Eγ′,模型机理如图2所示。Eδ′为分布于整个SiO2体内的浅能级陷阱中心(禁带中的能级大约1.0 eV),Eγ′为深能级陷阱中心(禁带中的能级大约3.0 eV),该类陷阱中心与界面电荷的交换作用不显著,通常被视为氧化层中固定的正电荷,即Not。发生电荷交换的E′主要分布于SiO2/Si界面约3 nm的SiO2中,此类陷阱为边界陷阱(border traps or switching oxide traps),即 Nit,电荷交换的方式主要通过电子隧穿的形式实现,其电荷交换时间约10-6~1 s。

图1 总剂量辐射效应在SiO2中的辐射机理[3]

图2 总剂量电离效应引起在SiO2/Si界面处的SiO2中产生E′陷阱中心模型示意图

据文献[4,5,6]介绍,当栅氧厚度小于100 nm时,总剂量辐照电离效应在SiO2/Si界面陷阱产生和建立的速度与栅氧化方式的选取有关。研究发现[4,5],在同等栅氧厚度、正栅偏置辐射条件下,干氧化工艺栅氧界面陷阱建立的时间是湿氧化方式的1.3~2.2倍,其陷阱的速率与氧化层厚度呈现Tox-0.4关系;干法氧化栅氧中产生的空穴陷阱距SiO2/Si界面的距离比湿法氧化栅氧小;干法氧化栅氧中电子陷阱的产生率比湿法氧化栅氧高。

由于氧化工艺及氧化后的退火处理对界面区的弱键密度有较大影响;一般中温(~1000℃)干氧生长的SiO2/Si界面较好;在栅氧加固工艺中,应避免界面生长之后的高温处理。用氦、氩等惰性气体作用退火气氛,可明显降低界面处的≡Si-OH和≡Si-H。因此,在高压抗辐射栅氧加固工艺中,需要重点考虑通过降低界面陷阱的方式增强器件的抗总剂量能力。

本文基于抗辐射0.6 μm CMOS工艺,研究了厚度为10~30 nm的NMOS器件其栅氧氧化方式对TID效应的影响。

2 实验

2.1 样品制备

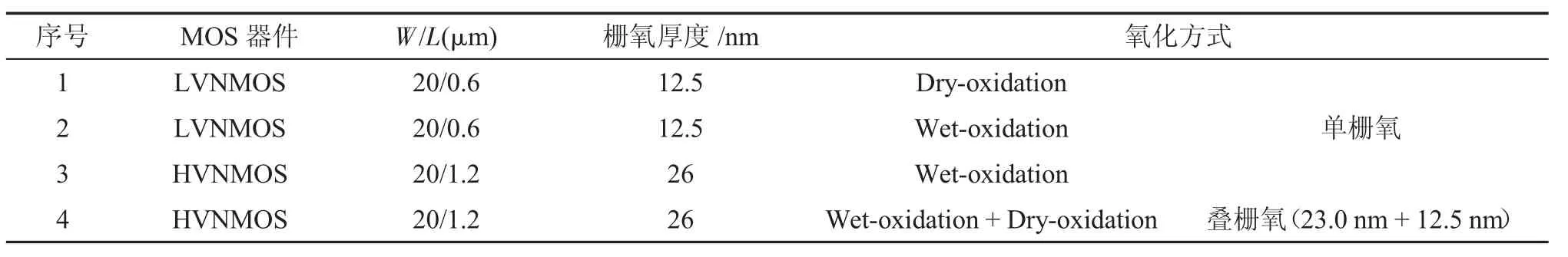

本实验主要研究了两种不同栅氧化方式NMOS器件的总剂量辐射电离效应,其器件及制备工艺条件如表1所示,其中LVNMOS器件栅氧采用单栅氧工艺进行制备,HVNMOS器件的栅氧采用单栅氧、叠栅氧(23.0 nm+12.5 nm)工艺进行制备。

表1 NMOS器件特征参数

2.2 器件结构

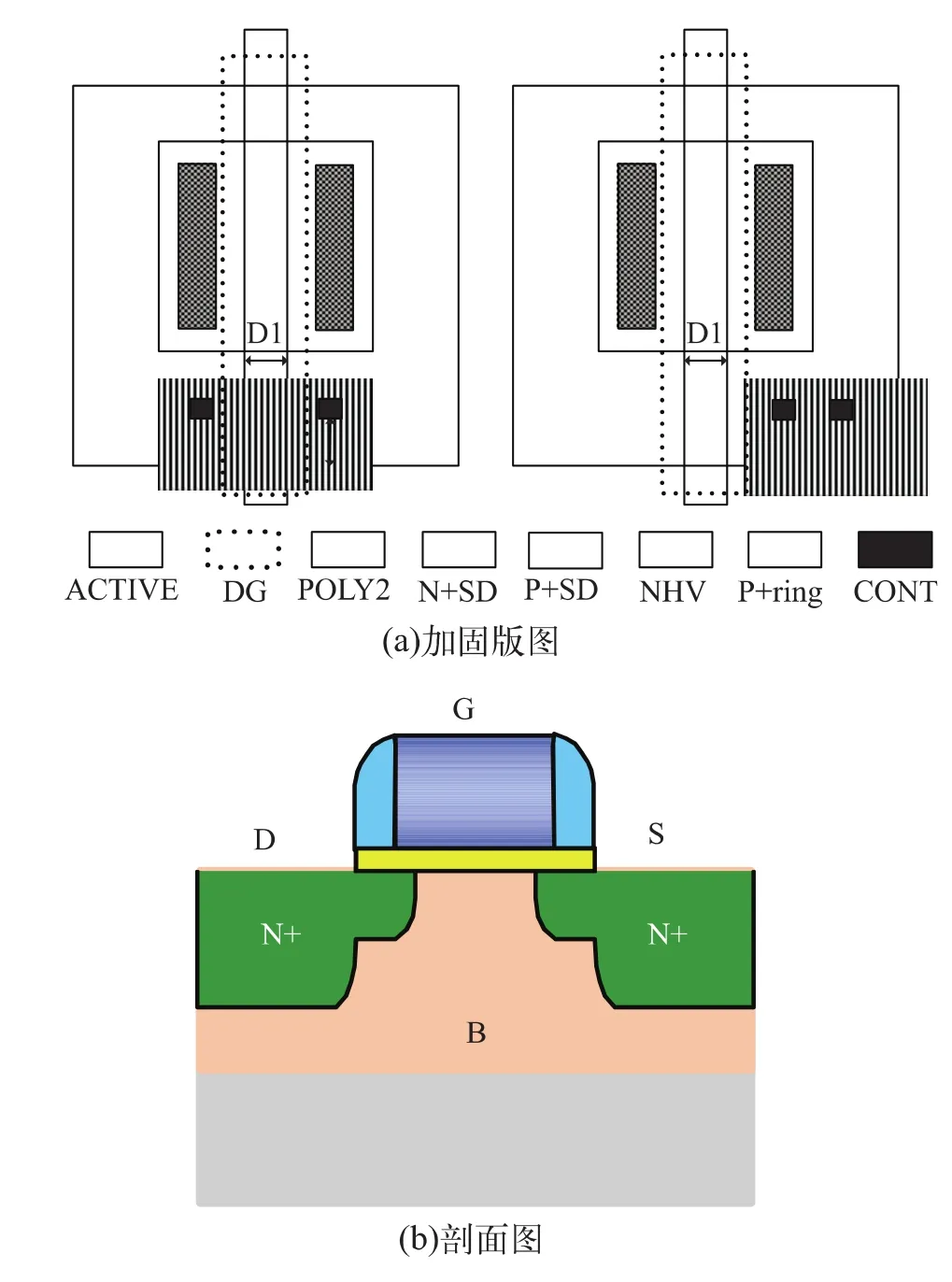

本实验LV/HVNMOS总剂量加固结构设计如图3所示。

图3 LV/HVNMOS结构示意图

2.3 辐照试验

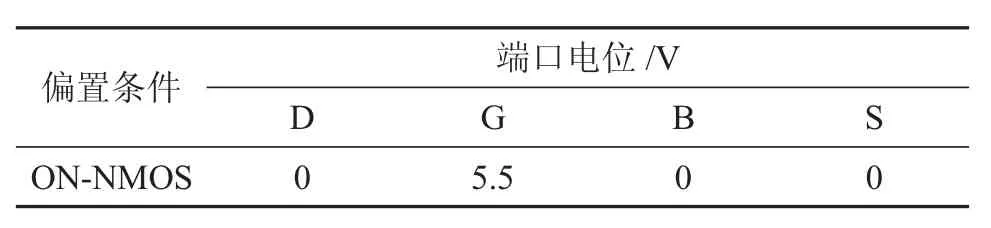

本实验采用中国科学院上海应用物理研究所钴60 γ射线源对NMOS单管器件进行总剂量辐照试验研究,剂量点 50 krad(Si)、100 krad(Si)、150 krad(Si)、500 krad(Si)、750 krad(Si),剂量率 50 krad(Si)/s,根据器件在电路中实际的工作状态,确定器件在辐照过程中的偏置电压条件,辐照过程中所施加的偏置条件如表2所示。

表2 NMOS器件辐照偏置条件

3 结果与讨论

3.1 阈值电压漂移量与总剂量的关系

通过分析MOS器件辐射效应及机理可知,导致NMOS与PMOS阈值电压的漂移主要来源于辐射对氧化层及硅界面的损伤,导致产生氧化物的陷阱电荷(Not)和界面态电荷(Nit)。TID引起MOS器件阈值电压漂移与氧化层厚度有关,其表述为:

在电离辐射作用下,氧化层中产生的载流子在电场的作用下产生漂移。电子和空穴的迁移率不同,电子很快漂移出氧化层,尽管电子漂移出氧化层时间很短(ps级),依然会在漂移过程中与空穴产生复合,因此计算氧化层中的空穴陷阱引起的阈值电压漂移,需要考虑空穴产生率f(Eox,E),其与氧化层中电场Eox和辐射射线粒子能量E有关。

3.2 LV/HVNMOS转移特性与总剂量关系

3.2.1 LVNMOS器件总剂量特性研究

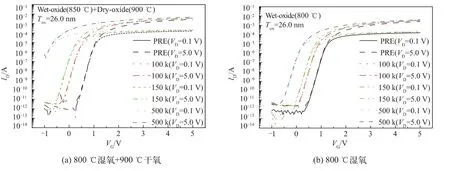

LVNMOS器件的转移特性与总剂量关系如图4所示,由转移特性可知,在500 krad(Si)条件下,LVNMOS器件场边缘均未出现漏电;同时,对于栅氧厚度小于12.5 nm的LVNMOS器件,干氧氧化、湿氧氧化方式对总剂量电离效应引起的ΔVtn影响较小,在500 krad(Si)条件下,采用湿氧氧化方式的LVNMOS比采用干氧氧化方式的阈值电压漂移ΔVtn约小0.025V。

3.2.2 HVNMOS器件总剂量特性研究

HVNMOS器件在不同辐照剂量下的转移特性曲线如图5所示。HVNMOS器件在150 krad(Si)条件下,均未出现漏电。器件总剂量电离效应Vtn差异明显,在500 krad(Si)条件下,采用800℃湿氧+900℃干氧化方式的HVNMOS器件阈值电压漂移ΔVtn比采用800℃湿氧氧化方式的高2倍左右;即当栅氧厚度为26 nm时,采用800℃湿氧氧化方式的HVNMOS器件抗总剂量效果明显优于800℃湿氧+900℃干氧。

3.3 阈值电压漂移量与总剂量关系

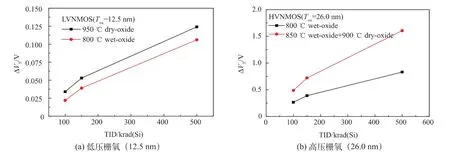

在相同偏置电压条件下(5.5 V ON偏置),高低压NMOS管的阈值电压的漂移与总剂量剂量点之间的关系如图6所示。对于LVNMOS(Tox=12.5 nm),采用湿氧氧化方式的器件其总剂量效果略优于采用干栅氧氧化方式的器件,在500 krad(Si)条件下,其阈值电压漂移约小0.025 V;对于HVNMOS器件(Tox=26.0 nm),采用800℃湿法氧化方式的HVNMOS其抗总剂量效果优于采用850℃湿氧+900℃干氧氧化的器件;在500krad(Si)条件下,其阈值电压漂移约小0.80V。

图4 LVNMOS管不同总剂量点条件下(5.5 V ON偏置)转移特性曲线

图5 HVNMOS管不同总剂量点条件下(5.5 V ON偏置)转移特性曲线

图6 不同厚度栅氧阈值电压漂移量与总剂量(5.5 V ON偏置)的关系曲线

从高压器件抗总剂量效果来看,湿法氧化栅氧明显优于干法氧化栅氧。原因主要是湿氧氧化层SiO2/Si界面的陷阱电荷转移效应。一方面,由于SiO2氧化层中内部缺陷密度Not的增加,可以增加TID电离效应引起的空穴陷阱的俘获概率;同时,在电场应力的条件下空穴向SiO2/Si界面方向迁移,易被边界陷阱(border traps or Switching states)所俘获,从而导致SiO2/Si边界E′(hole)产生积累量的增加,此过程中也会伴随着电子与空穴的复合、电子迁移与扩散等过程,但因电子迁移率远高于空穴,因此,在氧化层边界位置主要是以空穴积累为主,湿法氧化层中SiO2/Si边界E′(hole)浓度要低于干法氧化层。另一方面,干法氧化工艺Si/SiO2界面处俘获电子陷阱形成界面缺陷电荷Nit的概率远高于湿法工艺;研究结果分析,界面陷阱可以是正电性、中性或负电性的,这主要取决于费米能级和陷阱能级的位置,当费米能级位于陷阱能级之下,则陷阱显示正电性,反之则是负电性。一般而言,干法氧化工艺界面陷阱俘获电子/空穴概率比高于湿法氧化工艺。因此,对NMOS器件,干法氧化工艺Si/SiO2界面处的电子陷阱概率高于湿法氧化。对于HVNMOS器件,干氧栅氧化工艺由于电荷转移效应的影响,导致在SiO2/Si界面积累更多的边界陷阱,因此器件的总剂量效果远低于湿氧氧化工艺器件。

4 结论

本文基于抗辐射0.6 μm CMOS工艺,设计了总剂量加固结构,并采用叠栅氧工艺成功制备出了抗总剂量500 krad(Si)的高低压兼容的NMOS器件。同时,侧重研究了高低压栅氧化方式对MOS器件总剂量辐射电离效应的影响。研究发现,干、湿的氧化方式对栅氧厚度小于12.5 nm的LVNMOS器件总剂量电离效应的阈值电压漂移ΔVtn影响较小,在500 krad(Si)条件下,宽长比 20 μm/0.6 μm LVNMOS 栅氧为 12.5 nm 的湿氧比干氧总剂量效应ΔVtn小0.025 V;当栅氧厚度为26nm,其栅氧干湿氧化方式及氧化温度对HVNMOS器件的总剂量效应ΔVtn影响显著,在500 krad(Si)条件下,850℃湿氧+900℃干氧比800℃湿氧的总剂量效应ΔVtn高约2倍,其总剂量效应ΔVtn性能的优异性主要归因于湿氧氧化层SiO2/Si界面的陷阱电荷转移效应。

[1]刘文平.硅半导体器件辐射效应及加固技术[M].北京:科学出版社,2013.

[2]曹建中.半导体材料的辐射效应[M].北京:科学出版社,1993.

[3]RSJames.RadiationEffectsinMOSOxides[J].IEEEtransactions on nuclear science,2008,55(4).

[4]M R Shaneyfelt,J R Schwank,D M Fleetwood,P S Winokur,K L Hughes,G L Hash and M P Connors.Inerface-trap buildup rates in wet and dry oxides[J].IEEE transactions on nuclear science,1992,39(6):2244-2251.

[5]D M Fleetwood,S L Miler,R A Reber,Jr,P J McWhorter,P S Winokur,M R Shaneyfelt,and J R Schwank.New insights into radiation-induced oxide-trap charge through thermally-stimulated-current measurement and analysis[J].IEEE transactionson nuclearscience,1992,39(6):2192-2202.

[6]H J Barnaby.Total-ionizing-dose effects in modern CMOS technologies[J].IEEE transactions on nuclear science,2006,53(6):3103-3121.

[7]T R Oldham.Total ionizing dose effects in MOS oxides and devices[J].IEEE transactions on nuclear science,2003,50(3):481-499.

[8]C J Nicklaw,Z Y Lu,D M Fleetwood,R D Schrimpf,S T Pantelides.The structure,properties,and dynamics of oxygen vacanciesin amorphousSiO2[J].IEEE transactions on nuclear science,2002,49(6):2667-2673.

刘佰清(1989—),男,南京大学物理电子学硕士,2014年7月进入中国电子科技集团公司第五十八研究所工作,主要负责抗辐射工艺集成技术开发。

The Effect of Oxidation Methods on TID Radiation

LIU Baiqing,LIU Guozhu,WU Jianwei,HONG Gensheng,ZHENG Ruocheng

(China Electronics Technology Corporation No.58 Research Institute,Wuxi 214035,China)

The radiation ionization of total dose(TID)of the LV/HVNMOS based on the CMOS standard process has been analysed.For the LVNMOS witch the gate oxide thickness less than 12.5 nm,it is found that the dryandwetoxidationmethodshave little effect about the threshold voltage drift(ΔVtn)due to the TID effect.Under the condition of 500 krad(Si),the ΔVtnof the device prepared by the wet-oxidation process is 0.025 V less thanthe device thatpreparedbydry-oxidationprocess.For the HVNMOS device which the gate oxide thickness was 26 nm,the effect of the oxidation process and the oxidation temperature due to the TID was significant.Under the condition of 500K rad(Si),the threshold voltage drift(ΔVtn)due to the TID effect which prepared by the dry-oxidation process(900℃)was about 3 times higher than the wet-oxidation process.The superiority of the TIDeffect ΔVtnismainlyattributedtothe charge transfer effectofSiO2/Siinterface trap.

gate oxide process;TID;thresholdvoltage drift ΔVtn

TN306

A

1681-1070(2017)11-0044-05

2017-06-27