应用于高压接口电路的SCR ESD保护研究

曹燕杰,王燕婷

(中国电子科技集团公司第五十八研究所,江苏无锡 214072)

应用于高压接口电路的SCR ESD保护研究

曹燕杰,王燕婷

(中国电子科技集团公司第五十八研究所,江苏无锡 214072)

SCR是ESD保护器件中最具有面积优势的一种。提出一种应用于高压接口电路的SCR ESD保护结构,同时避免了发生闩锁的风险。采用0.5 μm BCD工艺设计,可达8000 V人体模型ESD能力,其维持电压可以达到28 V以上。

SCR;BCD;闩锁;ESD

1 引言

ESD(Electro-Static Discharge)对芯片设计者来说是一个主要的可靠性问题。客户反馈的失效电路中,有相当一部份和ESD损伤有关。为了防止电路的ESD损伤,芯片的I/O端口和电源-地之间都必须放入ESD保护电路。然而,加入的ESD保护电路可能会影响到电路的功能和参数,或者I/O端口的电路(如缓冲器)也可能会降低ESD保护电路的能力。因此,ESD保护电路需要有效地保护I/O端口的电路以及芯片内部的电路。

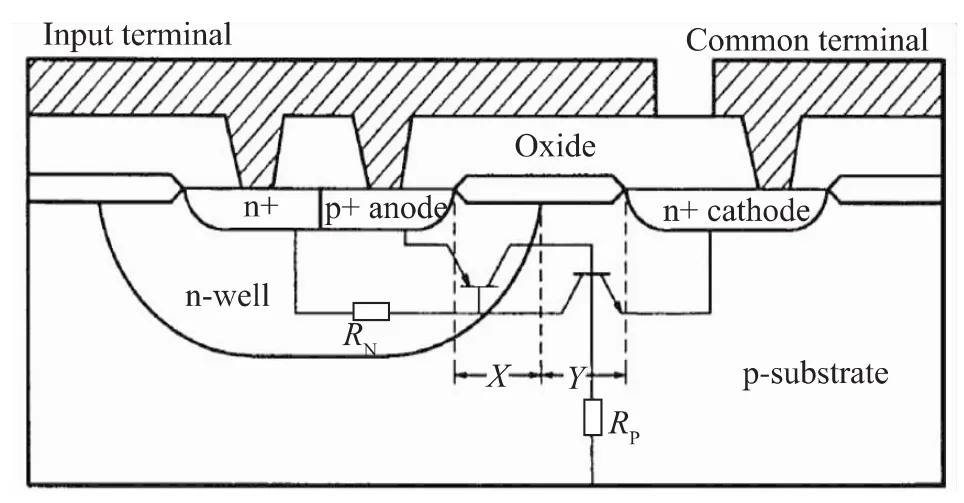

从单位面积的ESD能力看,SCR是目前最有效的ESD保护器件[1]。SCR是一种pnpn器件,如图1所示,通常被叫做横向SCR或LSCR。LSCR的工作原理如下:在n-well中相邻的n+、p+扩散区连接输入端(input terminal),一个纵向pnp器件是由p-substrate作为集电区,n-well作为基区,连接输入端的p+扩散区作为发射区。在p-substrate中的n+扩散区连接到地或衬底,作为npn器件的发射区,npn的基区和集电区分别由p-substrate、n-well组成。当ESD正脉冲来临时,npn的集电结首先发生雪崩击穿,在n-well中产生电流让pnp的发射结正偏,pnp在小于1 ns内导通,最终导致SCR导通[2]。一旦SCR开启,处于低阻状态,阳极-阴极间的钳位电压约为1~2 V。这就是SCR器件ESD性能优越的原因。由于SCR器件对salicide工艺不敏感,因此它在先进的CMOS工艺里也很有优势。

2 可控硅(SCR)器件的关键参数优化

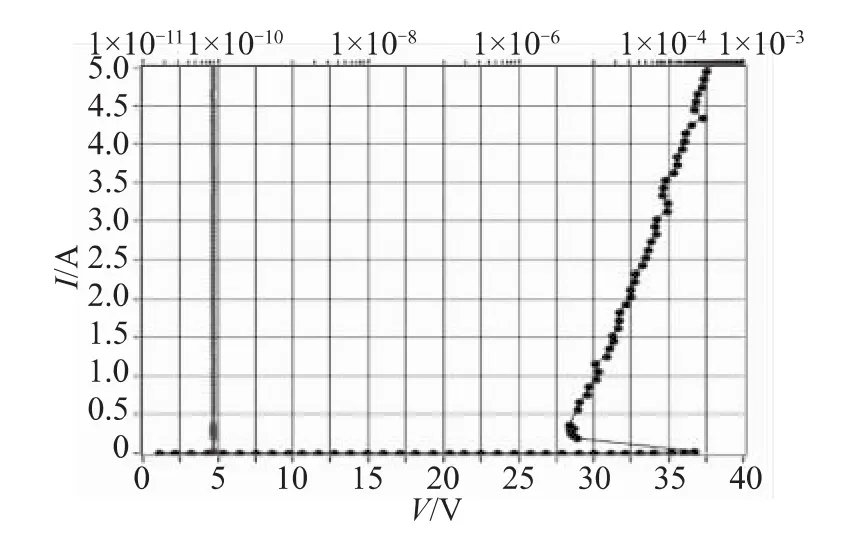

由引言中分析的SCR的触发机理可知,SCR的触发电压由n-well/p-substrate的击穿电压和衬底电阻Rp决定。在常规的CMOS工艺中,该击穿电压约为40~60 V。由于触发电压过高,难于保护输出缓冲器中的NMOS管。为了降低SCR的触发电压,采用在n-well边界处插入n+扩散区,修改后的LSCR(MLSCR)的 I-V特性见图 2。1.6 μm CMOS工艺MLSCR的触发电压可以降到20~25 V,而先进的CMOS工艺中MLSCR的触发电压可达10~12 V[3]。

图1 横向SCR截面图

图2 MLSCR的I-V特性

另外一个关键参数衬底电阻Rp是由衬底浓度决定的。尤其当使用外延衬底时,外延厚度越厚,SCR的ESD性能越好。当在先进工艺中,为了降低芯片的latch-up风险采用较薄的外延,使得衬底电阻Rp很小,导致LSCR中的npn难以触发。因而外延层的厚度需要在latch-up和ESD性能间折中考虑。

3 应用的需求

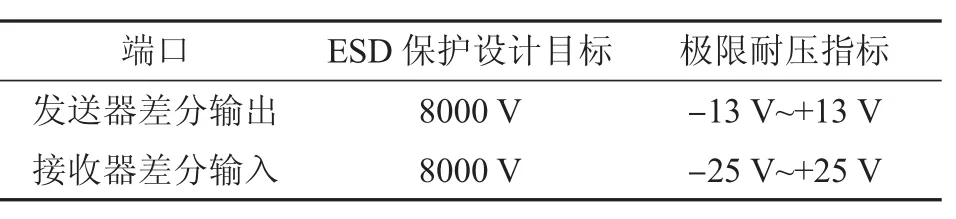

以RS-232接口电路为例,发送器的差分输出端口极限电压为-13 V~+13 V,RS-232接收器的输入端口极限电压为-25 V~+25 V,见表1。常规的LSCR ESD保护是存在对地的寄生二极管,这种结构会把负压输入信号嵌位在-0.3 V左右,不能满足-25 V~+25 V的电压输入信号,因此ESD结构的设计非常有难度,需要重新设计器件。

表1 RS-232端口ESD设计目标和极限耐压指标

4 器件的优化

为了满足实际的应用需求,需要对现有的LSCR加以改进才能满足,本文主要对以下两点做出改进:

(1)提高MLSCR的维持电压,从现有的1~2 V提高到25 V以上。

(2)在端口上存在负电压时,消除端口对地的钳位二极管。

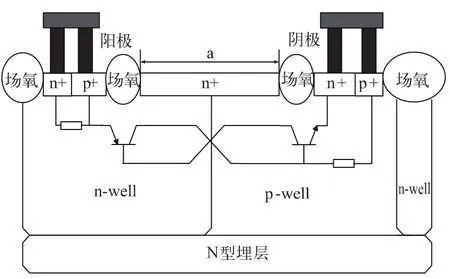

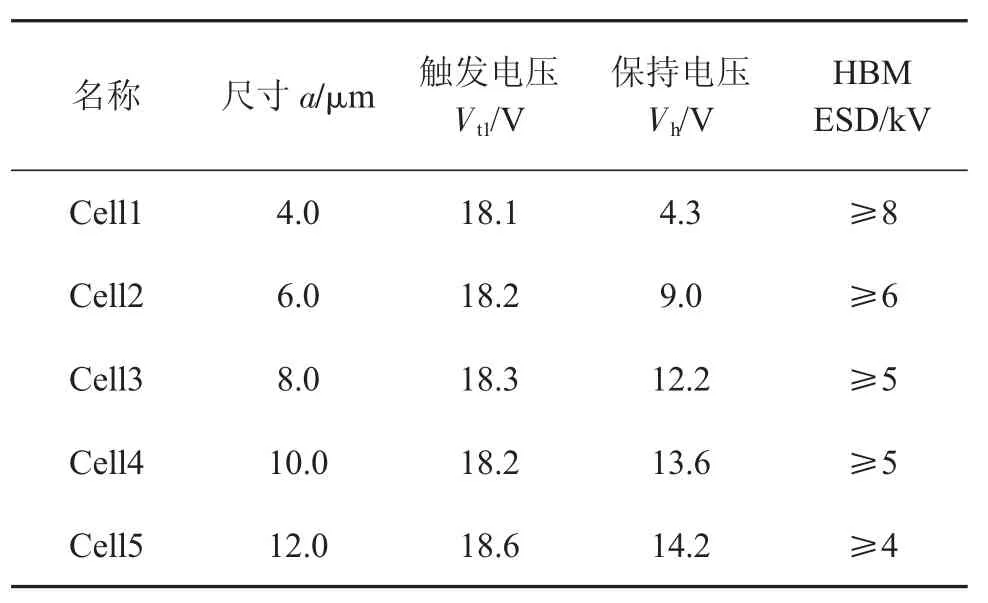

选用国内商用0.5 μm 2P2M BCD工艺,首先在MLSCR的基础上进行改进,通过调整图3中的尺寸a,提高SCR保持电压Vh。其中器件宽度100 μm。经流片后测试,TLP和ESD结果见表2。TLP结果显示,随着尺寸a的增加,器件的保持电压增加,在a≥8 μm时保持电压基本保持稳定并略有增加。根据ESD测试结果,随着保持电压的增加,器件的ESD能力在下降。从功耗角度分析,在相同的电流下,随着器件保持电压的增加,器件的功耗增加,导致了器件ESD能力的下降。

图3 改进的MLSCR剖面图

表2 HHVSCR尺寸a与ESD特性关系表

除此之外,可以采用MLSCR串联的方式提升维持电压,串联的MLSCR电路图见图4。选择尺寸a=10 μm的器件,器件宽度优化为200 μm,经流片验证,维持电压可达28 V,触发电压可达37 V,其TLP扫描曲线如图5所示。经人体模型ESD打击,通过8kV的测试。

图4 串联的MLSCR剖面图

图5 串联的MLSCR TLP曲线

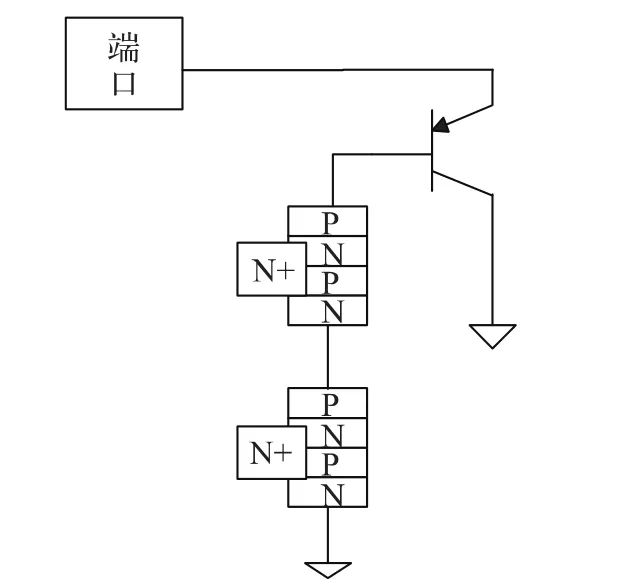

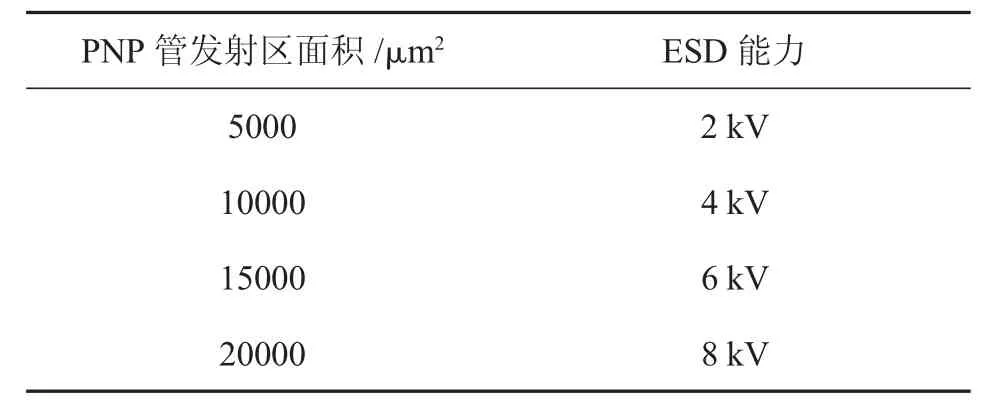

为了满足第二点的要求,消除端口对地的钳位二极管,对端口结构改进为如图6所示。增加了PNP三极管后,ESD正脉冲打击的特性基本没有变,相比原结构触发电压和保持电压增加1~2 V,人体模型ESD能力达到8 kV以上。但ESD负脉冲的特性需要进一步优化。首选选择P+/P-/NW耐压约30 V的PNP器件,通过调整PNP器件的发射区面积,得到如表3所示的ESD负脉冲测试结果。当PNP器件发射区面积达到20000 μm2时,负脉冲的ESD能力达到8 kV。

图6 PNP和串联的MLSCR组合结构

图7 新结构的TLP扫描正向特性

表3 PNP器件的发射区面积与ESD特性的关系

5 总结

本文提出一种新颖的SCR ESD保护结构,用于耐高压的接口电路,并且避免了发生闩锁的风险。采用0.5 μm BCD工艺设计,经验证可达8 kV人体模型ESD能力,其维持电压可以达到28 V以上。

[1]Ajith Amerasekera,Charvaka Duvvury.ESD in Silicon Intergrated Circuits[M].second edition.JOHN WILEYamp;SONS,LTD.

[2]R Rountree,C Duvvury,T Maki,H Stiegler.A processtolerantinputprotection circuitforadvanced CMOS processes[C].Proc 10thEOS/ESD Symposium,1988:201-211.

[3]A Chatterjee,T Polgreen.A low-voltage triggering SCR for on-chip protection at output and input pads[J].Elec Dev Lett,1991,EDL-12,21-22.

曹燕杰(1983—),女,江苏宜兴人,本科,现在中国电子科技集团公司第五十八研究所从事集成电路版图设计工作。

SCR Structure for High-Voltage Interface′s ESD Protection in BCD Process

CAO Yanjie,WANG Yanting

(China Electronics Technology Corporation No.58 Research Institute,Wuxi 214072,China)

The SCR is the most efficient of all protection devices in terms of ESD performance per unit area.A high holding-voltage SCR (HHVSCR)ESD protection structure is proposed for traditional I/O port without latch-up risk.The HHVSCR device has been practically used to protect RS-232 tranceiver with a 8 kV HBM ESDrobustnessina standard0.5 μm BCDtechnologywithoutextra processmodification.

SCR;BCD;latchup;ESD

TN303

A

1681-1070(2017)11-0030-03

2017-08-15