FPGA上电复位过程的存储单元读写检测方法

耿 杨,谢 杰,徐玉婷,张胜广

(1.无锡中微亿芯有限公司,江苏无锡 214072;2.中国电子科技集团公司第五十八研究所,江苏无锡 214072)

FPGA上电复位过程的存储单元读写检测方法

耿 杨1,谢 杰2,徐玉婷1,张胜广2

(1.无锡中微亿芯有限公司,江苏无锡 214072;2.中国电子科技集团公司第五十八研究所,江苏无锡 214072)

基于FPGA技术,提出了一种关于FPGA上电复位过程的存储单元读写检测方法。该方法能够在FPGA上电复位的过程中较早地检测出芯片中心的控制电路和若干级buffer的驱动能力是否足以控制所有存储单元的读写。

FPGA;SRAM;寄存器上电复位

1 引言

FPGA里分布着大量的存储单元,这些存储单元的读写是由位于芯片中心的控制电路经过若干级buffer控制的[1],由于驱动能力的问题,离芯片中心比较远的存储单元容易发生读写失误,导致芯片不能正常工作[2]。所以如何能够在FPGA上电复位的过程中较早地检测芯片中心的控制电路和若干级buffer的驱动能力是否足以控制所有存储单元的读写是本论文需要解决的问题。

2 设计方法与实现

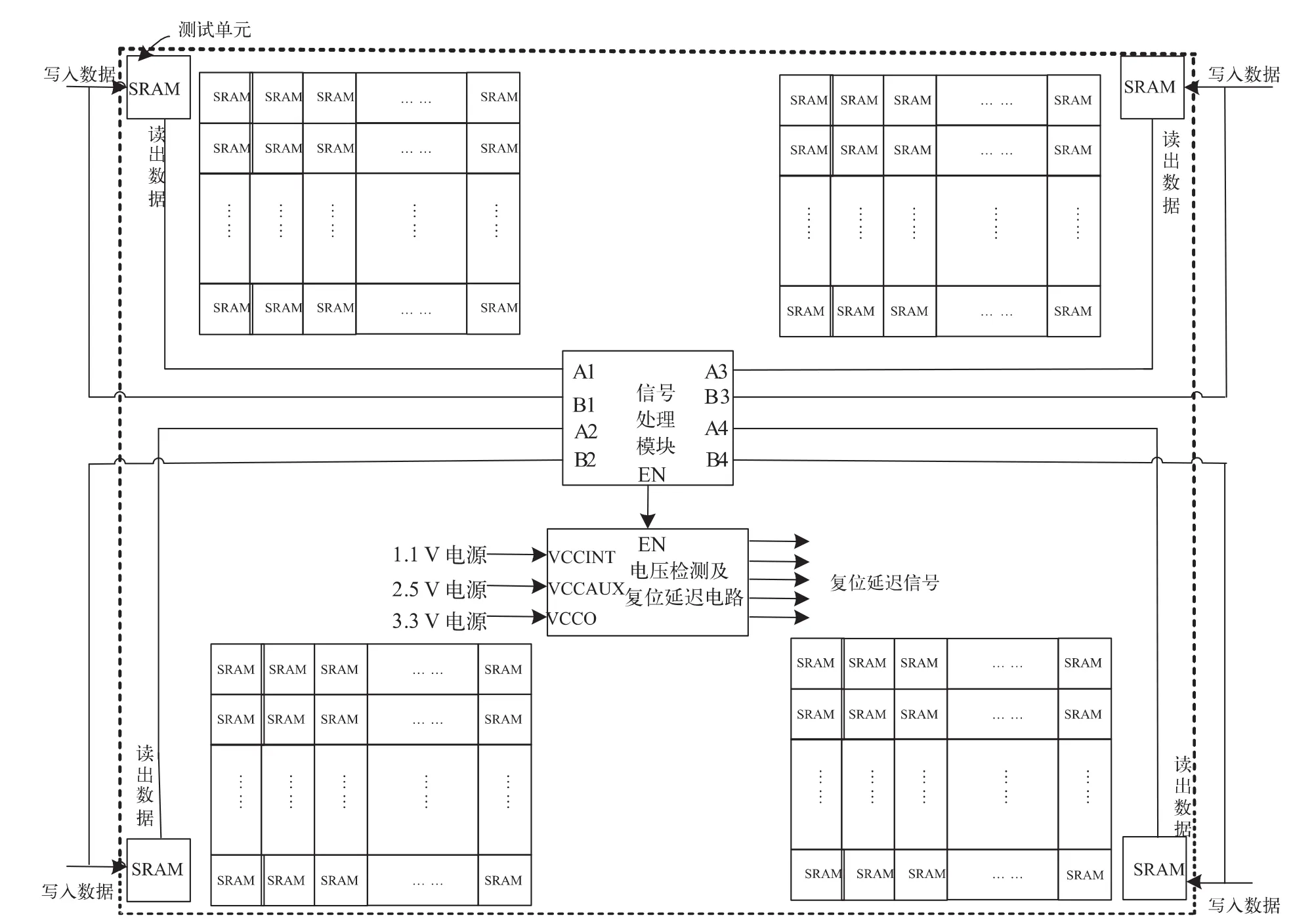

如图1所示,本论文设计的系统在FPGA芯片的左上、左下、右上、右下4个角各额外放置一个测试存储单元,由于驱动能力的问题,离芯片中心比较远的存储单元容易发生读写失误,当这4个测试存储单元SRAM(图2)都读写正常,说明所有的存储单元在后期配置[3]过程中都能正常读写。

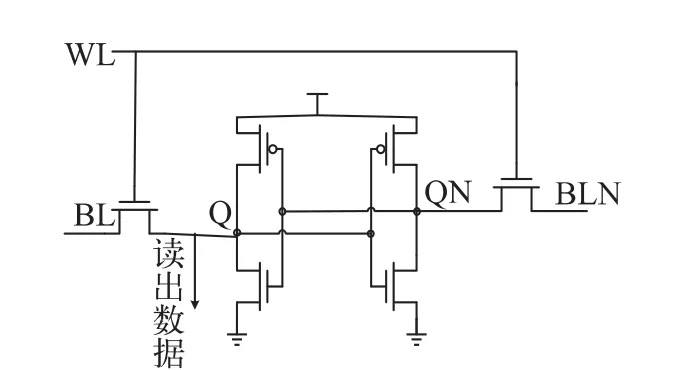

测试存储单元SRAM电路的工作原理如下。

写操作:写“1”时,位线BL为高电平,BLN为低电平,字线 WL为高,传输管打开,Q1点存“1”,Q2点存“0”;写“0”时,反之。

保持状态:字线WL为低电平,传输管关闭,一对互补位线BL、BLN为高电平,由于中间是一对互相耦合的反相器,使得存储的数据能够得以保持。

读操作:字线WL为低,传输管关闭,直接从Q端读出存储数据即可。

图1 FPGA上电复位过程的存储单元读写检测系统

图2 测试存储单元SRAM电路

具体步骤如下:

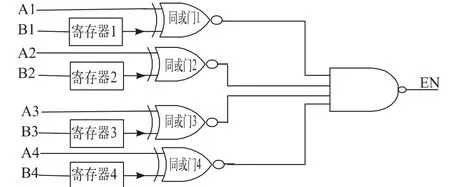

当位于芯片左上、左下、右上、右下4个区域的测试存储单元(见图2)SRAM[2]写入数据的同时信号处理模块(图3)中对应的寄存器会记录写入的数据,测试存储单元SRAM读出的数据和寄存器寄存的数据由对应的同或门进行比较,若二者数据相同则输出为“1”,不同则输出为“0”。

图3 信号处理模块电路

4个同或门的输出信号经过一个四输入与非门,若4个同或门全部为“1”(即4个方位上的测试SRAM全部读写正常)则四输入与非门输出信号EN为“0”。若4个同或门有任意一个为“0”时说明4个方位上的测试SRAM有读写失误的情况发生,四输入与非门输出信号EN为“1”,并发送到电压检测及复位延迟电路(图4)中的二输入与非门。

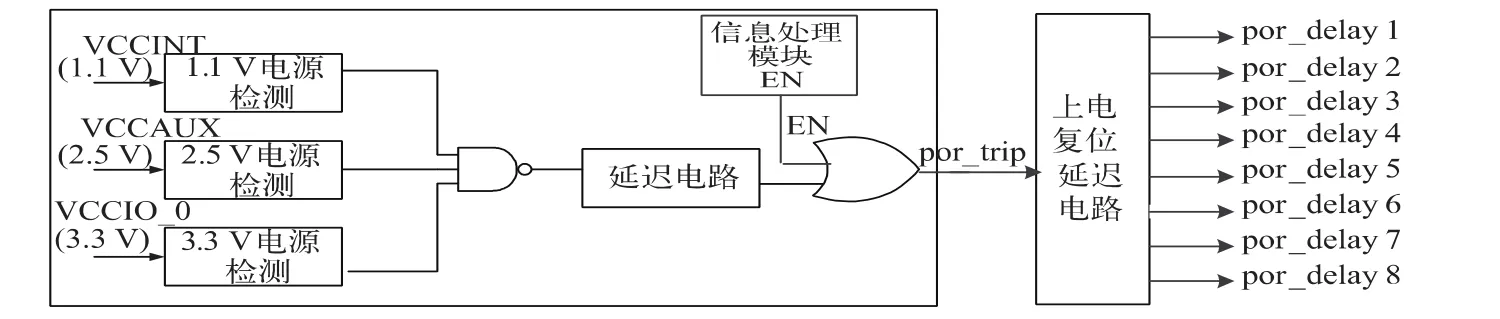

上电复位延迟电路如图5所示,由若干个D触发器串联组成。D触发器的个数可以决定上电复位延迟电路的延迟时间。假设2个复位信号分别对应的2个触发器距外界提供时钟的第一个触发器之间的触发器个数分别为N和M,外界提供的时钟周期为T,那这两个复位信号的延迟时间差为T×(2N-2M)。当上电复位信号por_trip为“0”时D触发器开始工作,上电复位延迟电路产生一系列不同顺序的复位信号,控制整个芯片不同模块的上电顺序。

如图4所示,电压检测及复位延迟电路中的3组电压上电检测电路正常上电三输入与非门输出“0”,经过一些延迟模块输入到二输入的或门,信号处理模块的输出信号EN也输入到二输入的或门并产生一个上电复位信号por_trip,当信号处理模块的输出信号EN 为“0”时,por_trip 为“0”,上电复位延迟电路正常工作,产生一系列不同顺序的复位信号,说明整个FPGA芯片的存储单元都不会由于驱动能力问题而导致不能够正常读写。当4个方位的测试SRAM出现读写失误时,信号处理模块的输出信号EN为“1”时,por_trip为“1”,上电复位延迟电路不能工作,输出没有达到预期的跳变,整个电路复位失败。

图4 电压检测及复位延迟电路

图5 上电复位延迟电路

3 仿真验证

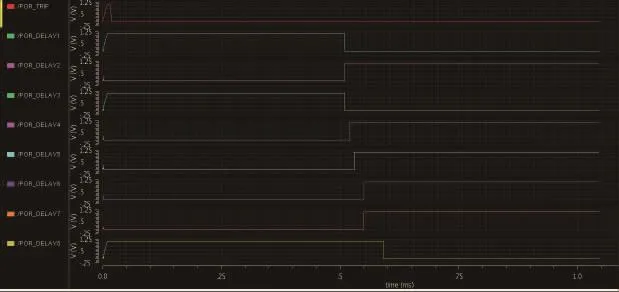

整个设计基于SMIC 65 nm工艺,建立整个仿真验证环境,利用Cadence公司仿真工具Spectre进行设计仿真验证。图6是当T=10 ns时上电复位延迟电路正常工作,电路复位正常时的仿真波形图。

图6 电路复位正常时的仿真波形图

图7是对图6的各个复位延迟信号的仿真波形结果进行的数据处理,可以看到各个复位信号的时间差符合上文提到的D触发器的个数可以决定上电复位延迟电路的延迟时间公式。

图7 各个复位信号的时间差

4 总结

本文提出了一种关于FPGA上电复位过程的存储单元读写检测方法,该设计能够在FPGA上电复位的过程中较早地检测芯片中心的控制电路和若干级buffer的驱动能力是否足以控制所有存储单元的读写。

[1]徐志军,徐光辉.CPLD/FPGA的开发与应用[M].北京:电子工业出版社,2002.

[2]张勇国,唐玉兰,等.FPGA高性能查找表的设计与实现[J].固体电子学研究与进展,2009.

[3]Singh S,Rose J,Chow Petal.The Effect of Logic BLOCK Architecture on FPGA performance[J].IEEE JSSC,1992,27(3):281-287.

耿 杨(1987—),女,河北辛集人,硕士,工程师,研究方向为千万门级FPGA设计。

A Method of Reading and Writing of Memory Cells in the Process of Power Reset on FPGA

GENG Yang1,XIE Jie2,XU Yuting1,ZHANG Shengguang2

(1.East Technologies,inc.Wuxi 214072,China;2.China Electronics Technology Corporation No.58 Research Institute,Wuxi 214072,China)

Based on FPGA,the paper presents a method of reading and writing of memory cells in the process of power reset on FPGA.In the process of power reset on FPGA,the method can early detect the center of the chip control circuit and a number of buffer driver ability which is enough to control all of the memory cells readingandwriting.

FPGA;SRAM;register poweronreset

TN402

A

1681-1070(2017)11-0033-03

2017-04-26