基于ZYNQ的涡流无损检测阻抗分解算法的实现

彭乐锋,刘 康,刘 继

(同济大学铁道与城市轨道交通研究院,上海201800)

基于ZYNQ的涡流无损检测阻抗分解算法的实现

彭乐锋,刘 康,刘 继

(同济大学铁道与城市轨道交通研究院,上海201800)

涡流无损检测技术在近年来取得了很大的发展,在工业检测领域有着重要的应用。在涡流检测系统的设计中,最为关键的是对缺陷信号进行提取。目前绝大多数涡流仪器都是基于阻抗分解技术进行缺陷信号的特征提取。在对特征提取技术的原理和实现方法进行了简要阐述的基础上,分析了模拟电路、DSP和传统FPGA实现的不足,提出了在ZYNQ平台上实现该算法的方案。该方案利用了ZYNQ平台的优势,使用软硬件协同设计和IP集成的设计思想,实现快速开发。利用ZYNQ片内互联总线,实现了动态参数可调。采用该方案实现的阻抗分解算法能够降低实现难度,且能够达到显著的缺陷提取效果。

涡流无损检测;ZYNQ平台;阻抗分解;软硬件协同设计;数字信号处理

1 引言

涡流检测技术作为一种重要的无损检测技术,近年来取得了很大的发展。由于其具有灵敏度高、易于实现自动化、检测效率高等优点,在工业无损检测中扮演着重要的角色[1]。在涡流检测技术中,关键的环节是提取检测信号中的缺陷特征信号。因此,对检测信号的特征提取理论和实现方法进行研究具有重要的意义。

目前,绝大多数的涡流检测仪器都是基于阻抗分解算法来实现缺陷提取的。传统的方法是使用电路处理模拟信号来完成,这一方法的缺点是电路设计复杂且易受噪声信号的干扰,测量精度比较低,适用范围较窄[2]。因此,近年来很多研究者从数字信号的角度来实现该算法,比如在DSP等微控制器平台上实现。但是由于这些平台是串行执行指令,因此,在处理大批量的数据时,会导致CPU负载过高,处理速度慢[3]。还有研究者为了提高处理速度,提出用FPGA来实现。但是由于需要使用硬件描述语言来实现整个算法的数据处理和数据流的控制,因此,实现难度较大[4]。经过对比,提出了一种在Xilinx公司的ZYNQ平台上从数字信号处理的角度实现阻抗分解算法的方案。该方案结合ZYNQ的优势和软硬件协同设计的方法,相比DSP实现而言,其处理速度高。相比传统FPGA的实现而言,其编程难度低,开发速度快,可灵活设置参数,同时具有很好的缺陷提取效果。

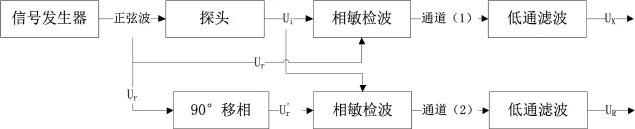

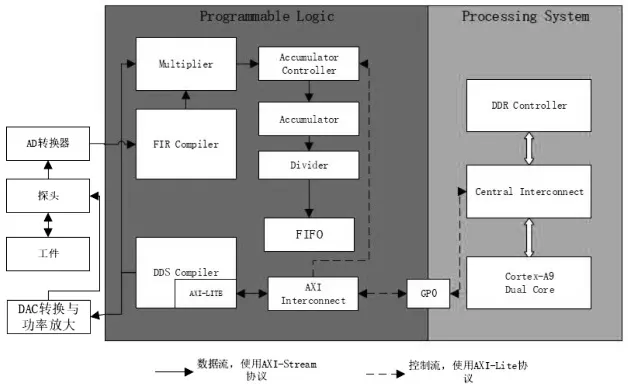

图1 阻抗分解原理框图

2 阻抗分解

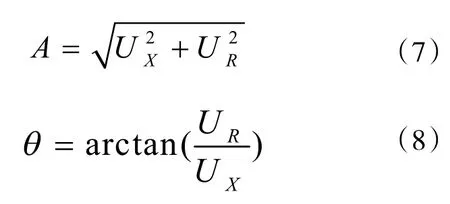

涡流检测线圈的阻抗值是一个矢量,可分解为相互垂直的电阻分量和感抗分量,如公式(1)所示:

采用阻抗分解法,根据阻抗信号反演被测工件上缺陷的形状和位置,需要将检测线圈的阻抗信号进行正交分解,得到电阻分量和感抗分量。阻抗信号分解的原理框图如图1所示。

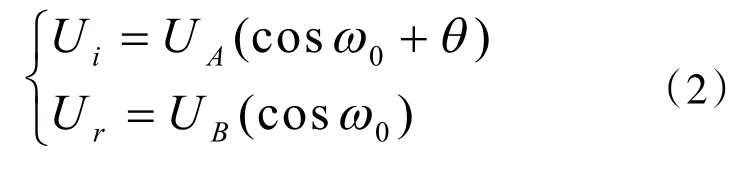

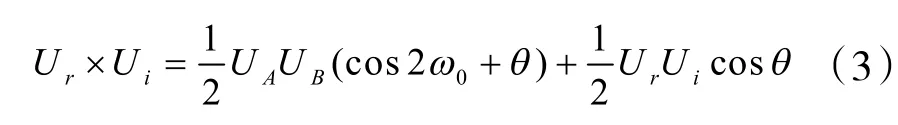

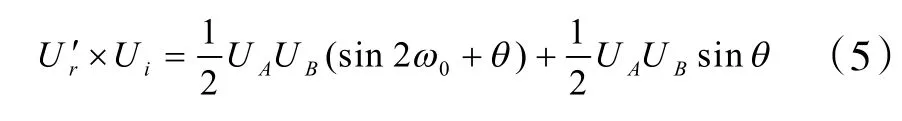

图1中信号发生器产生正弦信号激励探头,从探头返回的被测对象的阻抗信号为用来激励探头的正弦信号又作为后续相敏检波的一路参考信号,同时经过90°移相后形成另一路参考信号相敏检波电路的作用是将参考信号和阻抗信号完成乘法运算,从而得到和频信号与差频信号,利用低通滤波滤除和频信号即可得到所要的差频信号。与是频率相同的正弦波时,计算公式如(2)所示:

通道(1)进行的运算如公式(3)所示:

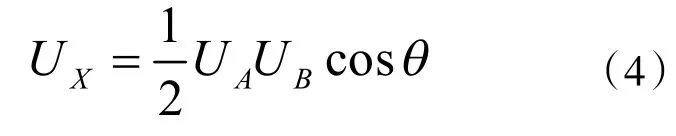

经过低通滤波滤除高频分量后即可得到直流分量,如公式(4)所示:

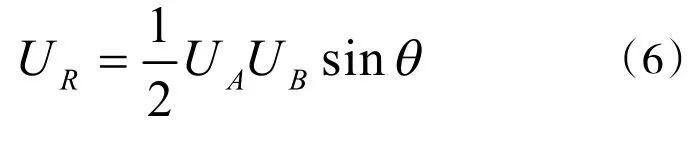

经过低通滤波滤除高频分量后即可得到直流分量,如公式(6)所示:

3 ZYNQ平台介绍

3.1 ZYNQ介绍

ZYNQ是Xilinx公司推出的高性能和低功耗的可扩展处理器平台,每个ZYNQ系列的单芯片内都集成了ARM Cortex-A9系列处理器系统(Processor System,PS)和Xilinx可编程逻辑(Programmable Logic,PL),并且PS中集成了内存控制器,外部存储器DDR控制模块及大量的外设。PS配有AMBA开放总线互联端口,可以通过AXI片内高速总线互联和PL通信,带宽速度高达100Gbps[5]。

3.2 AXI总线协议的介绍

AXI(Advanced eXtensible Interface)是一种总线协议,是ARM公司提出的AMBA(Advanced Microcontroller Bus Architecture)3.0协议最重要的部分,是一种面向高性能、高带宽、低延迟的片内总线[6]。AXI互联和接口在PS和PL之间形成桥梁,把PS和PL两者协同起来形成集成的系统。AXI总线分为三种类型:

1、AXI4—用于存储映射链接,它支持最高的性能:通过一簇高达256个数据字的数据传输来给定一个地址。

2、AXI4-Lite—一种简化了的链接,只支持每次连接传输一个数据(非批量)。AXI4 Lite也是存储映射的:这种协议下每次传输一个地址和单个数据。

3、AXI4-Stream—用于高速流数据,支持批量传输无限大小的数据。没有地址机制,这种总线类型最适合源和目的地之间的直接数据流。

因此,需要根据数据的形式选择合适的AXI总线类型。算法数据传输采用AXI-Stream协议,能够实现高速的传输。而控制接口采用AXI-Lite协议,用来实现PS端对PL端的参数配置。

3.3 软硬件协同设计的方法介绍

Xilinx为了适应系统的快速开发,推出了Vivado系统集成开发工具,提出了基于软硬件协同设计的方法。设计者根据系统各个功能模块的性能和资源需求,进行软硬件的划分。比如将运算量大的部分划分成硬件实现,即在PL端用FPGA实现,将控制部分划分成软件实现,即在PS端用C语言编程实现。同时,设计者可以使用Xilinx提供的IP核来实现算法,并且可以自定义IP核,利用AXI总线来进行封装,跟PS端实现通信。由于具有以上优点,因此基于ZYNQ平台的设计方法可以降低算法的实现难度,缩短设计时间[7]。

4 阻抗分解算法的ZYNQ实现

在图1可以看到,阻抗分解算法分为两部分,分别为相敏检波和低通滤波。本文使用数字相敏检波和由累加平均实现的低通滤波。ZYNQ平台中的阻抗分解的实现架构如图2所示。从图2可以看出,信号从探头返回后直接进入AD转换器,转换成数字信号,进入ZYNQ进行阻抗分解算法的处理。

图2 ZYNQ平台阻抗分解的实现架构

4.1 数字相敏检波的实现

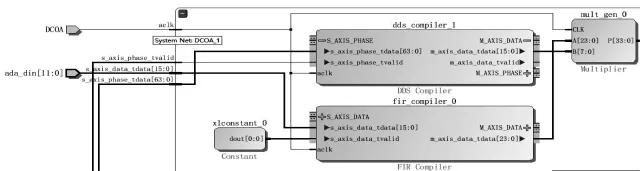

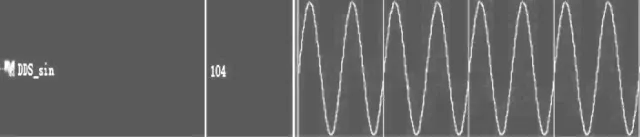

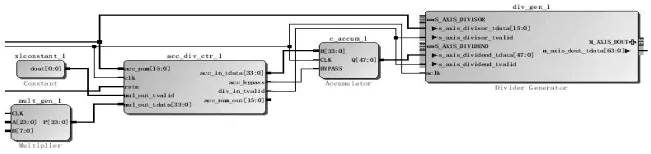

数字相敏检波是将探头回来的信号直接通过模数转换,然后与ZYNQ内部用DDS产生的两路参考信号相乘。课题采用12位AD芯片,采样频率为50MHz,探头的激励信号频率为50kHz到5MHz。为了滤除信号中的高频噪声,改善信号的质量,因此在算法通路的起点加入一个截止频率为5MHz的FIR低通滤波器,使用窗函数设计方法,采用汉明窗,得到滤波器为51阶[8]。在数字相敏检波的实现中,使用了基于IP核的设计方法,利用官方提供的IP核与自定义的IP核组成算法通路。DDS、FIR滤波器、乘法器、均使用Xilinx官方提供的IP核,上述IP核只需根据算法的参数进行配置即可,IP核的数据接口都采用AXI-Stream接口。算法运行的时钟为AD芯片输出的数据时钟DCOA,AD芯片输出的数据为ada_din[11:0],通过PL端的引脚引入到ZYNQ。从图1可以知道,通道1和2的区别在于参考信号的不同。下面给出数字相敏检波算法通道1的IP核连接,如图3所示。在调试时加入嵌入式逻辑分析仪可以实现在线抓取数据的功能,可以看到DDS输出的正弦信号,如图4所示。

图3 数字相敏检波算法通道1的IP核连接

图4 逻辑分析仪抓取的DDS正弦信号

4.2 低通滤波的累加平均实现

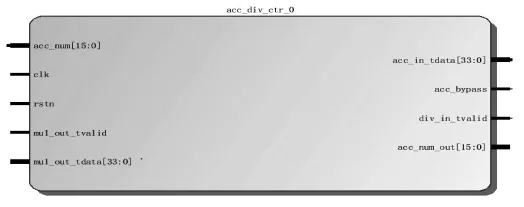

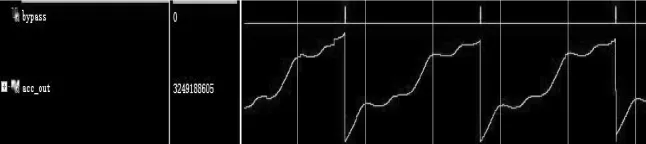

由式(3)可知,相乘后结果里含有一个倍频的高频分量,要将这个分量去除,传统方法是使用数字滤波器来完成。信号频率为50kHz时,则其倍频分量为100kHz,因此需要设计一个截止频率为50kHz,采样频率为50MHz的低通滤波器。本文使用Kaiser窗函数法来设计,得到滤波器的阶数高达50185。这是由于采样频率太高,目标截止频率太低,从而过渡带太窄导致的。因此,使用数字滤波器来完成低通滤波,会极大地消耗系统资源和降低系统的实时性。由于倍频分量是一个正弦信号,因此,根据正弦整周期内积分为零的特点,按照整周期累加的方法可以消除这个倍频分量。同时,由于特征信号为直流信号,从而会得到加强,为了还原真实数值,还需要除以倍频信号整周期内的点数。此外,当累加器累加多个周期时,还可以实现缺陷信号的平滑滤波作用和抽取作用。Xilinx官方提供了累加器和除法器的IP核。但是,累加器需要实现累加到上限值时重新从当前输入的数据重新开始累加这个功能,因此需要使能IP核的bypass信号,用来将当前输入直接输出到结果。同时需要自定义一个IP,名为Accumulator Controller,用来同步数据的控制和产生bypass信号,如图5所示。累加器上限值计算公式如式(9)所示:

式(9)中Fs是 系统的采样频率, Fsig是探头的激励频率。累加器的上限值由PS端计算后,通过AXI-Lite总线传输到acc_num接口。累加平均算法的IP核连接如图6所示。使用嵌入式逻辑分析仪抓取自定义IP的输出bypass和累加器的输出,如图7所示,可以看到程序工作正常,实现了累加功能。

图5 自定义的累加器控制IP核

图6 累加平均算法的IP核连接

图7 逻辑分析仪抓取的累加器输出和bypass信号

5 算法处理效果分析

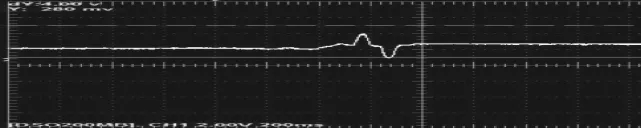

为了验证算法的有效性,需要与实验室原有的模拟阻抗分解电路的输出进行比较。实验条件时探头的激励信号频率为100kHz,发射档位为1档,前置放大增益为9dB,以0.1m/s的速度经过一个铁棒上的宽0.3mm,深0.1mm,长10mm的缺陷。采集到的UX分量如图8所示。

图8 模拟电路实现的阻抗分解算法提取的Ux分量

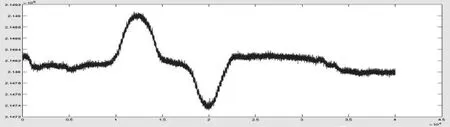

在同样的实验条件下,使用ZYNQ平台实现的阻抗分解算法来提取UX信号,将结果保存成文本,导入到Matlab中查看,如图9所示。可以看到,得到的缺陷波形与模拟电路实现时得到的一致,证明了此算法的有效性。

图9 ZYNQ平台实现的阻抗分解算法提取的Ux分量

6 结束语

在阐述涡流无损检测中阻抗分解算法的原理基础上,分析了该算法的模拟电路实现和DSP实现的缺点。更进一步分析了传统的FPGA实现的缺点,进而提出了用ZYNQ平台来实现阻抗分解算法。

该方案灵活利用了ZYNQ平台的优势,可以通过PS端在线配置参数,实现了数据的流水线处理,且取得了显著的效果。同时,大大降低了开发难度。对涡流设备的设计而言,此方案能够简化电路设计,降低成本,提高集成度,缩短研发周期,具有重要的现实意义。

[1]王广丰,钟海娜.发展中的涡流无损检测技术[J].煤矿机械,2005(2):7-8.Wang Guangfeng,Zhong Haina.Present Status of Research on Eddy Current NDT[J].Coal Mine Machinery,2005(2):7-8.

[2]郭太平.基于ARM和LabVIEW的高频电磁涡流检测系统集成设计[D].南京:南京航空航天大学,2016.Guo Taiping.Integrated Design of High Frequency Eddy Current System Based on ARM and LabVIEW[D].Nanjing University of Aeronautics and Astronautics,2016.

[3]石军,曹卫锋,徐方友,等.数字相敏检波在DSP中的实现 [J].郑州轻工业学院学报 (自然科学版),2005,25(2):85-87.Shi Jun,Cao Weifeng,Xu Fangyou,et al.The Realization of Phase Sensitivity Detection Technique in DSP[J].Journal of Zhengzhou University of Light Industry(Natural Science),2005,25(2):71-75.

[4]梁世盛,乔凤斌,张燕.基于FPGA的数字相敏检波算法实现[J].自动化仪表,2013,34(11):13-16.Liang Shisheng,Qiao Fengbin,Zhang Yan.Implementation of FPGA-based Digital Phase Sensitive Detection Algorithm[J].Process Automation Instrumentation,2013,34(11).

[5]Xilinx Inc.ug585-Zynq-7000-TRM(EB/OL).http://www.origin.xilinx-china.com/.2016.09.27.

[6]Xilinx Inc.ug1037-vivado-axi-reference-guide(EB/OL).http://www.origin.xilinx-china.com/.2105.06.24.

[7]李正轩,费树岷.基于Zynq-7000 FPGA的高速信号采集处理平台[J].新器件新技术.Li Zhengxuan,Fei Shumin.High-Speed Signal Sampling and Processing Platform Based on Zynq-7000 FPGA[J].New product&tech,2016(2):44-47.

[8]骆希,陶伟,黄荣鑫.基于FPGA的高速FIR滤波器并行结构设计[J].微处理机,2017(1):9-12.Luo Xi,Tao Wei,Huang Rongxin.Design of High Speed Parallel FIR Filters Base on FPGA[J].Microprocessors,2017(1)9-12.

Implementation of Impedance Decomposition Algorithm for Eddy Current Nondestructive Testing Based on ZYNQ

Peng Lefeng,Liu Kang,Liu Ji

(Institute of Rail Transit,Tongji University,Shanghai 201800,China)

Eddy current nondestructive testing has developed rapidly in recent years and is widely used in industrial inspection area.When it comes to the design of eddy current testing system,the most important part is the extraction of the flaw signal.Nowadays,most of these instruments use the method of impedance decomposition to extract the feature.On the basis of brief introduction of the principle and realization method of feature extraction technology,analyzing the disadvantage of the implementation of the analog circuit,DSP and traditional FPGA,a method of implementing this algorithmon on ZYNQ platform is proposed.This method takes advantage of ZYNQ platform,using hardware-software co-design and IP integration idea to achieve rapid development.With on-chip interconnect bus,dynamic parameters adjustability is realized.The impedance decomposition algorithm with this method can reduces the difficulty to implement,and has an outstanding ability to extract the flaw features.

Eddy current nondestructive testing;ZYNQ;Impedance decomposition;Hardware-software co-design;Digital signal processing

10.3969/j.issn.1002-2279.2017.05.017

TH701

A

1002-2279-(2017)05-0065-05

彭乐锋(1992—),男,广东省肇庆市怀集县人,硕士研究生,主研方向:无损检测。