锁相接收机扫描电路数字化设计

丁亚军, 成志锋, 傅黎黎, 陈 煦

(1.中国航天科技集团有限公司,北京100048;2.上海无线电设备研究所,上海200090)

0 引言

锁相接收机具有灵敏度高、跟踪性能好、能从噪声信号中提取出微弱信号等优点,广泛应用于航天、无线电遥测遥控、雷达和移动通讯及其它技术领域中[1]。锁相接收机依靠环路自身捕获能力对信号进行捕获,但是捕获带宽窄、捕获时间长,还可能出现迟滞、假锁等不可靠的捕获现象。辅助频率捕获方法较多,不同使用场合,辅助捕获设备的复杂程度有较大差异。常用的捕获方法有自动扫描法、辅助鉴频法、带宽切换法等。自动扫描法是实现快速、可靠频率稳定捕获的工程方法。在宽频带情况下,它是搜索、截获淹没在噪声中的信号的重要方法。以前,辅助扫描采用模拟扫描电路实现[2]。

在模拟扫描电路的设计和使用过程中,碰到许多问题。首先,模拟扫描电路的性能随组成电路的电容、电阻允差而变化;其次,模拟电路性能随温度的变化而变化,随着器件的老化性能发生漂移,影响贮存寿命。为解决这些问题,本文采用了数字化扫描捕获电路。从锁相接收机原理出发,根据数字扫描阶跃捕获需求进行理论推导,并进行了数字扫描电路设计和测试。结果表明,数字化设计是有效性。

1 基本原理

锁相接收机本质上是一个采用移频混频锁相体制的超外差接收机[3],其原理框图如图1所示。锁相环电路依靠扫描电路实现环路搜索捕获功能。

在锁相接收机的捕捉阶段,主要完成天线输入信号频率的捕捉。锁相接收机根据扫描电路送出的锯齿波扫描信号,微波本振产生从低到高的射频扫描信号。该射频信号与天线接收信号进行混频,经中频放大后,与中频参考信号进行比相,比相输出信号经过窄带环路滤波后作为环路误差。当本振频率扫描到外部天线信号频率附近时,锁相接收机停止扫描,依靠环路本身的捕捉能力使微波本振的频率稳定地锁定在天线信号频率上。

为了缩短捕获时间,应尽量提高扫描速率。但是,过高的扫描速率可能会导致信号在窄带滤波器内停留时间太短,不能及时锁定。当环路阻尼系数在0.7~1.0范围内,允许的最大捕获扫描速率Λ的经验公式为

式中:S/N是环路信噪比。

最大扫描速率可以通过锁相接收机的环路滤波器的参数调整,实现最优扫描。以有源积分二阶锁相环路为例,主要调整参数为R1、R2、C,如图2所示。

假定比相器灵敏度为Kd=0.56 V/rad,微波本振压控斜率Ko=2π×0.75×106rad/(V·s),环路滤波增益Ao=20,C=0.01μF,R1=12.1 kΩ,R2=220Ω。建立MATLAB仿真模型,可以得到最大扫描速度随R1、C变化的三维仿真结果,如图3所示。从图中可以看出:当C小于2μF时,最大扫描速率随着电阻R1的减小而增大;当R1小于100 kΩ时,最大扫描速率随着C的减小而增大。当R1、C较大时,最大扫描速率都很小。

2 数字化设计

依据上述分析,只要扫描速度选择合适,就可以实现捕捉[4]。模拟自动扫描电压信号是一个周期锯齿波,微波本振在这个电压作用下,频率从小(fL)到大(fH)变化,如图4(a)所示。采用数字阶梯扫描电路替代模拟自动扫描电路时,需要选择合适的数字阶梯。数字阶梯扫描电压产生一个周期性的阶梯电压,微波本振在这个阶梯电压作用下,频率发生阶梯状的变化,如图4(b)所示。由图4中可见,在模拟方式下,由于模拟电路的充放电特性,在第二次扫描前,扫描电压回到初始位置的时间较长。在数字方式下,可以在很短的时间内,返回初始位置。

为了缩短捕获时间,应尽量减小阶跃的间隔Δt,增大跳变频率Δf。

微波本振单次跳变频率必须小于两倍环路的捕捉带宽,以保证在数字阶梯扫描过程中捕获信号[5]。对于前文设定的环路参数,相应环路直流总增益为

环路的自然角频率ωn为

环路的阻尼系数ξ为

环路捕捉带为

可见,微波本振的跳变频率为两倍的Δfp,即3.526 MHz。考虑到不同产品环路KD、Ko的个性差异和高低温变化,为确保每次数字阶梯扫描都能够截获信号,应留有一定的余量。

单次频率跳变的时间间隔由最大捕捉时间和环路锁定判断时间决定。在单次跳变条件下,锁相环捕获锁定时间Tq为环路锁定判定时间TLmax和跳变频率下环路捕捉时间Tp之和。

环路锁定判断时间是指初始检测信号到确认环路锁定所需要的时间,通常为400μs。留有余量,取0.5 ms。如果微波本振单次搜索跳变1 MHz,总扫描频率带宽200 MHz,则总扫描时间为100 ms。

3 硬件设计

如上所述,数字扫描电路的计算量较小,采用单片机、CPLD、FPGA均可以完成上述功能。为获得更好的相位噪声,本设计采用CPLD,硬件原理框图如图5所示。

硬件电路板以CPLD为中心,配置相应的晶振、EPROM等辅助器件,完成所有算法[6]。电路设计了逻辑输入、逻辑输出、4路模拟输出。电源采用数字5 V和模拟5 V隔离的方式,降低数字电路对模拟电路的影响。CPLD的电源均采用线性电源,降低扫描电路板的数字噪声,提高产品的相位噪声性能。

4 试验探索

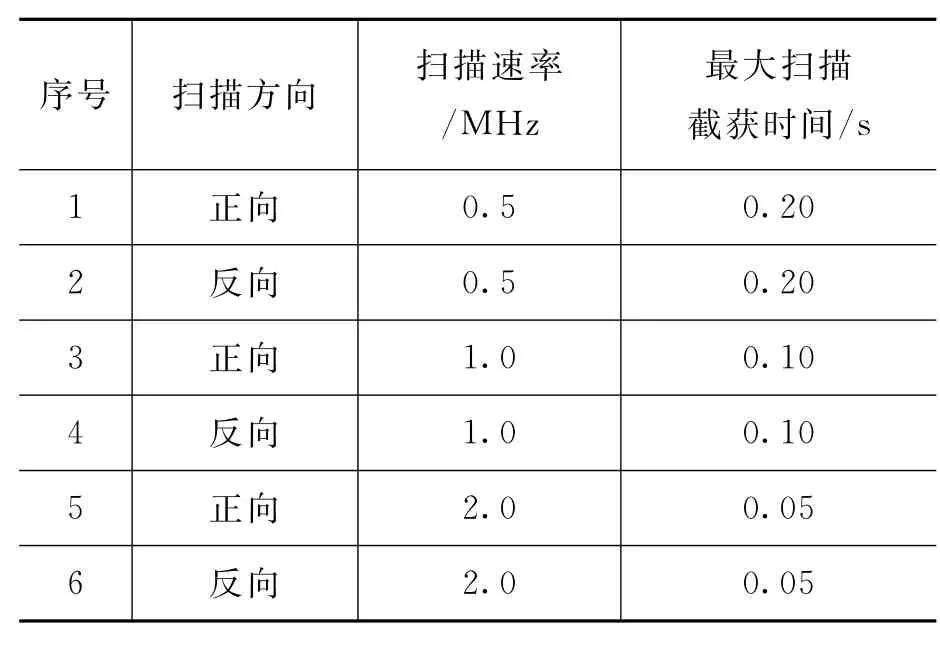

设置扫描速率为0.5 MHz、1 MHz、2 MHz,扫描方向为正向、反向,共6个状态试验,试验结果如表1所示。

表1 数字扫描试验结果

由表1可见,扫描阶跃频率越大,扫描截获时间越短。当扫描阶跃频率到达理论极限(3.5 MHz)时,正向扫描将出现偶尔不截获的临界情况,而反向扫描能够稳定截获。这是因为VCO本身存在一个正向频率漂移,使正向阶跃出现了超出锁相接收机的捕捉范围,导致环路失锁。根据一级降额的设计准则,留有50%以上的余量,即采用1 MHz作为该锁相接收机数字扫描阶跃频率。

5 结束语

本文针对模拟扫描电路设计和使用遇到的实际问题,对锁相接收机模拟扫描电路进行数字化设计改进。通过锁相接收机扫描电路数字阶梯扫描速度分析与试验,得到了最稳健的数字阶梯扫描速率。