DAM多通道同步波形发生的设计与实现

张秋明,周兴云,陆文斌

(上海航天电子技术研究所,上海 201109)

DAM多通道同步波形发生的设计与实现

张秋明,周兴云,陆文斌

(上海航天电子技术研究所,上海 201109)

基于数字阵列雷达在数字域实现幅相加权的需求,给出了一种基于时钟模块电路与DDS波形发生电路的八通道波形输出与输入参考时钟相位同步的设计方案。在AD9520-0零延时模式完成的DAM电路内外时钟相位同步基础上,采用AD9959自动同步模式完成八通道相位相互同步,最终实现了该方案。测试结果表明,相位误差在±1°。对DAM单元间数字波形发生同步的研究提供参考。

幅相加权;八通道同步;零延时模式;自动同步模式

0 引言

在现代和未来的战争中,空中力量的重要性将显得尤为突出,尤其是远程高精度武器的发展对掌握制空权和信息权起到了至关重要的作用[1],因此雷达系统的技术革新势在必行,并由此产生了以数字阵列波束形成取代模拟阵列波束形成的数字阵列雷达技术[2]。

数字阵列雷达技术的核心——数字阵列模块[3](Digital Array Module,DAM)包含了整个接收机、发射机、激励器和本振信号发生器,是数字阵列波束形成的系统硬件平台[4]。DAM承接了整个系统模拟信号和数字信号的相互转换[5],其性能直接影响数字阵列雷达发射波束形成的优劣,也在某种程度上决定了雷达系统的探测性能[6]。

2000年,美国海军研究办公室[7]联合MIT林肯实验室、海军研究所和海军水面作战中心[8]研究开发了包含数字波束形成结构的有源阵列雷达[9],使波形瞬时动态范围额外增加了30 dB[10],同时,也提高了雷达系统信杂比和快速自适应性,降低了整个系统的成本。2010年,美国普渡大学的William Chapple和Caleb Fulton设计了一个16阵元[11]、S波段数字阵列雷达系统,其中包含了高度集成、器件全数字化的控制板以及多通道的无线收发集成芯片[12],具备很强的校准监控与自我校正能力[13]。上述文献都介绍了在数字阵列雷达中采用数字波束形成技术来提高整个系统的集成度和性能,并降低了数字阵列单元体积和成本。

数字阵列雷达各通道间发射信号同步也是整个系统所需发射增益和波束指向的关键所在[14],更是雷达研究的技术难点。本文介绍了一种基于PLL和DDS(直接数字频率合成器)技术的DAM八通道同步波形发生电路的设计,实现了各通道发生波形之间的相位同步以及各通道波形与DAM输入时钟波形的相位同步,满足了数字阵列雷达在数字域实现幅相加权的需求[15]。

1 数字波形产生的基本原理

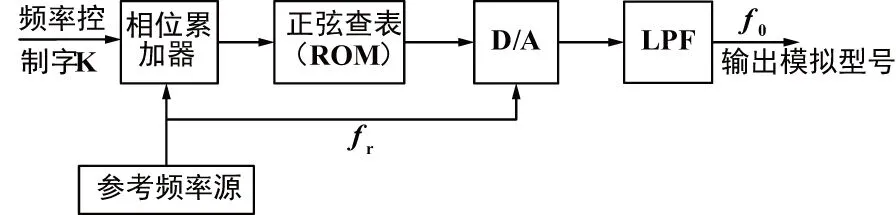

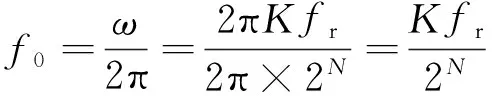

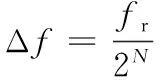

数字波形产生的DDS技术的基本工作原理是根据正弦函数的产生[16],从相位出发,用不同的相位给出不同的电压幅度最后滤波平滑出所需要的频率[17]。DDS的原理方框图如图1所示[18]。

图1 DDS原理

当DDS正常工作时,相位累加器在频率建立字FSW和参考时钟源的同步控制下,对其存储的抽样数字值不断地进行累加,直到累加至满量时,产生一次溢出,表示一个动作完成了它的周期[19]。该周期所用的时间即是DDS合成信号频率的周期时间。因此,输出合成信号的频率以及该频率合成器的频率分辨率可表示为:

(1)

(2)

式中,f0为输出信号的频率;Δf为频率合成器的频率分辨率;K为频率建立字[20];fr为参考频率源的工作频率;N为相位累加器的字长。

2 DAM多通道波形同步发生的实现

设计的DAM电路集成了8路数字波形发生通道,由时钟模块电路和波形发生电路两部分组成。

2.1 时钟模块电路

时钟模块电路选用ADI公司的AD9520-0芯片,为DAM电路中的2片DDS芯片提供了2路480 MHz差分工作时钟以及占空比为25%的2路同步时钟,为FPGA芯片提供了120 MHz的全局工作时钟以及为上变频单元提供了240 MHz的上变频时钟,同时利用AD9520-0芯片的时钟零延迟模式完成了DAM电路内部时钟与外部时钟的相位同步工作。芯片参考输入时钟(即DAM时钟输入)为120 MHz,而且零延迟模式将其通道0分频器120 MHz输出作为N分频器输入,PFD输入为8 MHz,这样R和N分频器的配置值都为15,VCO分频器为3,而各个通道分频器的分频值如表1所示。芯片环路滤波器的设计由ADI公司的ADIsimCLK进行仿真,相应参数是带宽200 kHz,电荷泵电流设为中间值2.4 mA,相位裕度45°,鉴相器的输入频率为8 MHz。

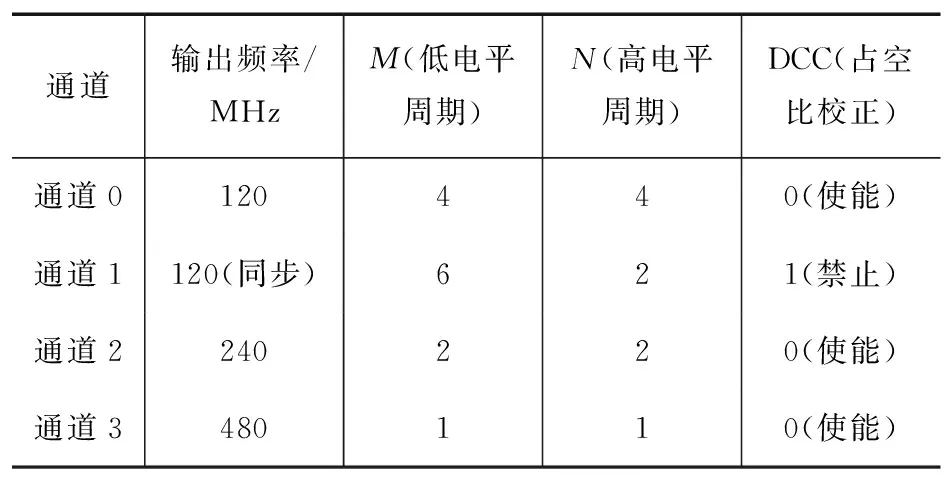

表1 通道分频器

以上就完成了DAM模块中480 MHz、240 MHz和120 MHz工作时钟与DAM本振输入时钟的相位同步工作。

2.2 DDS波形同步发生电路

在时钟同步的基础上,DAM电路选用了2片ADI公司的AD9959芯片来完成8通道数字波形的产生。该芯片拥有4个DDS核,可独立地对每个通道进行频率,相位和幅度的配置,其每个通道的输出原理框图如图2所示,最后得到中心频率为330 MHz的中频信号。该芯片的频率控制字为32 bit,相位控制字为14 bit,幅度控制字为10 bit。

图2 DDS波形输出电路原理

AD9959有4个通道,它们共享相同地址的寄存器,并且支持独立配置每个通道的寄存器,配置方式如下:

① 首先通过MASTER_RESET引脚给AD9959复位,让其控制寄存器都复位到其默认值;

② 配置CSR寄存器,将需要配置通道相应的使能位置1,其他通道使能位置0;

③ 使用串行通信将所要配置寄存器的数据写进AD9959,从寄存器0x03~0x18都可以进行配置;

④ 重复步骤②和步骤③,配置另外3个通道;

⑤ 将I/O_UPDATE位更新,这样就完成了AD9959四个通道的独立配置。

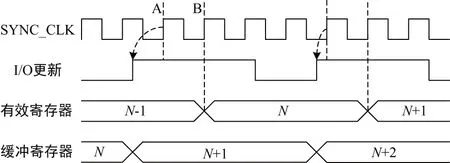

由AD9520-0芯片提供的120 MHz的同步信号是实现DDS多通道波形发生的关键所在。因为在AD9959芯片中,缓冲寄存器中的数据加载到有效寄存器的时间(即AD9959开始工作的时间)由I/O更新上升沿与SYNC_CLK共同决定。当2片ADD9959的I/O更新上升沿同步时(由FPGA控制),真正触发时间是由SYNC_CLK来决定的,如图3所示。SYNC_CLK为120 MHz,来源于AD9959的480 MHz工作时钟的内部4分频。4分频后的相位不确定性导致了2片AD9959通道输出波形相位的不同步。在有DDS同步时钟的情况下,AD9959通过SYNC_IN采样同步时钟脉冲信号完成了2片AD9959芯片间SYNC_CLK同步和输出波形的同步。同时,由于AD9520-0已经完成了DAM内部时钟与外部本振输入时钟的同步,因此2片AD9959的SYNC_CLK信号以及输出波形不仅互相同步,也与DAM的120 MHz的本振输入同步。

图3 AD9959寄存器传输时序

3 测试验证

文中给出了在没有DDS同步时钟下的2片AD9959的SYNC_CLK波形和2片DDS单频输出波形的相位关系,如图4所示,分别展示了复位之后2片AD9959的SYNC_CLK信号所会产生的4种相位差,这也是导致2片AD9959通道1所输出信号出现4种不同的相位差根本原因。

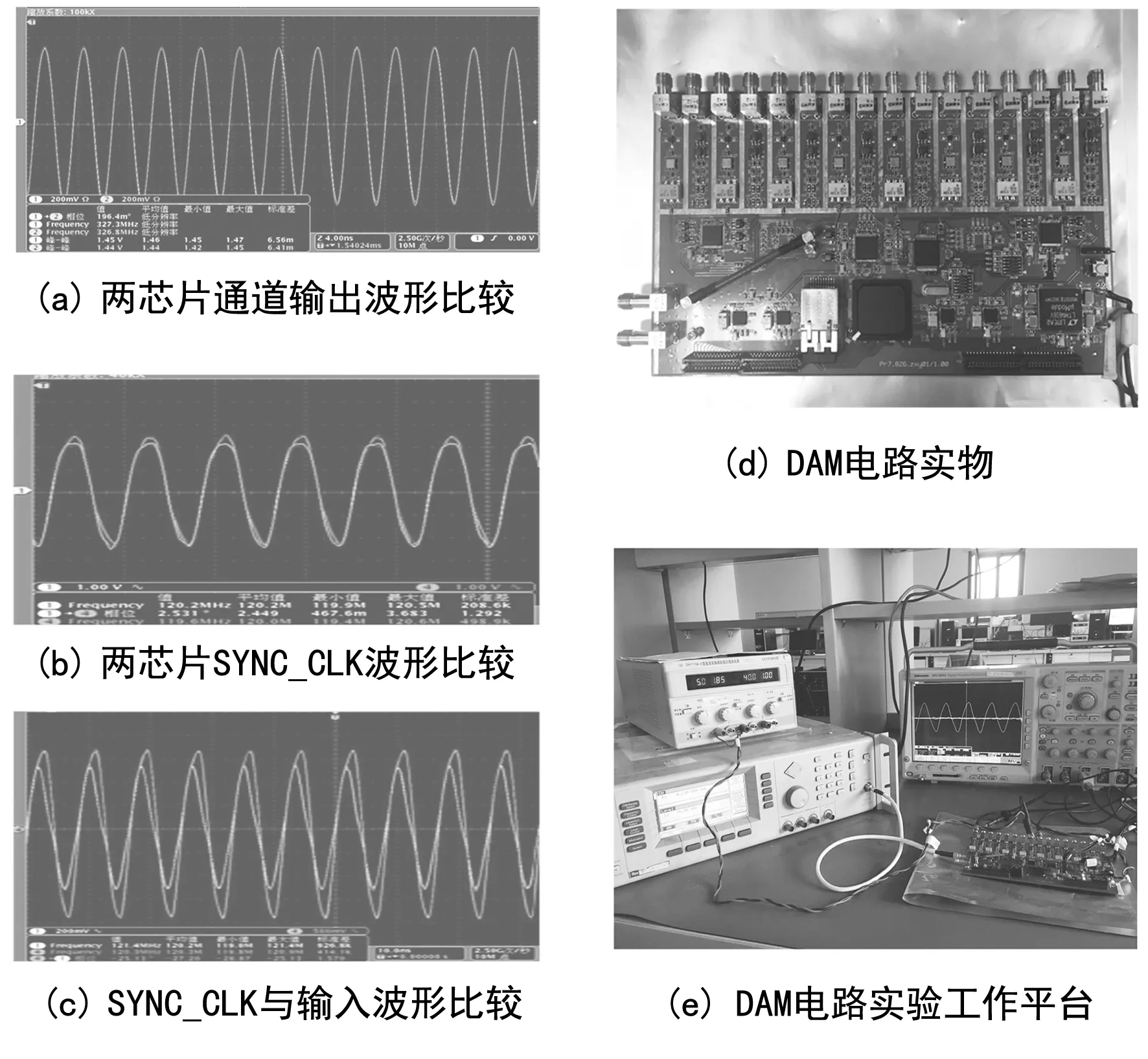

同步完成后,再对8个独立通道的幅度,相位控制字进行了调整,然后对2片AD9959通道1的输出以及SYNC_CLK时钟的波形进行了测试,同时测试了SYNC_CLK与DAM本振输入的波形关系,如图5所示,多次复位验证后,2片DDS输出以及DAM输入的确实现了相位同步,相位误差都在±1°之内。图5(e)和图5(f)分别为DAM电路的实物图和实验工作平台。

图4 同步前的波形测试

图5 同步后的波形测试

从图4可以看出,2片AD9959的SYNC_CLK信号存在4种相位差,分别是-89±1°、90±1°、178±1°和1±1°,平均分布在-180°~+180°,其现象与相位同步的信号经过2个不同的4分频器所产生的相位差现象一致。因此,进一步证明了2片AD9959之间的不同步源于AD9959内部对参考时钟的4分频。在实现同步之后,通过测量SYNC_CLK信号与DAM输入波形关系(频率相同)来表明DAM输出与输入波形的相位关系。测试结果显示,2个信号相位差为25±1°,表明DAM的波形输出相位与输入参考时钟的相位实现了同步。

4 结束语

详述了DAM中时钟模块电路和波形发生模块电路的设计,介绍了通过这2部分电路来完成DAM八通道数字波形产生的相位同步以及与DAM本振输入时钟同步的工作原理,并通过测试结果验证了硬件设计的正确性。在本电路研究的基础上,继续完成多个DAM单元参考输入时钟相位同步的研究,就可以完成多个DAM单元间数字波形发生的同步,使得多通道波形同步发生的通道数可以更多,甚至上百或者上千个通道波形发生完成同步。对数字阵列雷达波形相位研究以及雷达性能的提升具有工程实用价值。

[1] 吴曼青.数字阵列雷达的发展与构想[J].雷达科学与技术,2008,6(6):401-402.

[2] 贺寅.DBF权重处理电路的设计与实现[D].南京:南京理工大学,2012.

[3] MCLACHLAN A D.T/R Modules for Airborne Radar[C]∥The Challenges Ahead 35 European Microwave Conference,2005.

[4] 贺成,苏五星,徐敬伟,等.超宽带雷达和高功率微波武器一体化设计[J].舰船电子工程,2009,283(29):85-86.[5] DONALD J H.Solid State Transmit/Receive Module for the PAVE PAWS Phased Array Radar[J].Microwave Journal,1978,17(4):33-35.

[6] 刘晓政,陈荣兆,陶玉龙,等.一种C波段DAM设计与研究[J].中国电子科学研究院学报,2012,7(3):318-319.

[7] CANTRELL B,DE GRAAF J,LEIBOWITZ L,et al.Development of a Digital Array Radar(DAR)[C]∥Proceedings of the 2001 IEEE Radar Conference,2001:157-162.

[8] STAPLETON R,MERRANKO K,PARRIS C,et al.The Use of Field Programmable Gate Arrays in High Performance Signal Processing Application[C]∥IEEE International Radar Conference,2000:850-855.

[9] LEIBOWITZ L.Digital Active-aperture Phase-array Radar[C]∥IEEE International Conference on Phase Array System & Technology,2000:145-148.

[10] SZU Harold,STAPLETON Ron,WILLWERTH Frank.Digital Radar Commercial Application[C]∥IEEE International Radar Conference,2000:717-722.

[11] CHAPPELL William,FULLTON Caleb.DAR Panel Development[C]∥IEEE International Conference,2010:50-60.

[12] MILLIGAN J.SiC and GaN Wide Bandgap Device Technology Overview[C]∥IEEE Radar Conference,2007:17-20.

[13] MIR H S,ALBASHA L.A Low-cost High-performance Digital Radar Test Bed[J].IEEE Trans.Instrumentation and Measurement,2013,62(1):221-229.

[14] 容伟.数字阵列天线测量技术研究[D].南京:南京理工大学,2015.

[15] 张明友.数字阵列雷达和软件化雷达[M].北京:电子工业出版社,2008.

[16] 李站,陈金鹰.基于DDS芯片AD9851的信号发生器的设计[J].中国集成电路,2013,175(12):83-86.

[17] 王炜珽,李淑华,张文旭.基于FPGA实现直接数字频率合成脉冲线性调频信号[J].现代电子技术,2015,38(10):10-15.

[18] GANGELE S,DESAI N M.ISRO’s Programmable Digital Waveform Generator[J].IEEE Aerospace and Electronic Systems Magazine,2008,23(6):25-30.

[19] 王江涛,於洪标,张建增.低相噪DDS信号产生电路的设计[J].微波学报,2007(23):148-151.

[20] 张卫清,谭剑美,陈菡.DDS在数字阵列雷达中的应用[J].雷达科学与技术,2008,6(6):467-471.

Design and Implementation of Multi-channel Synchronous Waveform Generation in Digital Array Radar

ZHANG Qiu-ming,ZHOU Xing-yun,LU Wen-bin

(ShanghaiAerospaceElectronicTechnologyInstitute,Shanghai201109,China)

On demand of amplitude-phase weighting in the digital domain of the Digital Array Radar,a design scheme,that eight channels were synchronized with the input clock of the circuit through the clock module and DDS,has been achieved by synchronizing internal clock with external clock through the zero delay mode in AD9520-0 and eight output channels with each other through automatic synchronization mode in AD9959.Experimental result presents a phase error less than ±1°,which provides reference for the research in the channels’ waveform synchronization between multiple DAMs.

amplitude-phase weighting;synchronization of eight channels;zero delay mode;automatic synchronization mode

10.3969/j.issn.1003-3106.2017.07.20

张秋明,周兴云,陆文斌.DAM多通道同步波形发生的设计与实现[J].无线电工程,2017,47(7):82-85.[ZHANG Qiuming,ZHOU Xingyun,LU Wenbin.Design and Implementation of Multi-channel Synchronous Waveform Generation in Digital Array Radar[J].Radio Engineering,2017,47(7):82-85.]

2017-02-21

国防科工局军工科研基金资助项目。

TP391.4

A

1003-3106(2017)07-0082-04

张秋明 男,(1992—),硕士研究生。主要研究方向:数模混合电路设计。

陆文斌 男,(1980—),高级工程师。主要研究方向:数模混合电路设计。