基于DDS的Ka频段小步进捷变频频率综合器设计

冯占群,李洪涛,宋 旸

(1.中华通信系统有限责任公司 河北分公司,河北 石家庄 050081;2.中国电子科技集团公司第五十四研究所,河北 石家庄 050081;3.北京无线电计量测试研究所,北京 100000)

基于DDS的Ka频段小步进捷变频频率综合器设计

冯占群1,李洪涛2,宋 旸3

(1.中华通信系统有限责任公司 河北分公司,河北 石家庄 050081;2.中国电子科技集团公司第五十四研究所,河北 石家庄 050081;3.北京无线电计量测试研究所,北京 100000)

在通信、雷达和电子对抗系统中,频率综合器的频率步进、换频时间对系统的指标有重要影响。基于对DDS和锁相合成方式的理论分析和比较,结合DDS与锁相合成方式的优点,通过使用AD公司的最新DDS产品AD9914和优化设计,提出一种Ka频段宽带小步进捷变频频率合成器的实现方案,对合成器的相位噪声、杂散抑制和换频时间指标进行了理论分析。结果表明,该频率综合器在24~32 GHz输出频率下,最小频率步进可以达到300 Hz,换频时间优于10 μs。

频率合成;小步进;捷变频;直接数字频率合成;锁相环

0 引言

随着电子技术的发展,对作为现代电子设备和电子系统的基础,被誉为电子系统“心脏”的频率源性能提出了更高的要求[1]。捷变频、小步进、高频率和低相噪等指标越来越受到工程的青睐。但是上述各个指标会互相制约[2],如何选择合适的频率合成方案使其整体性能达到最优成为了工程设计的难题。针对此难题,提出了采用DDS和PLL相结合的技术,利用二者优势互补,在Ka频段实现低相噪、高杂散抑制的同时,将换频时间由以往常规的200 μs左右提高到10 μs以内,并且最小频率步进可达300 Hz。

1 频率合成原理分析

频率综合器在技术实现上通常采用锁相环、DDS或二者相结合的方案[3]。DDS具有极短的换频时间和极高的频率分辨率,但其杂散抑制较差;PLL可实现较高的频率和较宽的频率范围,环路滤波器使其具有优良的杂散抑制,但其换频时间和频率步进二者相互制约[2]。DDS+PLL相组合的方案可将二者优势互补,可实现综合器的小步进和捷变频要求。

通常DDS+PLL的频率合成器主要有3种组合方案[4]:① DDS与PLL直接混频方案。该方案将DDS与PLL的输出频率直接混频滤波后输出,设计原理简单、指标较好,但是对混频后的滤波器要求较高[5],综合器体积较大、成本非常高,实现起来较为困难。② DDS作为分频器的PLL方案。此方案将DDS当作一个小数分频器使用在PLL的反馈环路中,由于DDS具有很高的频率分辨率,因此可以产生低相噪、小步进信号[6],其缺点在于DDS的输出频率中杂散分量不容易滤除,影响最终输出指标。③ DDS激励PLL的方案,即DDS的输出作为参考信号进入鉴相器,通过锁相环倍频输出最终信号,虽然DDS输出信号中包含大量杂散信号,但是这些杂散信号可以通过环路滤波器滤除,可实现宽带频率的输出[7]。

2 设计与实现

2.1 整体方案设计

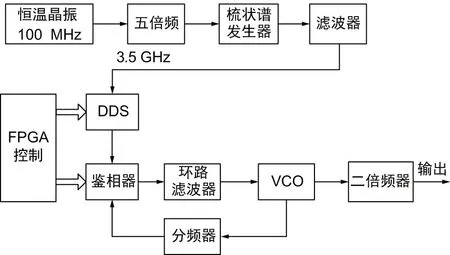

综合考虑,本文采用上面描述的第③种方案。原理框图如图1所示。恒温晶振输出的100 MHz参考信号经过5倍频后进入梳状谱发生器,将500 MHz各次谐波激励起来,通过带通滤波器选频,得到高稳、纯净的3.5 GHz信号作为DDS参考时钟。为了实现小步进、捷变频、低相噪和高杂散抑制,在DDS、鉴相器选型和环路滤波器参数设计优化上做了大量试验,倍频器选用低噪声倍频器;DDS和鉴相器的控制均采用高速FPGA芯片来实现。

图1 频率综合器原理

2.2 鉴相器选型

鉴相器选用Hittite公司的HMC704芯片[8]。该鉴相器为电荷泵鉴相器,输入参考频率范围为DC~350 MHz,反馈频率范围为DC~8 000 MHz,可以满足方案需求;鉴相器相位噪声基底在整数模式下为-233 dBc/Hz,可以实现频率综合器的低相噪要求。

2.3 DDS选型

DDS芯片选择AD公司的AD9914芯片[9]。该芯片调谐分辨率190 pHz,可有效地实现综合器的小步进需求。在输入参考时钟为3.5 GHz、输出100 MHz时相噪优于-152 dBc/Hz@10 kHz,可使综合器实现较优异的相噪性能。3.5 GHz的高时钟,使DDS在输出100 MHz时具有更好的杂散特性,进而使综合器具有优良的杂散性能。该芯片可以使用直接控制模式,其10 ns左右的切换时间,对综合器锁相环的建立时间基本无影响。芯片内部集成了重构滤波器,可以有效地消除采样过程的伪像以及滤波器带宽外的其他杂散。

2.4 环路滤波器设计

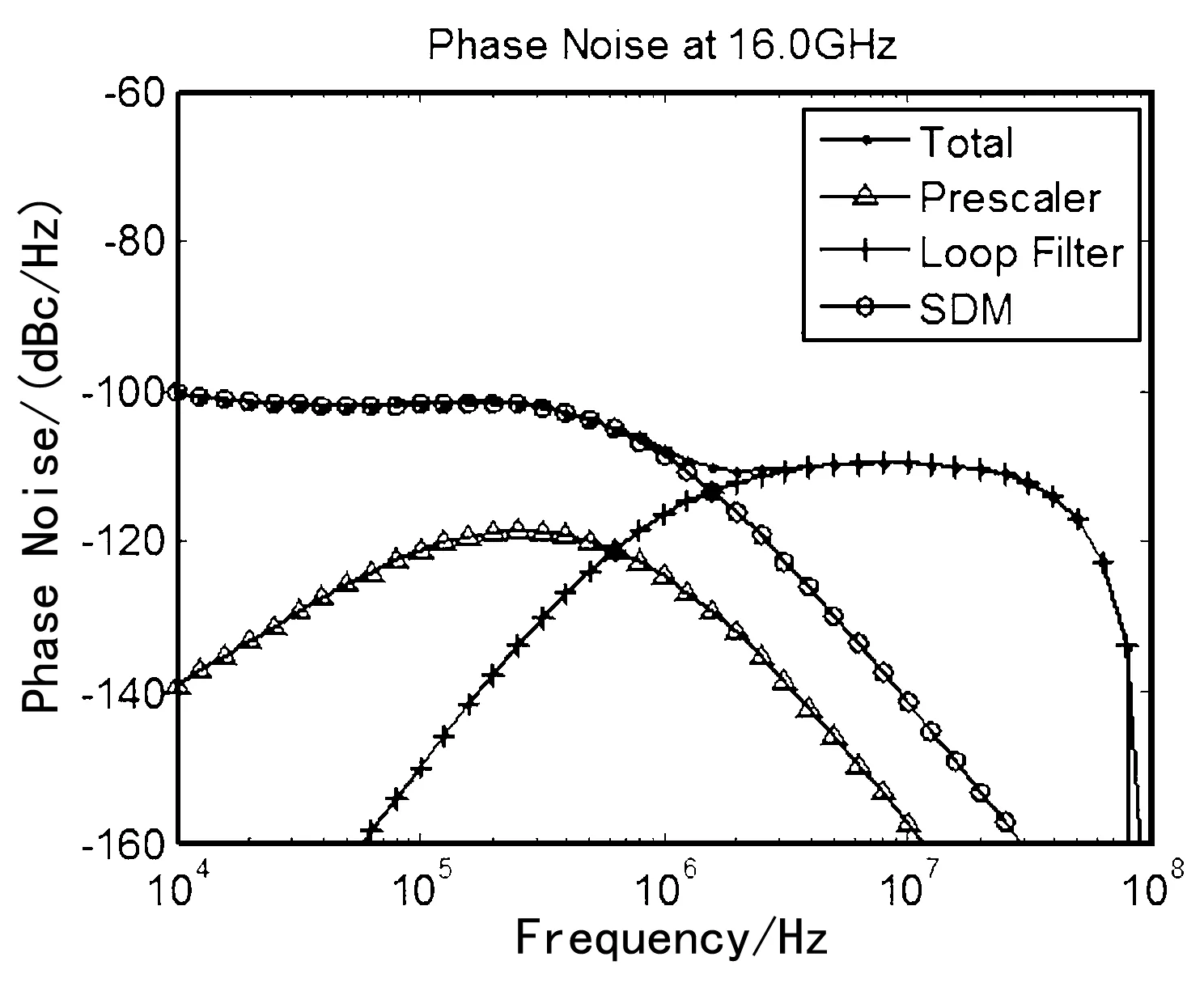

由于VCO调谐电压最大值为12 V,电荷泵输出电压无法达到,故环路滤波器采用有源积分环路滤波器[10]。设计环路滤波器时,为了兼顾相位噪声、换频时间和杂散抑制等各项指标,需要考虑环路滤波器阶数、环路带宽、相位裕量、零极点设置、电荷泵电流设置、鉴相泄漏抑制、电阻噪声、运放选型[11]和VCO压控灵敏度的变化等很多因素[12]。在工程设计中通过ADIsimPLL软件对输出信号的相位噪声进行优化仿真,结果如图2所示。其中X轴为偏离主频频率,Y轴为相位噪声,Total为输出信号相位噪声,Prescaler为芯片的噪声,Loop Filter为环路滤波器噪声,SDM为Σ-Δ噪声。

图2 环路滤波器优化仿真结果

3 性能分析

3.1 相位噪声分析

选用的100 MHz恒温晶振的相位噪声可以达到-165 dBc/Hz@10 kHz。倍频后的相位噪声为:

POUT1(f)=PIN1(f)+20logN。

(1)

式中,POUT1(f)为倍频后输出信号在频偏f处的相位噪声;PIN1(f)为倍频前输入信号在频偏f处的相位噪声;N为倍频次数,N=35,可得到综合器中输出3.5 GHz时钟信号的相位噪声为-134 dBc/Hz@10 kHz。

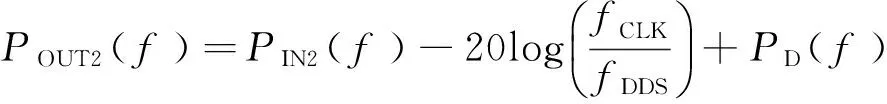

DDS输出信号的相位噪声为:

(2)

式中,POUT2(f)为DDS输出信号在频偏f处的相位噪声;PIN2(f)为DDS输入时钟信号在频偏f处的相位噪声,即式(1)中的POUT1(f);fCLK为DDS输入时钟频率;fDDS为DDS输出频率;PD(f)为DDS芯片在FDDS频率上频偏f处产生的相位噪声。

AD9914芯片资料中给出的相位噪声即PD(f)约为-152 dBc/Hz@10 kHz。经式(2)计算,POUT2(f)约为-150 dBc/Hz@10 kHz。

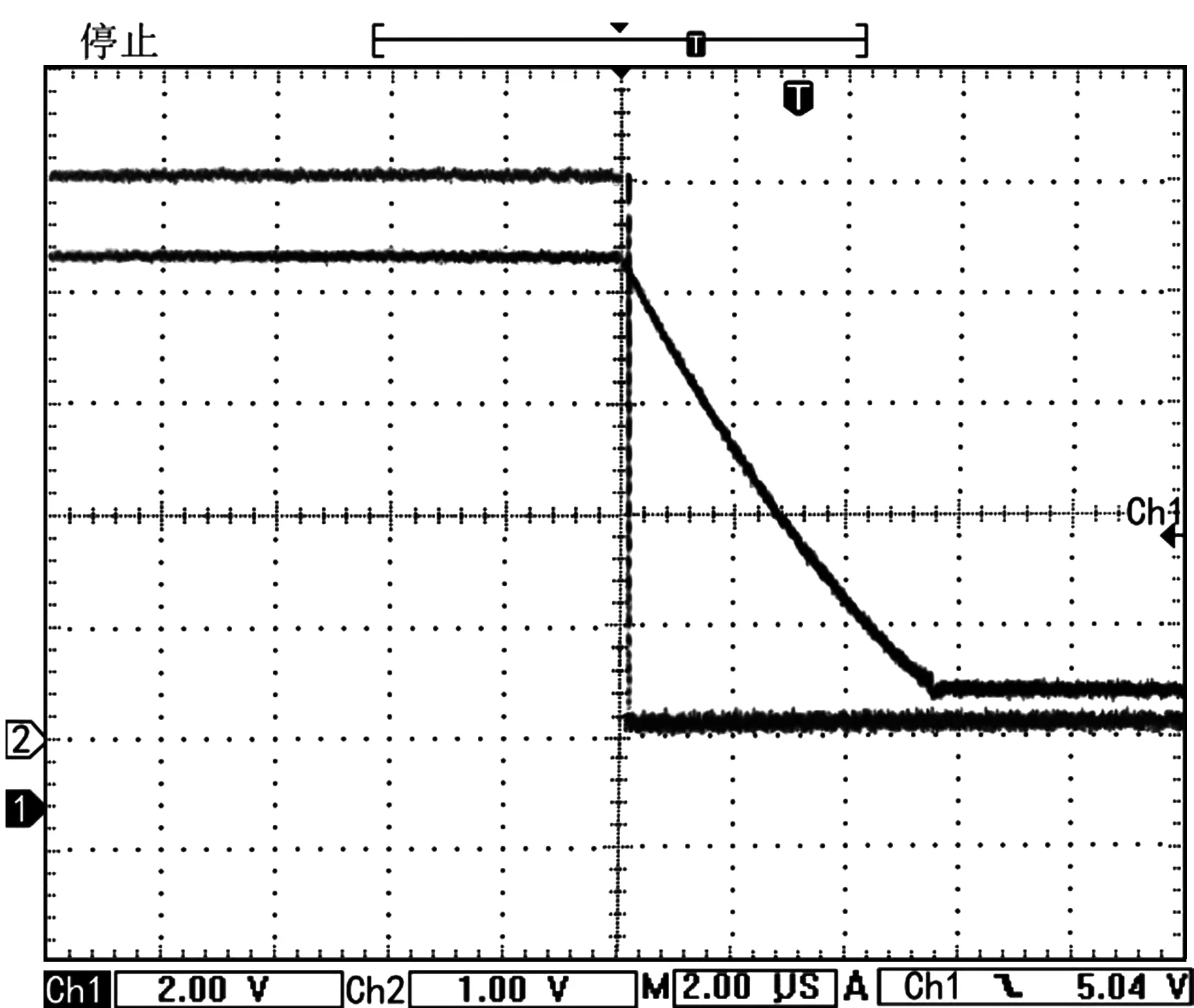

VCO输出信号的相位噪声主要由参考信号、鉴相器和鉴相器的闪烁噪声3部分决定[13]。

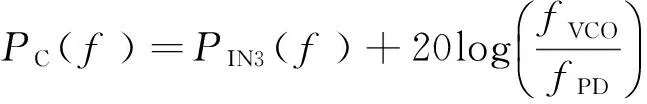

其中,由参考信号经锁相环倍频后所得到的相位噪声PC(f)为:

(3)

由鉴相器基底噪声倍频后所得到的相位噪声PPD(f)为:

(4)

由鉴相器闪烁噪声所得到的相位噪声Pflick(f)为:

Pflick(f)=FOM+20 log(fVCO)-10log(foffset)。

(5)

式中,PIN3(f)为参考信号在频偏f处的相位噪声;PN(f)为鉴相器归一化带内噪声基底;fPD为鉴相频率;fVCO为VCO输出频率;FOM为鉴相器闪烁噪声基底;foffset为频偏。

频率综合器输出频率为32 GHz时,fVCO为16 GHz,fPD为100 MHz,本文中PIN3(f)为DDS输出信号的相位噪声POUT2(f),即-150 dBc/Hz@10 kHz,HMC704芯片资料中PN(f)为-233 dBc/Hz@10 kHz,FOM为-266 dBc/Hz@10 kHz,foffset为10 kHz。利用式(3)、式(4)和式(5)计算得出:

PC(f)=-105.9,PPD(f)=-108.9,Pflick(f)=-101.9。

VCO输出频率的相位噪声为:

(6)

即PVCO(f)≈-99.9 dBc/Hz@10 kHz。

VCO输出频率经过2倍频后的相位噪声恶化6 dB,综合器最终输出信号的相位噪声理论值为-93.9 dBc/Hz@10 kHz。

3.2 杂散分析

频率合成器的杂散主要是由DDS产生。DDS的杂散成因主要分为相位截断引入的杂散、幅度量化引入的杂散和DAC转换产生的杂散[14]。目前改善DDS输出杂散的方法主要有抖动注入技术和ROM幅度表压缩2种方法。抖动注入技术是在每次累加器溢出时,注入一个随机整数到累加器上,以使相位累加器的溢出随机性提前,打破其周期性,这样就抑制了杂散的产生,但是会增加输出的噪声。幅度表压缩的原理就是增加ROM数据寻址位数,从而使DDS输出频谱得到进一步改善。

AD公司的AD9914芯片内部对杂散进行了处理,大幅降低了杂散的幅度和数量。其中近端杂散幅度一般较低,只有输出频率在fCLK/N(N<7)频点附近时,才会出现较高的近端杂散[13]。本方案中N≥35,此时DDS产生的近端杂散幅度非常低。

除DDS之外,其他因素也会造成杂散恶化。在设计中通过环路滤波器来滤除环路带外杂散,通过分腔屏蔽、信号隔离和加强电源滤波等进行远端杂散抑制;电路调试时在关键部位贴吸波材料,在加工误差缝隙中涂导电胶来抑制串扰杂散信号。

3.3 换频时间分析

频率合成器中,换频时间主要包括环路锁定时间和控制时间。为了缩小环路锁定时间,该频率合成器采用单环方案,同时适当增大环路带宽[15],可以保证环路锁定时间在10 μs以内。

在减少控制时间方面,电路设计中将锁相环的分频比设为固定分频比,通过改变DDS控制字使输出频率变化,省去了锁相环的控制时间。DDS在控制电路的实现上采用全并行控制方式,并行控制的控制切换速度可以保证在ns量级,对环路的换频时间的影响可以忽略不计。

综上所述,频率合成器的换频时间可以控制在10 μs以内。

4 测试结果

4.1 相位噪声及杂散抑制

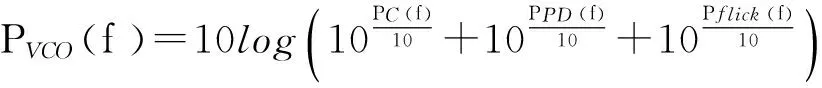

测试偏离主频10 kHz处的相位噪声指标如表1所示。

表1 相位噪声指标测试记录表

测试得到的相位噪声结果与理论计算值基本相符。经测试,杂散抑制指标优于65 dB。

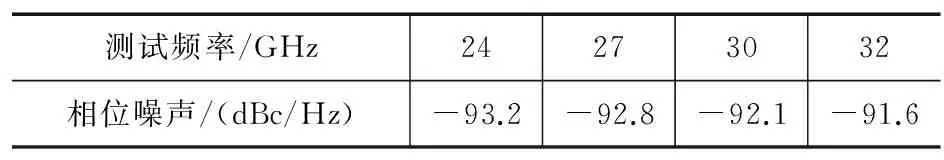

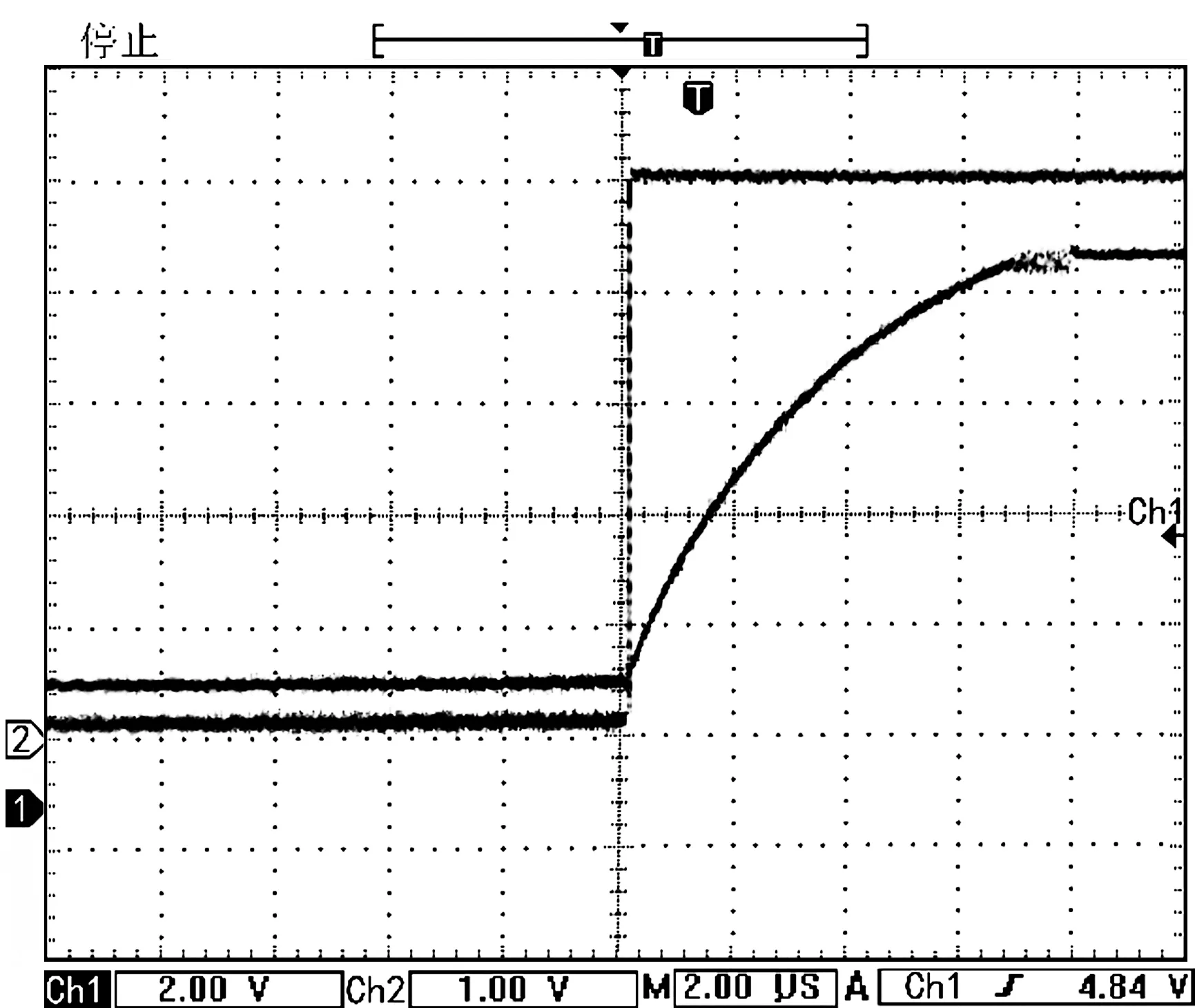

4.2 换频时间

换频时间测试方法是通过使用示波器测量VCO调谐端电压的跳变时间,结果如图3所示,其中变化较陡峭的信号为其中的一位控制信号,变化相对缓慢的信号为VCO的调谐电压。24 GHz向上跳变至32 GHz的测试曲线,换频时间约8 μs,如图3(a)所示;频率合成器从32 GHz向下跳变至24 GHz的测试曲线,换频时间约6 μs,如图3(b)所示。由图3可以看出,VCO从最低端到最高端的换频时间及最高端到最低端的换频时间均在10 μs以内。

(a) 24 GHz跳变到32 GHz的测试曲线

(b) 32 GHz跳变到24 GHz的测试曲线图3 换频时间测试结果

较国内公布的综合器结果来看,该综合器实现了Ka频段的宽频化,频宽展宽几倍以上;在Ka频段实现了300 Hz的频率步进,较以往的MHz以上的级别,有了巨大的提高;关键是在百Hz步进的情况下,实现了换频时间小于10 μs的性能。

5 结束语

本文方案利用DDS来实现小步进,通过改变DDS的控制字来改变输出频率,通过PLL将输出频率扩展到Ka频段,通过环路滤波器将DDS中众多的杂散分量滤除。该方案结合了DDS和PLL的优点,在Ka频段实现小步进、捷变频的同时保证了杂散抑制和相位噪声指标。相位噪声和换频时间的测试结果与理论值基本一致,反映出设计方案的合理性和科学性。通过理论分析可知,这种合成方案可获得较其他合成方式更为理想的换频时间指标,可应用于诸多频段的小步进捷变频率合成器中。

[1] 张建斌.锁相与频率合成[M].北京:科学出版社,2011.

[2] 王福昌,鲁昆生.锁相技术[M].武汉:华中科技大学出版社,1997.

[3] 高玉良.现代频率合成与控制技术[M].北京:航空工业出版社,2002.

[4] 白居宪.低噪声频率合成[M].西安:西安交通大学出版社,1995.

[5] 雷振亚,明正峰,李磊,等.微波工程导论[M].北京:科学出版社,2010.

[6] 李青平,刘方,蔡鹏飞.一种短波频率综合器的研制[J].无线电通信技术,2007,33(3):42-43.

[7] 杨新功,宋庆辉.超宽带低相噪频率合成器的实现[J].无线电通信技术,2006,32(3):39-41.

[8] Hittite Microwave Corporation.HMC704LP4E Datasheet[R],2012.

[9] Analog Devices Inc.AD9914 Datasheet[R], 2012.

[10] 张涛,陈亮.电荷泵锁相环环路滤波器参数设计与分析[J].现代电子技术,2008(9):87-90.

[11] MANCINI R.运算放大器权威指南(第3版)[M].姚剑清,译.北京:人民邮电出版社,2010.

[12] 张大鹤,李青平.一种超低相位噪声宽带频率合成器的设计[J].无线电工程,2016,46(2):58-60.

[13] 舒燕,李青平,柳星普.低杂散低相噪频率合成器的设计[J].计算机与网络,2009(15):48-51.

[14] TIERNEYJ,RADER C M,Gold B.A Digital Frequency Synthesizer[J].IEEE Transactions on Audio and Electroacoustics,1971,19(1):48-57.

[15] 蔡鹏飞,李青平,杨懿,等.基于谐波混频技术的宽带频综的设计[J].无线电通信技术,2016,46(2):58-60.

Design of Ka-band Small-step Agile Frequency Synthesizer Based on DDS

FENG Zhan-qun1,LI Hong-tao2,SONG Yang3

(1.HebeiBranch,ChinaCommunicationsSystemCo.,Ltd.,ShijiazhuangHebei050081,China;2.The54thResearchInstituteofCETC,ShijiazhuangHebei050081,China;3.InstituteofBeijingWirelessMetricandMeasurement,Beijing100000,China)

In communication,radar and electronic countermeasure systems,the frequency step and switch time of frequency synthesizer greatly affect the performance of the system.According to theoretical analysis and comparison on DDS and PLL,combining of their advantages,a detailed scheme of Ka-band frequency synthesizer with small frequency step and frequency agility is proposed using the AD Company’s latest DDS-AD9914.The phase noise,spur rejection and frequency switch time of frequency synthesizer are analyzed in theory.The experimental results show that the frequency step of the proposed frequency synthesizer is down to 300 Hz,and its frequency switch time is less than 10 μs within the output frequency range of 24 GHz to 32 GHz.

frequency synthesis;small step;frequency agility;DDS;PLL

10.3969/j.issn.1003-3106.2017.07.21

冯占群,李洪涛,宋旸.基于DDS的Ka频段小步进捷变频频率综合器设计[J].无线电工程,2017,47(7):86-89.[FENG Zhanqun,LI Hongtao,SONG Yang.Design of Ka-band Small-step Agile Frequency Synthesizer Based on DDS[J].Radio Engineering,2017,47(7):86-89.]

2017-02-14

海洋公益性行业科研专项基金资助项目(2013418028)。

TN743

A

1003-3106(2017)07-0086-04

冯占群 男,(1980—),工程师。主要研究方向:频率合成技术、射频与微波技术。

李洪涛 男,(1985—),硕士,工程师。主要研究方向:频率合成技术、射频与微波技术。