基于P2020的嵌入式计算机最小系统开发

何 斌,钟 洋

(成都蓉威电子技术有限公司开发部,四川 成都 610091)

基于P2020的嵌入式计算机最小系统开发

何 斌,钟 洋

(成都蓉威电子技术有限公司开发部,四川 成都 610091)

设计了基于PowerPC的嵌入式计算机最小系统,该系统由硬件系统和软件系统组成。硬件系统以P2020为核心,以DDR3和Flash为存储介质,以FPGA为逻辑控制单元,通过Local Bus实现对外总线,通过串口和千兆网实现通信接口;软件系统采用VxWorks6.8操作系统,实现了多核SMP对称多处理架构。功能测试和后期应用表明,该最小系统具有嵌入式计算机运算、控制、通信等基本功能,同时性能稳定,环境适应性强,可扩展性好。

P2020;最小系统;嵌入式计算机;VxWorks

嵌入式计算机最小系统是指某类嵌入式计算机的公共核心单元,具备最基础的软硬件功能且对外扩展出中心处理器的全部资源。开发某类嵌入式计算机,首先要开发其最小系统。

除嵌入式计算机基本功能外,最小系统还应配备对应的操作系统,同时具有小尺寸、低功耗、扩展性好等特点。根据这一需求,本文提供了一套基于PowerPC处理器和VxWorks操作系统构建嵌入式计算机最小系统的软硬件方案;本方案具有集成度高、处理能力强、功耗低、扩展性好、环境适应性强等优点。最小系统以Freescale公司的P2020为核心处理器,以Micron公司的DDR3 SDRAM为内存,以Intel公司的TE28F128J3D为Flash存储器,以Xilinx公司的Spartan3系列FPGA为逻辑控制单元,以Marvell公司的千兆网物理层控制器芯片88E1111作为网络桥接芯片对外通信,以Wind River公司的VxWorks操作系统作为其底层软件。

1 总体设计思路

最小系统以PowerPC双核嵌入式处理器P2020为核心,采用FPGA、DDR3 SDRAM、Flash、网络物理层、串口驱动、时钟、开关电源等功能芯片,实现基本硬件架构,并利用高速连接器对外扩展P2020处理器全部资源。

系统软件选用VxWorks操作系统,实现硬件初始化、设备驱动、文件系统等基本功能。

最小系统的设计功能为:(1)处理器。双e500V2内核,工作频率1 GHz,内存容量2 GB,Flash容量32 MB;(2)总线。对外扩展出32位Local Bus,总线时钟频率为100 MHz;(3)通信。实现2路自适应千兆网接口,1路RS232串口;(4)扩展。通过高速接插件对外拓展出PCIe/Rapid IO、USB、eSPI、SD/MMC、GPIO、I2C等全套处理器资源;(5)操作系统。支持VxWorks6.8嵌入式操作系统。

1.1 P2020内部架构

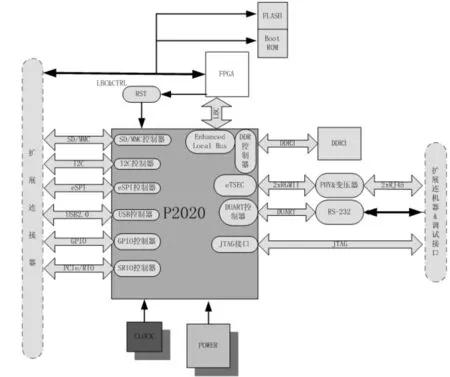

PowerPC P2020的内部架构如图1所示,集成2个e500V2内核及独立的64 kB L1 Cache和共用的512 kB L2 Cache,此外还嵌入DDR控制器、SerDes接口、增强型Local Bus、千兆网、USB、DUART等丰富的功能单元[1]。

图1 P2020内部架构图

1.2 最小系统功能框图

依据P2020的内部架构,结合总体设计思路,构建最小系统的硬件框架[2],如图2所示。

图2 最小系统硬件框架图

硬件系统对P2020的基本功能单元(如图2右侧、上侧)如DDR、Local Bus、千兆网、串口等进行了应用,同时将其他功能单元(如图左侧)对应的处理器管脚引至扩展连接器,便于后续扩展应用。硬件系统实现后,在此基础上建立VxWorks6.8高实时性操作系统,即达成本次设计目的。

2 硬件设计

2.1 P2020设计

PowerPC选用Freescale公司的P2020NXE2MHC,设计采用100 MHz单端时钟输入,通过处理器内部PLL倍频为500 MHz平台时钟,2个e500V2内核工作频率基于平台时钟倍频至1 GHz[3]。

2.2 DDR3设计

高速内存选用4片Micron公司的DDR3 SDRAM芯片MT41K256M16HA,单片容量为512 MB[4],内存总容量达2 GB。DDR控制器采用异步时钟模式,工作时钟频率配置为300 MHz[5]。

2.3 FPGA设计

FPGA主要功能是Local Bus剥离、上电配置、复位设置、看门狗实现、信号译码等,对逻辑资源要求较低,但需要一定的IO资源,故FPGA选型[6]Xilinx公司的XC3S400AN-4FTG256I,含有8 064个逻辑单元,195个IO管脚[7],逻辑设计开发工具为Xilinx公司的ISE 14.6。

2.4 Local Bus设计

P2020集成的增强型Local Bus是地址数据复用总线,总线时钟配置为100 MHz[3]。Local Bus在FPGA中通过组合逻辑剥离成地址、数据分开的本地总线,可挂接标准总线设备如Nor Flash。本次选型的Nor Flash为Intel公司的TE28F128J3D,容量为32 MB[8]。

2.5 网络设计

P2020自带3个千兆网内核,本设计应用其中2个,外接Marvell公司的千兆网物理层芯片88E1111-BAB1I000[9]和变压器实现2路自适应千兆网接口。

2.6 串口设计

P2020内部集成有1个DUART控制器,外接MAXIM公司的串口电平转换芯片MAX3232[10]实现1路RS232串口,主要用于在PC机的串口终端上打印调试信息。

3 操作系统设计

VxWorks操作系统是美国Wind River公司出品的嵌入式操作系统,具备高实时性和多任务调度能力,适合与精简指令集处理器PowerPC进行软硬件搭配。

P2020是双核处理器,故操作系统选择支持多核处理的VxWorks6.8,其开发平台为WindRiver WorkBench3.2。操作系统设计分为引导和建立2个过程[11]。

3.1 操作系统的引导

操作系统引导的基本思路是首先初始化核心组件并驱动引导设备,然后通过引导设备获取操作系统镜像,为操作系统建立打下基础。

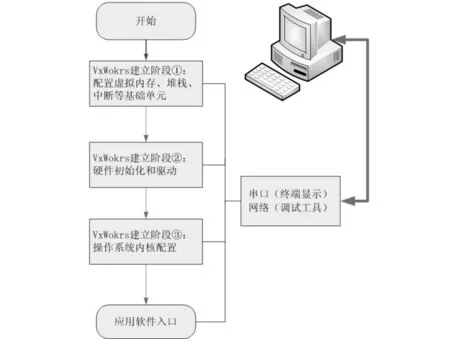

操作系统的引导可采用多种途径,如业内常用的U-boot标准化引导模式[12]。本次设计采用WindRiver WorkBench3.2编译生成的bootrom代码进行引导,其引导步骤[5]分为3个阶段,如图3所示。

(1)ROM运行阶段。配置e500V2内核、L2 Cache、DDR控制器等核心组件[13],为引导代码进入RAM运行阶段创造条件。

在本阶段中,引导代码直接读入至L1 Cache中运行,由于Cache容量有限,要求代码高效简洁,故此阶段运行代码由效率较高的汇编语言编写;

(2)RAM运行阶段①。初始化操作系统基础组件如中断、堆栈等[13-14];

(3)RAM运行阶段②。驱动终端显示设备串口和引导设备千兆网[13-15]。

图3 VxWorks操作系统引导流程图

RAM运行阶段完成后,操作系统的终端信息可通过串口在PC机上显示,同时能通过千兆网从PC机下载VxWorks操作系统镜像。

3.2 操作系统的建立

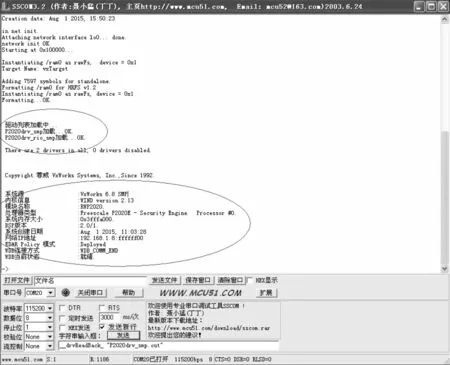

操作系统引导完成后,获取的操作系统镜像被放置到指定内存区域运行,即进入操作系统建立过程,该过程分为3个阶段,如图4所示。(1)配置中断、堆栈、虚拟内存等操作系统基础单元[13-14];(2)分配地址空间,初始化和驱动最小系统的所有硬件设备[13-15];(3)配置操作系统内核,完成操作系统建立,进入应用软件入口。

图4 VxWorks操作系统建立流程图

经历以上3个阶段,VxWorks6.8操作系统在最小系统硬件平台上建立成功,操作系统建立信息如图5所示,P2020的2个e500V2内核在SMP对称多处理架构下实现并行工作[16]。

图5 VxWorks6.8操作系统建立信息

4 系统测试

4.1 测试平台的搭建

根据最小系统的设计功能,搭建如图6所示的测试平台,最小系统的调试串口和2路千兆网口直接与PC机连接,测试母板通过扩展连接器与最小系统实现硬件连接,为最小系统提供直流电源。

图6 最小系统测试平台

4.2 测试方法

针对最小系统的设计指标,制定以下测试方法:(1)处理器测试。通过读取处理器相应的状态寄存器,对处理器双核运行状态、内核工作频率、内存容量和Flash容量进行测试;(2)总线测试。通过访问母板上的总线设备,对Local Bus的带宽和速度进行测试;(3)通信测试。利用PC机的网络和串口,对系统通信接口功能进行测试;(4)扩展测试。通过测试母板对扩展资源的应用,对系统扩展资源功能进行测试;(5)操作系统测试。硬件功能测试均在VxWorks6.8嵌入式操作系统下进行。

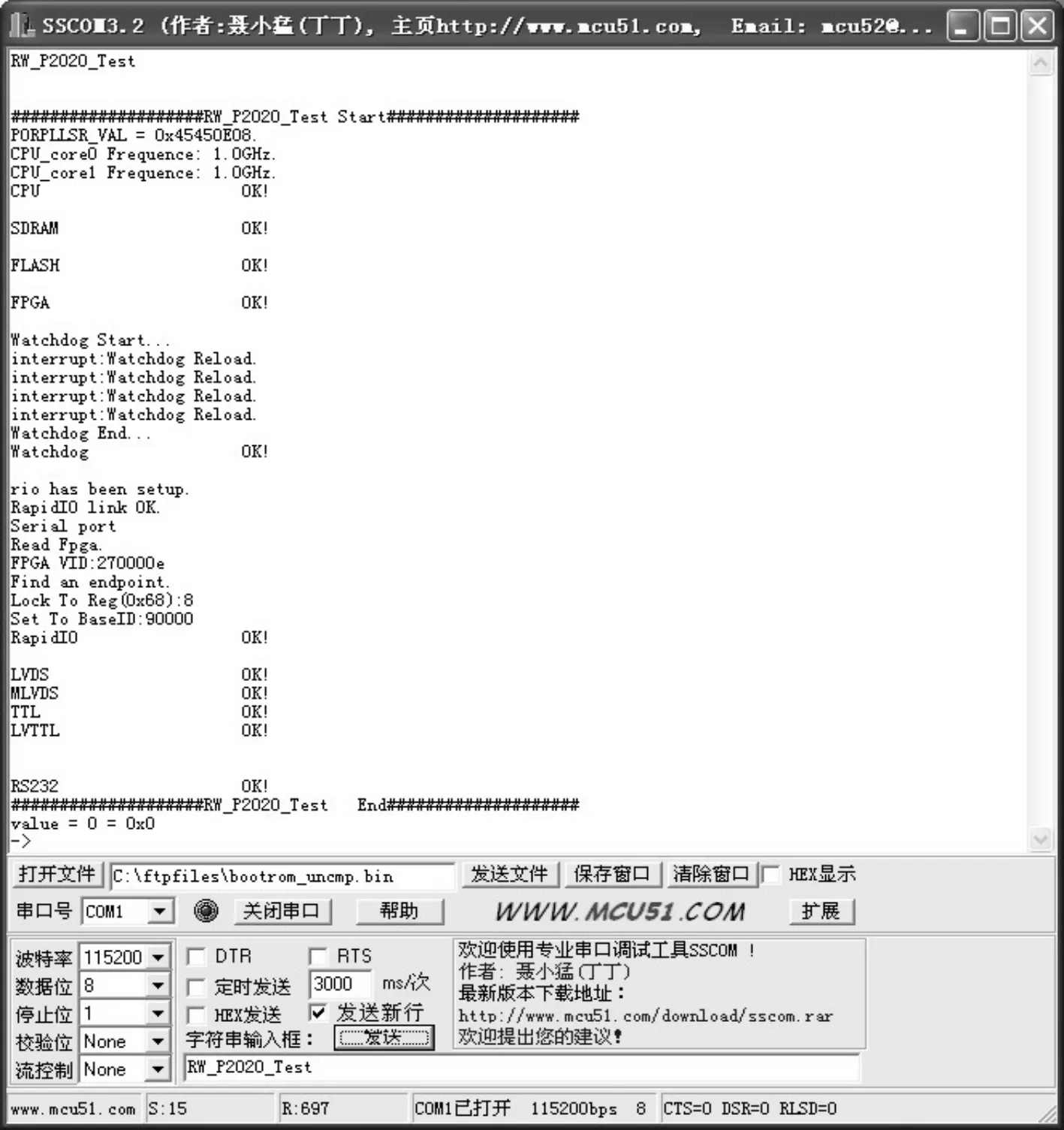

4.3 测试结论分析

经过反复测试和针对性调试,最小系统各个功能指标均通过测试,如图7所示。结合后期环境试验的验证,说明最小系统功能指标达到设计预期。

图7 最小系统的测试数据

5 结束语

本文立足于硬件电路设计、VxWorks操作系统开发等关键技术,对一款基于PowerPC P2020的嵌入式计算机最小系统实现过程进行了论述。经过测试平台测试和环境试验验证,该最小系统实现了前期制定的设计功能目标。在后期的衍生应用中,后续研制的P2020嵌入式计算机系列产品均是在该最小系统的基础上二次开发,大幅缩短了产品研发周期,其可扩展性也得到充分确认。如此可见,最小系统的预先研发就是产品平台的共性研制,在系列化产品的研制中有重要的意义。

[1] Freescale Inc.P2020 QorIQ integrated processor hardware specifications[M].USA: Freescale Inc,2011.

[2] Freescale Inc.P2020 QorIQ integrated processor design checklist[M].USA: Freescale Inc,2012.

[3] Freescale Inc.P2020 QorIQ integrated processor reference manual[M].USA: Freescale Inc,2011.

[4] Micron Inc.DDR3L SDRAM datasheet[M].USA:Micron Inc,2009.

[5] FreescaleInc.Power QUICC and QorIQ DDR3 SDRAM controller register setting considerations[M].USA:Freescale Inc,2014.

[6] 柏溢.FPGA的比较与选型[J].信息工程学院学报,1999,18(3):61-64.

[7] Xilinx Corporation.Spartan-3 FPGA user guide[M].USA:Xilinx Corporation,2009.

[8] INTEL Corp.Numonyx? embedded flash memory datasheet[M].USA:INTEL Corp,2007.

[9] Marvell Inc.88E1111 datasheet[M].USA:Marvell Inc,2004.

[10] MAXIM Inc.MAX3232 datasheet[M].USA:MAXIM Inc,2007.

[11] 乔从连.VxWorks系统的BSP概念及启动过程[J].舰船电子对抗,2005,28(1):61-64.

[12] 周德荣,夏龄.基于U-Boot的Linux内核映像加载与引导功能实现[J].廊坊师范学院学报:自然科学版,2010,10(4):33-35.

[13] 张杨,于银涛.VxWorks内核、设备驱动与BSP开发详解[M].2版.北京:人民邮电出版社,2011.

[14] 王洋,宋彦国,但果,等.VxWorks嵌入式实时操作系统设备驱动与BSP开发设计[M].北京:北京航空航天大学出版社,2012.

[15] 曹桂平.VxWorks设备驱动开发详解[M].北京:电子工业出版社,2011.

[16] Wind River Inc.Vxworks_kernel_programmers_guide_6.8[M].USA:Wind River Inc,2009.

Development of Embedded Computer Minimum System Based on P2020

HE Bin,ZHONG Yang

(Development Department,Chengdu Rongwei Electronic Technology Development Company, Chengdu610091, China)

Design a minimum embedded computer system based on PowerPC processor, The System is composed of hardware system and software system. System hardware to p2020 as the core, to DDR3 and flash as the storage medium, using FPGA as the logic control unit, by local bus external bus, realize the communication interface through the serial port and Gigabit network; software system adopts VxWorks6.8 operating system, realize the multi core SMP symmetric multi processing architecture. Functional testing and late application show that this system has the basic functions of embedded computer operation, control, communication and other basic functions, at the same time, stable performance, strong adaptability to environment and good expansibility.

P2020; minimum system; embedded computer; VxWorks

2016- 11- 07

何斌(1980-),男,硕士,工程师。研究方向:嵌入式计算机和嵌入式操作系统。

10.16180/j.cnki.issn1007-7820.2017.03.034

TP338.1

A

1007-7820(2017)03-121-04