可变频任意波形发生器设计

余先涛,孔文胜

(武汉理工大学 机电工程学院,湖北 武汉 430070)

任意波形发生器( Arbitrary Waveform Generator,AWG)作为测试仪器的一种,可以为测试系统提供各类基本及复杂的信号,普遍运用在工业控制、医疗和通信等领域。多种电子设备的检测都需要测试信号的激励,波形发生器作为测试系统中不可或缺的源头,成为实际应用中最普遍使用的电子设备之一,与示波器、万用表等设备一起成为最基本的测试仪器[1]。任意波形发生器的主要功能有:提供基本的函数波形,生成任意波形以及下载传输复杂信号,该3种功能使其具备很强的实用性和灵活性。因此,在航空、通信等高科技领域也得到了广泛应用[2]。

任意波形发生器的实现经历了模拟电路到数字电路的巨大转变,传统的波形发生器全部表现为模拟电路,采用机械驱动电容器或谐振腔等可变元件的方法调节频率,此类调节方式往往受到模拟元件的限制,调节范围小,结构复杂,难以产生复杂的波形;采用微处理器和数模转换器(Digital to Analog Converter,DAC)组成的波形发生器,取代了机械驱动调节频率的方式,使用数字电路合成频率的方法,对基准频率源进行分频和变频,由此产生比较复杂的波形[3];频率合成技术的发展给波形发生器带来了性能上的巨大提升,直接数字合成技术(Direct Digital Synthesis,DDS)采用全数字的方式,相比其他实现方式具有频率分辨率高、频率转换速率快、相位连续可变等优点。DDS原理在于采样还原信号,对于一个固定频率的信号,如果以某一固定的时间间隔进行采样,则原始信号可以通过采样值恢复出来。笔者在对DDS性能进行分析后,详细介绍了一种基于FPGA(Field Programmable Gate Array)实现DDS技术的方案,实现了可编程的多频双通道任意波形输出。通过最终性能测试证明了该设计的有效性和实用性。

1 设计原理及方案分析

1.1 DDS系统原理

直接数字合成技术从相位角度出发,通过设置频率控制字得出相位值,对波形存储器进行查表从而直接合成所需的波形,其特点包括响应速度快、频率分辨率高、转换速度快以及能够产生任意波形等。

DDS系统的理论基础为Nyquist采样定理,根据该理论,在模/数信号转换过程中,被采样数字信号若要完整恢复原始信号的信息,则在采样过程中,采样频率fs要高于信号最高频率fmax的两倍(fs>2fmax)。但是该原理在DDS技术中的应用是相反的过程,DDS系统不是对模拟信号进行采样,而是根据已经数字化的采样量化值,采取某种方式将模拟信号恢复出来[4]。

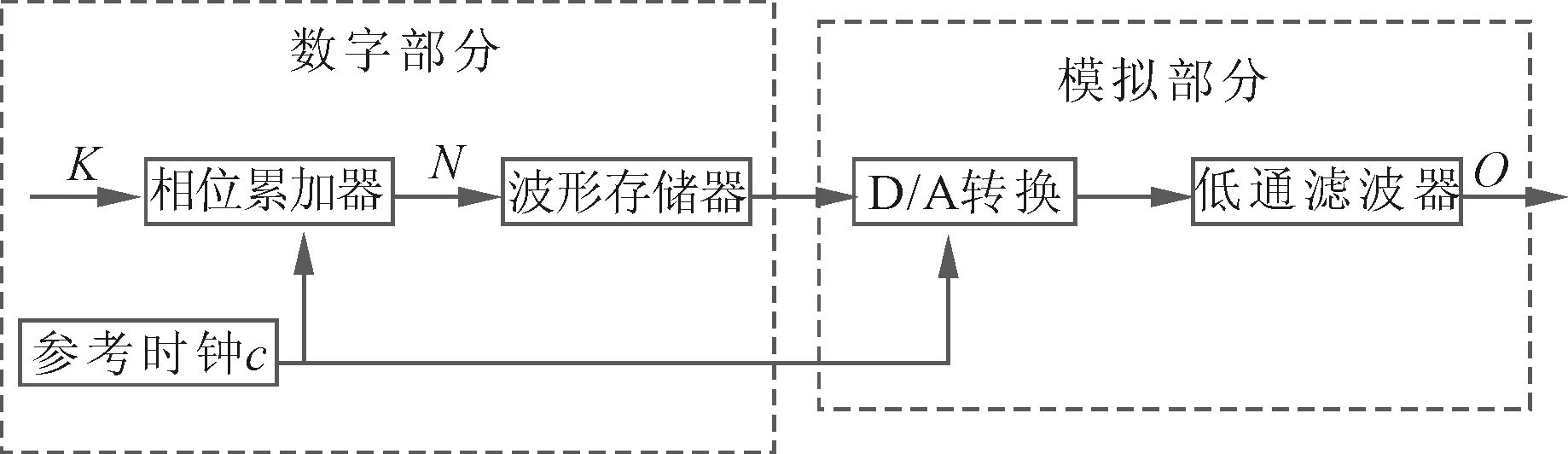

DDS系统的典型结构如图1所示,该系统由参考时钟、相位累加器、波形存储器、D/A 转换器(DAC)和低通滤波器(Low-Pass Filter,LPF)5个部分构成[5]。

图1 DDS系统结构

其中K为频率控制字,N为相位累加器位数,相位累加器与波形存储器相连,N值也为波形储存器的存储深度,fc为参考时钟频率,fo为系统输出频率。波形幅度值预先置于存储器中,通过设置频率控制字得出相位值,对波形存储器进行查表从而得到所需的波形值。

由傅立叶原理可知,时域内不同频率的正弦波信号叠加可以构成任何所需的波形信号,下面以正弦波为例,分析K值对于输出波形频率的影响。正弦波信号以某一固定间隔采样、量化后,将量化值存储在波形存储器中,假设存储的幅度量化值有2N个,相位累加器的位数为N。现以频率为fc的系统时钟进行采样,即时钟周期为Tc。取频率控制字K的值为k,即相位累加器的相位步进值为k,在系统时钟的控制下,经过2N/k个时钟周期后,相位累加器输出所有的相位值,波形存储器也取出所有的幅度值,即输出正弦信号循环一周,此时输出正弦波的周期为:

(1)

输出频率为:

(2)

根据式(2)可知,任意波形发生器的输出频率由采样频率fc、频率控制字K及相位累加器的位数N共同决定。一般而言,相位累加器的位数N和系统的采样频率fc在设计时已经固定,编程改变频率控制字K值即可获得不同频率的波形。

1.2 方案可行性分析

以DDS技术实现的任意波形发生器融合了数字处理技术与信号合成理论,与锁相频率合成技术具有本质上的差别,其性能上也存在着独特之处,主要体现在以下几个方面:

(1)输出频率相对带宽宽。根据式(2),当频率控制字K为1时,DDS系统的输出频率为最低输出频率,当相位累加器的字长N很大时,最低输出频率可达到微赫兹。DDS系统的最高输出频率受到时钟频率和抽样定理的限制,最高可达0.5fc,在实际应用中,考虑到滤波器的非理想特性,一般认为最高输出频率为0.4fc。

(2)频率分辨率高。DDS系统的频率分辨率就是其最小频率步进值,即最小输出频率,频率分辨率取决于参考频率fc和相位累加器字长N,本设计采用的N为48,fc为100 MHz,则频率分辨率为3.55e-7,超高的频率分辨率可以使输出频率逼近频率的连续变换。

(3)频率转换时间快。所谓频率转换时间即为连续输出两个不同频率的信号相隔的时间,对于DDS系统,该时间即为频率控制字K的传输时间,一般只需要几个时钟周期,本设计采用100 MHz的参考频率,则频率转换时间为几百纳秒,可见DDS系统输出不同频率的信号可以近似认为是实时的。

(4)频率变换时相位保持连续。改变DDS系统的输出频率,实际上是通过改变频率控制字K,改变相位累加的速率,这个过程中相位函数曲线是连续的,只是在改变频率的瞬间其斜率发生了突变,因而保持了输出信号相位的连续。

(5)可输出任意波形。DDS系统中,波形存储器用于事先存储波形的离散幅值,改变在RAM(Random Access Memory)中的函数表格,即可输出所需的波形。

由于DDS技术具备的独特性能,市场上逐渐出现了高度集成的DDS专用芯片,该类芯片使用起来较为简单,可以直接输出高质量的波形信号。专用DDS芯片覆盖的频率范围较广,内部集成了高分辨率的DA转换器,可直接输出高质量的波形信号,而且功耗较低。但是此类芯片存在明显的不足:只能产生非常有限的波形,灵活性差。这是因为芯片内部采用只读存储器(Read-Only Memory,ROM)来存储波形数据,芯片出厂时内部数据已经固定,无法根据用户需求进行改变。

相比专用DDS芯片,采用可编程逻辑器件实现DDS技术具有更强的灵活性。现场可编程门阵列(Field Programmable Gate Array,FPGA)内部集成了波形存储RAM,不同于只读存储器,它不仅读取速度快,而且随时可以修改内部数据,实现任意波形的输出。与此同时,基于FPGA实现的DDS系统可以根据用户需求进行功能上的修改和增删,方便了对任意波形发生器进行二次开发。价格方面,高性能的专用DDS芯片售价达到上百美元,是高性能FPGA芯片的几倍,采用FPGA进行开发有助于降低设计成本。

FPGA技术提供了灵活性和快速原型的能力, 用户可以多次测试不同的想法,并在硬件中完成验证,而无需经过设计专用DDS芯片的漫长过程,缩减了产品的研发时间,再加上丰富的EDA工具的支持,非常适合于任意波形发生器的数字部分的设计。综上所述,本设计采取以FPGA芯片实现DDS技术的设计方法。

2 硬件电路设计

2.1 总体设计方案

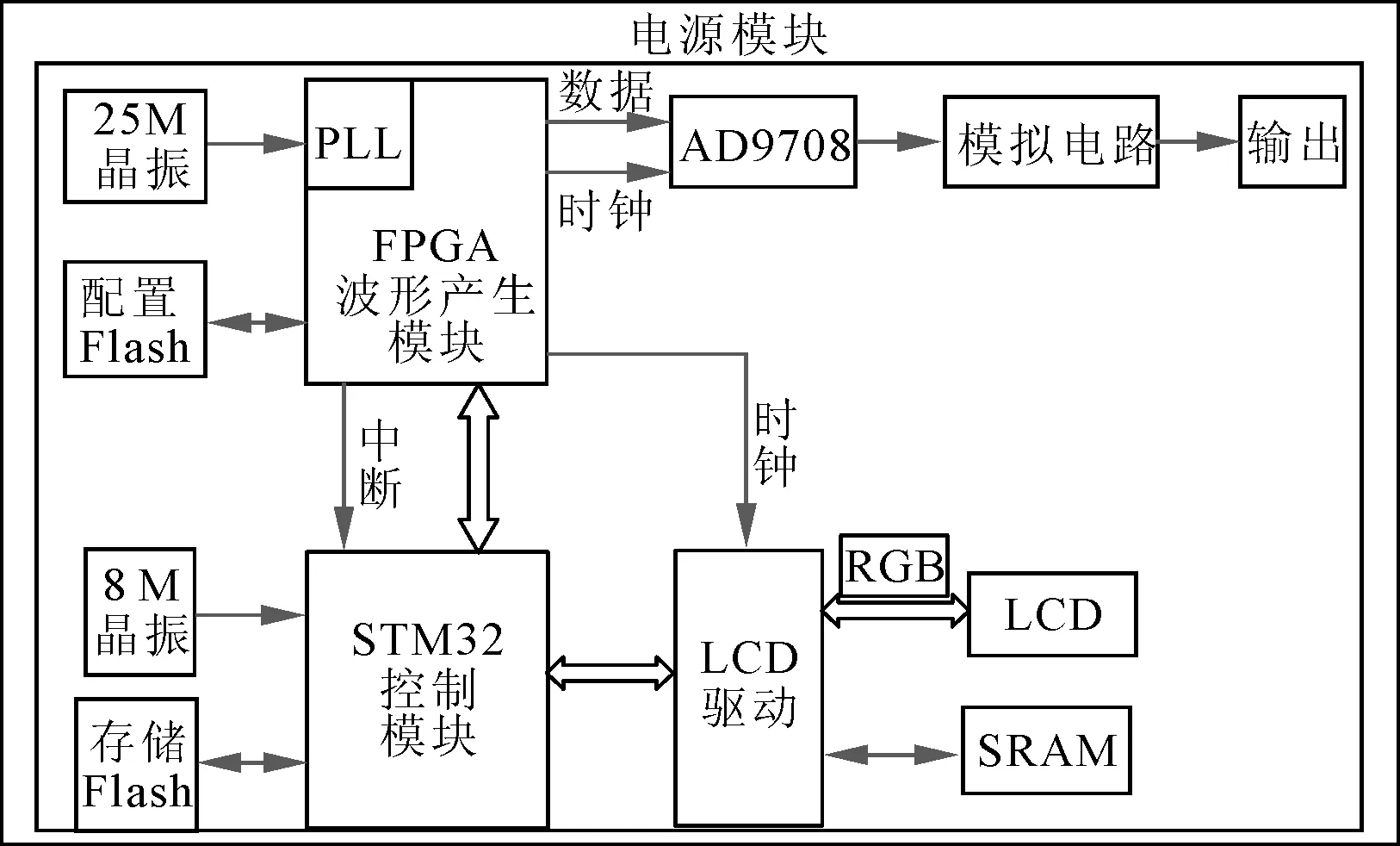

硬件设计在满足系统功能指标的前提下,采取模块化的设计方法,使得电路结构清晰、设计简便,硬件系统框图如图2所示。

该硬件系统主要由ARM控制模块、波形产生模块、模拟处理模块、液晶驱动模块和电源模块组成。

(1)电源模块环绕整个系统,为各部分提供合适的输入电压。

(2)波形产生模块位于FPGA内部,DDS系统产生波形的数字信号,输入至高速DAC芯片AD9708,完成数模转换后,由模拟电路进行平滑、放大衰减等处理,输出平稳的模拟信号。

(3)外部25M晶振输入FPGA,经内部锁相环倍频和分频后分为两路,一路时钟信号输入DDS系统,一路时钟提供给高速DAC芯片。

图2 硬件系统框图

(4)主控ARM芯片采用STM32系列产品,该系列产品既可以实现系统的控制任务,又具有成本低、功耗小等优点,STM32配以8 M的晶振,工作频率较低,从而降低功耗,STM32通过内部的可变静态存储控制器(FSMC)与FPGA通信,简化了通信过程,数据传递更快捷有效。

(5)系统配有两片相同的FLASH芯片,一片用于上电时配置FPGA内部数据,另一片与STM32通信,用于存储开机所需画面的数据和字库。

2.2 D/A转换器

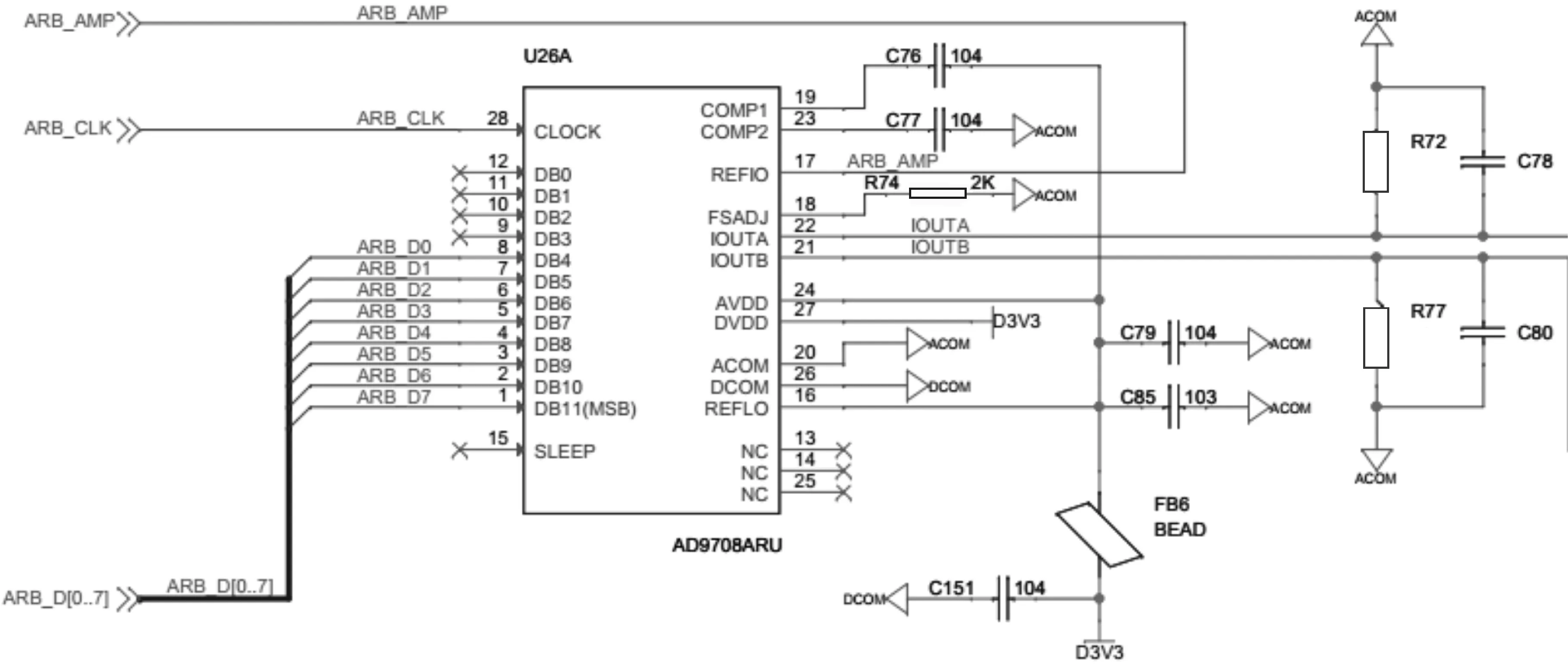

系统选用ADI公司的8位分辨率产品AD9708,该芯片为电流型DAC,由一个大型PMOS电流源阵列组成,提供高达20 mA的总电流,分为两路输出IoutA和IoutB,既可以通过互补方式输出电流,也可以转换为IoutA单端电压,D/A转换电路如图3所示。

图3 AD9708的D/A转换电路图

在该电路中,ARB_AMP为AD9708的参考电压,来自STM32内部的数模转换器,程序控制该电压值的范围为0~1.25 V,ARB_CLK是由FPGA芯片内部PLL输出的时钟信号,为AD9708提供100 MHz的转换速率。根据系统的设计指标,DDS系统输出波形的最高频率为10 MHz,因此100 M的SPS转换速率完全可以满足最高频率波形的数模转换要求。

AD9708提供差分电流输出,采用差分输出时,可以有效抑制信号中的共模噪声,当差分信号作为后端运放的输入级时,还可高效抑制外界环境中的电磁干扰,两个差分端的电流值共同分担AD9708的满量程输出电流20 mA。

由于AD9708是一款电流输出型的DAC,而且以差分电流方式输出,因此输出侧需要一颗I-V精密运放,实现电流耦合及电流至电压转换,同时提高数模转换器的驱动能力[6],本设计采用LMH6643芯片进行转换,该芯片内部集成了两个运算放大器,系统采用其中一个用于差分放大电路,产生中心在零点的波形。

2.3 滤波电路

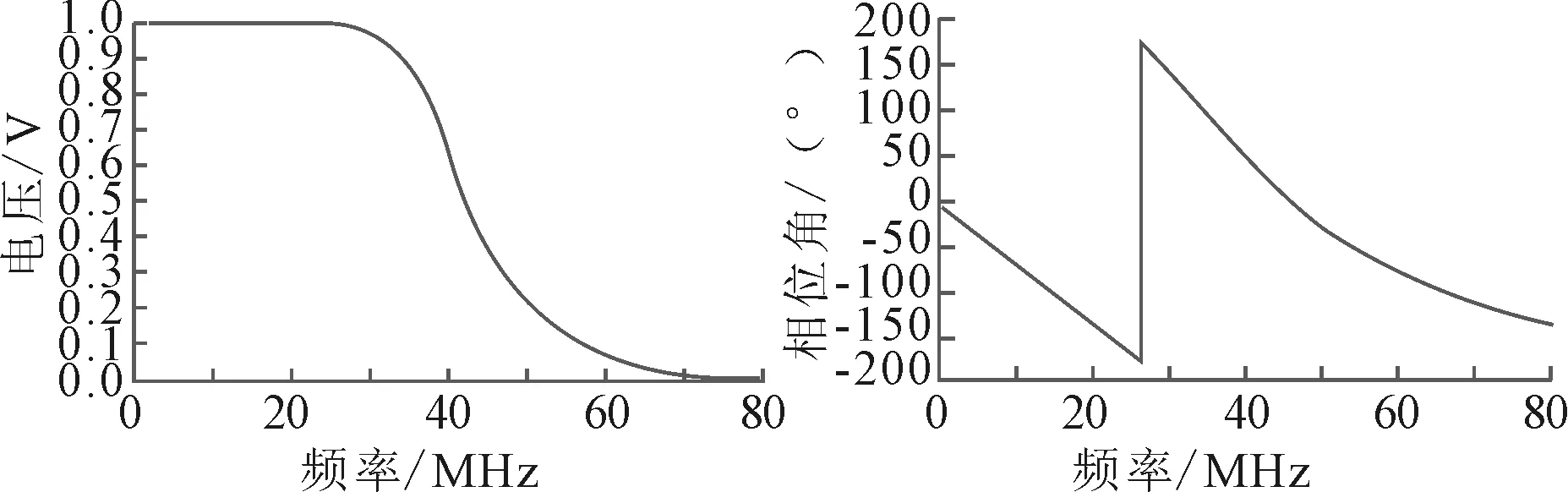

图4 滤波器幅频和相频特性

由DAC输出的模拟信号为阶梯状电平,同时含有复杂的频谱分量及杂波,因此需要滤波器平滑波形,保持有效分量以及抑制杂波。笔者选取滤波器时尽量保证通带内波形平坦,因此采用7阶巴特沃斯滤波器。根据设计需求,DDS系统输出波形的最高频率为10 MHz,由于滤波器的过渡带较长,为提高波形的最高频率,将滤波器-3dB的截止频率定为40 MHz。

3 逻辑系统设计

逻辑系统的设计是任意波形发生器设计的关键,FPGA芯片实现了DDS原理,完成了时钟倍频分频、相位累加器、波形存储器等多个功能及器件。本系统采用的是Altera公司第IV代Cyclone产品EP4CE6E144,该芯片采取60 nm低功耗工艺,采用1.2 V内核电压,包含6 272个逻辑单元,144个引脚,采用EQFP封装。

3.1 DDS模块

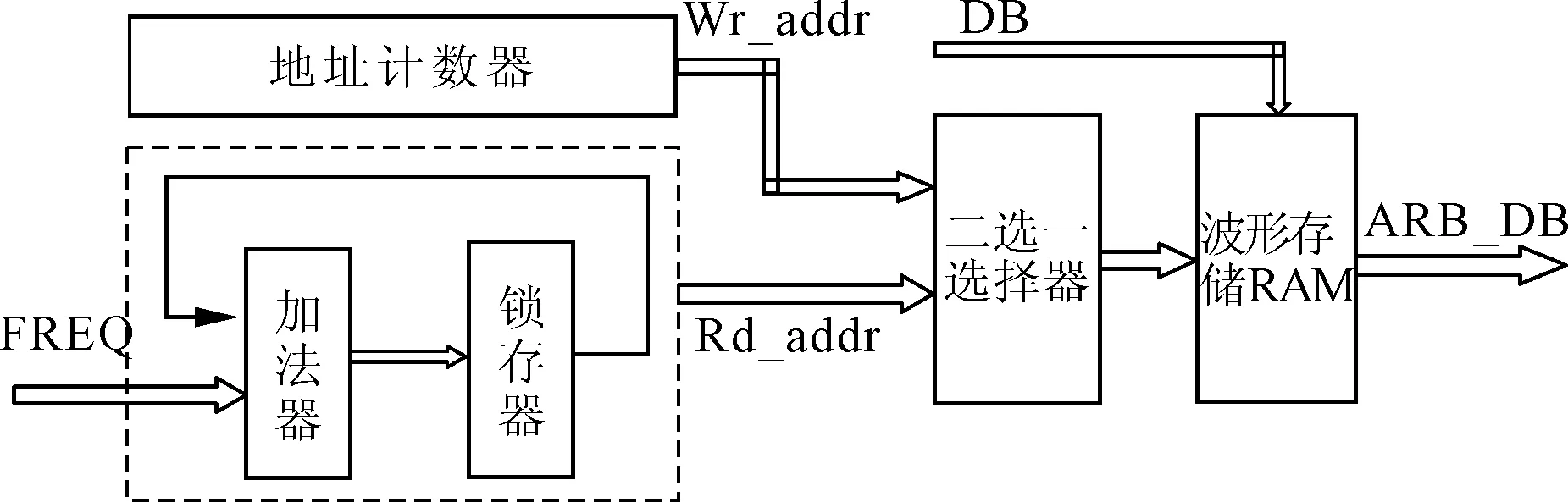

在逻辑系统的设计中,DDS模块为最核心的

部分,通过累加频率控制字K得到相位值,以相位值作为地址值对波形RAM查表,输出波形的幅度值。DDS模块的原理示意图如图5所示,主要组成部分为相位累加器、地址计数器和可读写的波形存储RAM,其中FREQ为频率控制字,Wr_addr为写地址,Rd_addr为读地址。波形存储器的写地址由地址计数器在系统时钟的作用下产生,完成波形幅值的存储;读地址则由相位累加器根据频率控制字输出相位值。相位累加器可看作一个加法器与一个锁存器的级联,加法器输出端与锁存器相连,两个输入端分别为频率控制字K和锁存器输出端的反馈,在系统时钟的作用下,对频率控制字进行累加[7],加法器量满溢出后变为零,相邻两次归零的时间差即为一个周期。

图5 DDS模块原理图

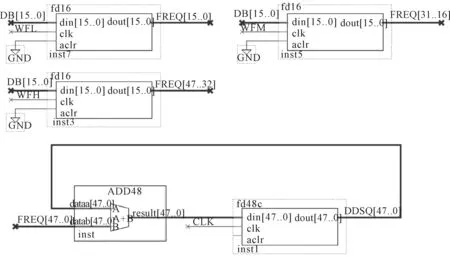

根据式(2),当K的取值为1时,输出波形的频率为系统的频率分辨率,若使系统具备输出较高频率波形的能力,可提高系统的采样频率[8],因此采取100 MHz的时钟频率。若使系统获取较高的频率分辨率,则需增加相位累加器的位数。根据系统的设计需求,为达到1 μHz的频率分辨率,计算得相位累加器的位数至少为47位,为方便数据的传输,取累加器的数据位为48 bit[32]。在数据传输过程中,为减少数据的截断误差,取频率控制字K与相位累加器的位数相同,而输入数据线为16 bit,因此将K值分三次传输,在时钟沿控制下,分别将K值的bit[0-15]、bit[16-31]和bit[32-47]依次锁存。相位累加器模块的逻辑电路如图6所示。

图6 相位累加器模块

相位累加器主要由3个16 bit的寄存器、一个48位的加法器和一个48 bit的寄存器组成。其中16位寄存器分别用于存储频率控制字的高中低部分,在各寄存器时钟信号的控制下,STM32通过FSMC数据总线分时传送频率控制字的部分数据位。得到完成的FREQ之后,加法器将其与寄存器中保存的数据累加,在时钟信号作用下,相位结果再次保存至寄存器中。

3.2 波形存储RAM

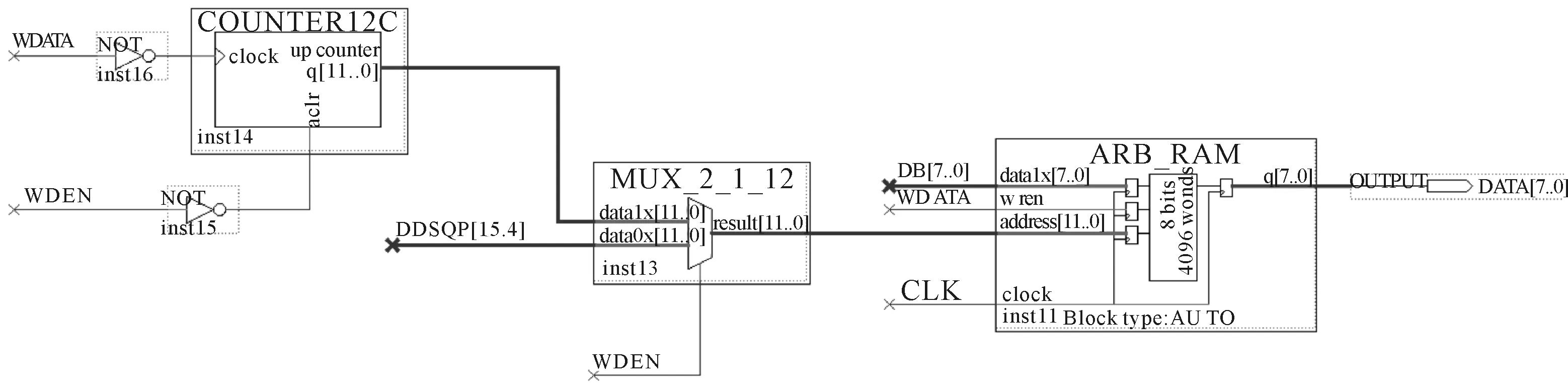

相位累加器输出相位值之后, 作为波形存储RAM的地址值进行查表得到波形幅度值,图7为波形存储RAM的设计。

图7 波形存储RAM

波形存储RAM的写地址由地址计数器在系统时钟的作用下产生,完成波形幅值的存储,读地址则由频率控制字截取得到。由于单端口RAM只有一组地址线和数据线,因此采用二选一数据选择器分时输出读写地址,同时配合RAM中的写使能位工作,在写使能有效时,二选一数据选择器选用写地址,波形数据存入RAM中;写使能无效时,选用读地址,RAM根据地址输出相应的波形数据。

4 系统测试

本次测试主要进行波形种类及系统参数的验证,主要针对任意波形发生器的三个方面进行测试:生成波形种类、频率精度和幅度精度。本次测试采用的仪器为安捷伦公司的4通道数字示波器DSOX2014A,带宽100 MHz,可满足系统最大输出频率为10 MHz的测试要求,每通道最大采样率可达2 GSa/s,可提供更细节的波形数据。

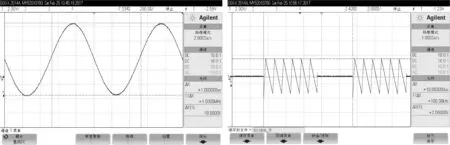

任意波形发生器可生成直流波、方波、指数波、三角波、噪声、正弦波、锯齿波、负锯齿、SINC、猝发波共10种波形,根据系统的输出阻抗为50 Ω,采取的测试方法为任意波形发生器外接50 Ω的测试件,示波器并联测试件并采集波形,图8显示了频率1 MHz,10 Vpp的正弦波和频率100 kHz,2.5 Vpp的猝发波。

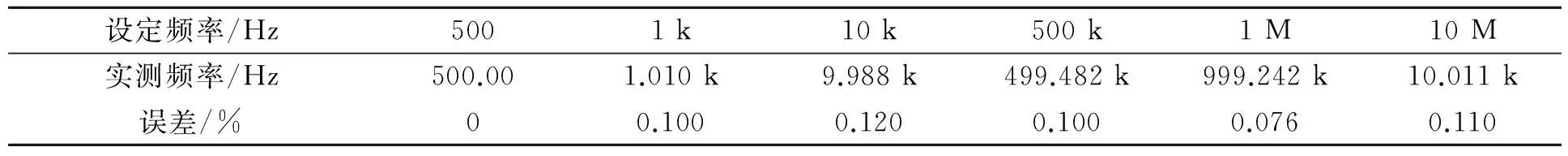

任意波形发生器的波形输出频率的设计指标最大10 MHz,本次测试选取多个频率点,根据实测数据计算得到频率的误差,频率测试结果如表1所示。

表1 频率测试结果

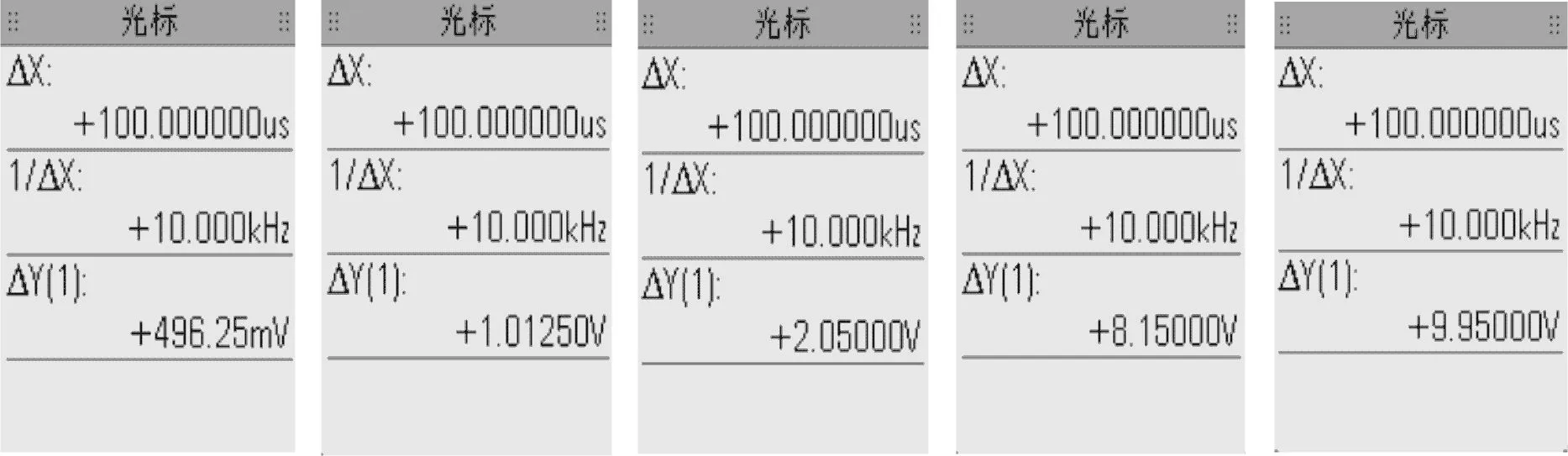

任意波形发生器的波形幅度值的设计指标为最大10 Vpp,本次测试以正弦波为测试对象,选取6组Vpp值:500 mV、1 V、2 V、8 V、10 V,各幅值的测试数据如图8~图9所示,根据测试结果,幅度值误差均控制在1.6%之内。

图8 正弦波与猝发波形测试图

图9 幅度精度测试值

5 总结

笔者在分析了DDS原理之后,提出以可编程逻辑器件实现DDS技术的方案,比较了该方案与其他实现方法的优点所在。本设计基于FPGA+ARM+DAC的硬件平台,实现了DDS技术,其中在FPGA内部完成相位累加器、波形存储RAM的设计,并给出了DA转换电路和滤波器的具体设计,最终实现的任意波形发生器具备响应速度快、频率分辨率高等优点。经测试,系统能够产生正弦波、方波以及猝发脉冲等设计波形,频率和幅度精度也达到了设计要求,实现了便捷实用、性能优良的设计初衷。

[1] 黄振华.基于FPGA函数信号发生器的设计与实现[D].镇江:江苏大学,2009.

[2] 李季.信号发生器发展浅析(上)[J].电子产品世界,2002,19(9):65-66.

[3] 吴昕.信号源的发展和现状浅析[J].科学时代,2010(8):58-59.

[4] 张冠百.锁相与频率合成[M].北京:电子工业出版社,1995.

[5] 徐啸林,田书林,李硕.基于并串转换DDS技术的任意波形发生器采样率研究[J].自动化信息,2010(7):42-44.

[6] 甄军红.AD9708及其在数据采集系统中的应用[J].电子世界,2003(11):44-45.

[7] 黄志林.基于FPGA的并行DDS技术研究[J].现代电子技术,2013,36(7):54-55.

[8] Kazuyuki Wakabayashi, Keisuke Kato, Takafumi Yamada, et al. Low-Distortion Sinewave Generation Method Using Arbitrary Waveform Generator[J]. Journal of Electronic Testing,2012,28(5):641-651.