雷达回波存储设备的信号完整性研究

范国浩, 杨少博, 张艳兵, 马铁华

(1.中北大学 电子测试技术国家重点实验室,山西 太原 030051;2.中北大学 仪器科学与动态测试教育部重点实验室,山西 太原 030051)

雷达回波存储设备的信号完整性研究

范国浩1,2, 杨少博1,2, 张艳兵1,2, 马铁华1,2

(1.中北大学 电子测试技术国家重点实验室,山西 太原 030051;2.中北大学 仪器科学与动态测试教育部重点实验室,山西 太原 030051)

该文设计高速雷达回波存储系统,针对在系统设计过程中可能出现的影响信号传输完整性的诸多因素进行分析,并做出多种预防性措施。从主要器件选型、PCB板布局布线、叠层设计以及在PCB板设计制造中结合IBIS模型与Cadence仿真软件对所遇到的差分对的反射问题进行分析与研究。在重点分析差分传输线理论的基础上选取高速接口处的1组差分对提取拓扑结构,并对其在进行端接匹配前后接收的信号进行分析及眼图仿真。实验结果表明:采用ESD芯片进行端接处理后所接收的眼图波形变得整齐,抖动与尖峰明显减少。目前采取的措施可以确保实际存储设备工作的可靠性,为工程实践提供有益的借鉴。

雷达回波;存储测试;信号完整性;差分对;IBIS模型

0 引 言

雷达技术向高分辨率方向发展,增加了雷达回波的信息量,对雷达数据记录设备的速度提出更高要求,同时对存储设备PCB板的信号传输也提出更高要求[1]。本文研究设计了高速雷达回波信号记录设备,主要针对机载雷达探测其他飞行器飞行中的各种参数并进行采集与加密存储。返回陆地后经高速接口进行数据回读分析。

对于高速电路有两个方面的含义:1)从频率角度考虑,数字电路的频率达到或是超过40~50MHz,且工作于此频率之上的电路占整个系统的1/3。2)考虑信号的上升与下降时间,若某信号的上升时间小于6倍信号传输延时即认为是高速信号[2]。本文所采集的激光雷达回波信号的最大频率为40MHz,采样频率为信号频率的4~10倍,数据采用的是LVDS低压差分形式进行传输。对于高速的雷达回波信号采集存储设备,在PCB板的设计过程中需要对采集、存储、回读过程中信号传输的完整性进行分析,以最大程度保证信号传输的不失真性[3-4]。本文针对此问题在系统设计过程中主要从PCB布局布线、叠层设计、差分对设计等方面进行研究,并对差分对信号提出合理的端接,保证数据传输的完整性。

1 系统结构

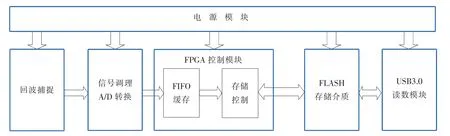

系统结构由回波捕捉与信号调理、主控存储、读数接口和电源等模块组成。回波捕捉与信号调理模块完成有效信号的捕捉、模数转换、外部数据的匹配、隔离等工作;存储模块工作是在主控芯片控制下经数据缓存电路存入FLASH阵列中。读数接口模块用于设备采集后的数据回读;电源模块给其他模块提供稳定、精准的各等级电压。系统结构框图如图1所示。

图1 系统结构框图

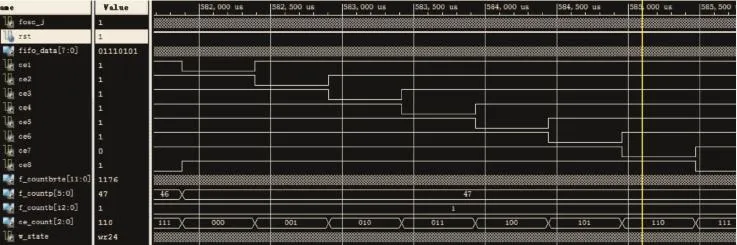

系统上电后各个模块完成复位操作,回波捕捉电路捕捉到有效的回波信号后使系统触发,回波信号经信号调理电路,之后进入模数转换部分。其输出类型为LVDS信号,经接口芯片转换为TTL信号,经FPGA内部调用的FIFO实现高速数据缓冲,并在其控制下存储至FLASH介质中。记录结束后通过USB3.0读数接口将数据回读分析,继而实现了雷达回波数据从采集到高速传输,存储以及回读等功能。数据高速存储使用流水线的方式存入FLASH芯片,系统逻辑控制时序仿真图如图2所示。

图2 系统逻辑控制时序仿真图

2 信号完整性研究

PCB板的设计主要是从狭义的信号完整性(SI)、电源完整性(PI)和电磁兼容性(EMC)3个角度出发[3,5]。从原理图的设计,元器件的封装与布局布线,电路板的叠层与参数等方面统筹协调,综合规划。本存储系统对体积有所要求,导致单位面积PCB板上的元件很多,布局布线的密度也很大。在PCB板的设计制造过程中信号完整性的思想始终贯穿其中[6]。具体的PCB设计过程,如图3所示。

图3 PCB设计过程

2.1 主要器件选型

对于高速系统的设计,对主要器件的选型从高速信号传输角度也需要进行全面考虑。在满足系统设计与成本要求的前提下系统的中央控制模块所采用的可编程逻辑器件为Xilinx公司的Spartan II系列的XC2S50(XCR3256),它拥有1728个宏单元,大大增强了系统的可扩展性。模数转换器选取具有双倍速率低压差分信号输出的 14位 65MSPS的 ADS6142,在速度与性能上都满足设计要求。读数模块中USB芯片为CYUSB3014,另外还加有对接口进行保护的ESD防护芯片。

2.2 PCB板的布局布线

在进行仿真和布线之前要先进行预布局,即按照一般的外形因素、机械限制和惯例预先确定关键元器件的位置。器件的布局决定了布线的大致走向和结构、电源和地平面的分割,以及对EMI和噪声的控制情况[4,7]。PCB布局坚持以下原则:按照信号流动的方向布局各功能模块在PCB板上的位置;在各功能模块中以核心器件为中心,将器件归类布局,尽量使其均匀、整齐、紧凑地围绕着核心器件,并使元器件之间的引线与连线最简化;高频和低频电路相隔离,模拟与数字电路相隔离,且数字器件尽量集中放置以减少走线长度;晶振尽量靠近其驱动器件,高频去耦电容放在芯片电源引脚附近[8]。

设计的 PCB板尺寸为 56 mm×82 mm,高速数据传输系统器件较少,先确定LVDS转换芯片DS92LV090A和USB3.0芯片CYUSB3014的位置,然后依次放置扩展口接插件、FLASH、电源管理芯片、配置芯片,晶振和去耦电容等。在进行前仿真过程中,根据线长和结构优化调整布局。

2.3 PCB板的叠层设计

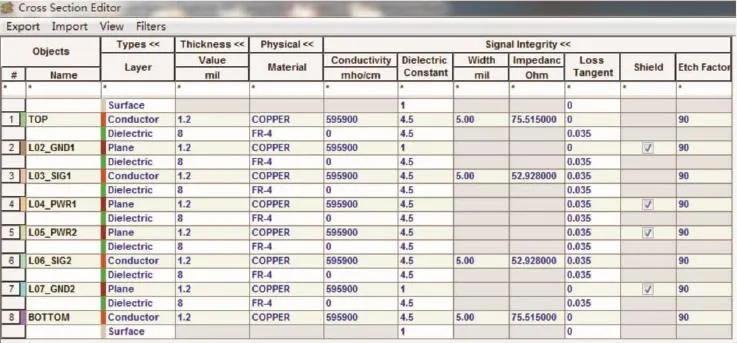

设计合理的PCB叠层可以使系统的EMC性能极大改善,同时会使回路的辐射效应大大减弱。稳定可靠的电源平面为信号提供理想的返回路径,使之减少环路面积[9]。多层板应用于高速数字系统设计中主要考虑其板层结构设计、介质选择和电源/地层的设计。参考有关手册和设计经验,本系统采用的PCB叠层设置如图4所示。

图4 PCB叠层参数设置

系统采用8层PCB设计,总厚度1.67mm。将中间的两个信号层置于地层与电源层之间,顶部与底部的信号层与底层相邻。表层走线为微带线和内层走线为带状线。loss tangent是介质损耗因数,其类型包括表层、信号层、电介质和电源平面4种。信号层和电源/地的材料选择COPPER,厚度设为0.03mm,绝缘层设为FR-4材料,通过改变绝缘层的厚度达到期望的各层阻抗和PCB厚度。PCB顶层和底层的阻抗最终设为75.515 Ω,中间信号层的阻抗设为52.928Ω。

2.4 差分对设计

如今高速数字信号频率大大提高,边沿十分陡峭,互联结构中各种寄生参数效应也越发明显[5],只有把信号从发送端到达接收端的传输看作是消耗一定时间的“动态过程”,把高速电路中的互联结构当作传输线对待,并从电磁波传播的角度来理解信号的传播[10-11]。在时钟频率和噪声隔离要求较高的情况下,常使用差分传输线。在差分互联模式下,成对摆放着两条电压和电流大小相等但极性相反的传输线,如图5所示。两个信号从驱动端出发,到达接收端时根据两信号的数值差判断电平高低。

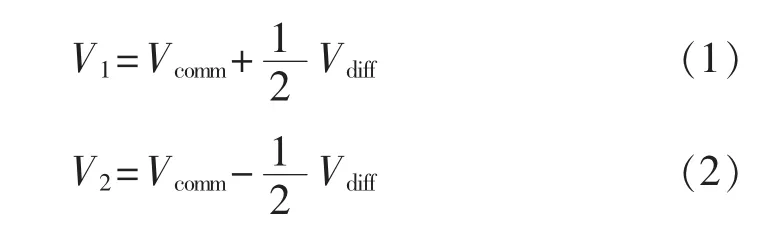

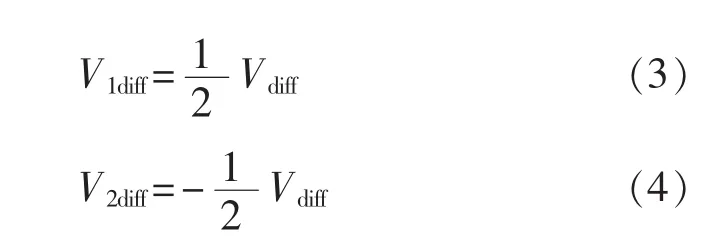

理想时,两信号可用共模分量以及差分分量形式[5]表示:

其中Vcomm表示共模分量,Vdiff表示差分分量。两条信号传输过程的环境是相同的,所以接收端有很好的共模抑制能力,若只考虑其中的差分分量,则两个信号可记为

式中 V1diff、V2diff分别表示第 1个信号和第 2个信号的差分分量,是两条电压相等极性相反的信号线,其每条差分分量的阻抗都是奇模阻抗Zodd。假设由差分分量引起的电流为Idiff,则Zodd可表示为

即定义差分阻抗Zdiff为

差分阻抗(或特性阻抗,两条差分传输线之间的阻抗)为单条传输线对地特性阻抗的2倍[12]。通常,差分对信号间距越近,其特性阻抗越小[13](其他因素保持不变的条件下)。常使用的差分对的特性阻抗为100Ω,有时也用75Ω。

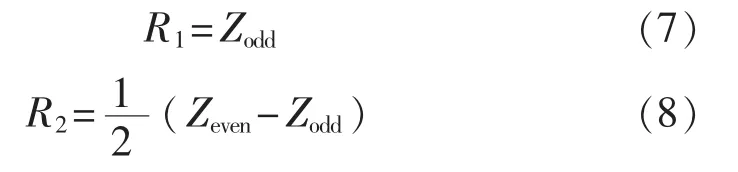

差分对中的两个单端信号传输到传输线末端时,如果没有端接信号可能发生反射,接收端波形可能会产生振铃。对差分信号和共模信号同时端接是减小振铃现象最理想的方式,常用的端接方式有T型和π型端接,如图6所示。

图6 差分对端接方法

图中电阻R1和R2分别为

两个R1串联作用在差分信号上,刚好等于差分阻抗。两个R1并联再与R2串联作用在共模信号上,阻值为Zeven/2,恰好为共模阻抗的值。

π型端接中电阻R1和R2分别为

那么差分信号感受到的阻抗为R1//2R2=2Zodd,共模信号感受到的阻抗为R2/2=Zodd/2,这两种方法对差分信号和共模信号皆有端接作用。

图7 USB3.0接口与CYUSB3014之间拓扑结构

差分对设计的一个基本要求就是尽量保持等长平行布线,如果绕线处不得不改变间距,那么尽量在小范围内改变间距,这样做的目的是使差分对两条传输线的延时相等,使差分信号畸变变小,并减少共模噪声引起的抖动。由于差分信号在传输过程中,两条路径上遭遇的噪声干扰完全一样,这样其相互产生的电磁场将相互抵消,所以比单端传输在减小地线回路噪声与外部噪声上更有优势。需要注意的是,在差分对与单端线间距较小的情况下,单端线对差分信号的串扰噪声依然较大,因此,即便是使用差分传输,最有效的减小串扰的方法仍然是尽量拉开差分对与攻击信号的间距。对于差分对中一条走线的返回电流路径,参考平面中的返回电流占总电流的90%左右,另一条走线上的返回电流约占10%,因此参考平面对于差分对同样重要。

综上,针对差分对特性阻抗、差分互联的反射与端接、串扰等的分析,进行差分对设计。根据相关数据手册建议,信号线阻抗为90Ω(±7%)的差分值[12]。本设计中差分对的特性阻抗设为90 Ω,线宽设为0.28 mm,走线间距设为0.2 mm,同时在布线时将差分信号线完全与接地层邻近,尽量远离其他信号线,减少串扰。本文中差分对设计的重点在于USB接口处,其中USB接口处差分信号接收端反射现象并不明显,因此在USB3.0接口与CYUSB3014之间接入ESD芯片,防止静电干扰,减少外部噪声。

3 仿真实验

3.1 SI模型分配

图8 波形及眼图仿真

在进行仿真前需要对元器件进行模型分配,这里采用(input/output buffer information specification,IBIS)模型仿真。只有IC类有源器件能够分配IBIS模型,DISCRETE无源器件和IO类输入/输出器件没有IBIS模型。IBIS定义引脚与哪一个缓冲模型相关,这里采用手动分配模型方式,分配给元器件的信号模型名不必与Allegro元器件名匹配[14]。如果模型库中没有某个器件的IBIS模型,则需要亲自创建,确定该器件的引脚寄生参数和各个引脚的输入输出特性。

USB3.0接口与CYUSB3014之间的3对差分信号线起着连接USB3.0芯片与上位机的关键作用,这些差分对信号能否准确传输对整个高速数据存储系统起着重要作用,因此必需考虑这些差分信号在传输过程中的完整性问题。此处选取USB3.0接口处的SSRX+和SSRX-差分对提取拓扑结构,并按照前面分析进行相关参数设置,拓扑结构如图7所示。

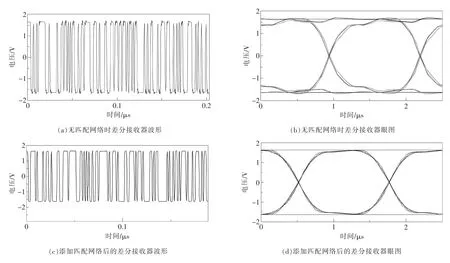

3.2 眼图仿真

眼图通过余晖方式积累叠加,然后显示采集信号的比特位[9]。对高速差分互联通常使用眼图来评估信号的传输,从“眼睛”睁开的大小(高度及宽度)能看出接收信号的误码率相对大小,“眼睛”睁开得越大,接收的出错概论越小。下面利用Cadence软件的Allegro PCB SI部件对差分对进行仿真分析。

图 7拓扑结构中,USB3.0接口为驱动端,CYUSB3014为接收端。对驱动端激励信号进行设置,激励形式为Custom,频率为400 MHz,采用时钟同步方式。传输数据设为1024字节随机数。设置好参数后,开始仿真。图8为在添加ESD芯片SP3010-04UTG前后的仿真结果图。在仿真结果中只显示CYUSB3014接收到的差分信号,图8(a)、图8(b)中接收器所接收到的信号尖峰明显,说明所受到的抖动与外部噪声对信号有较大干扰,眼图波形失真严重。而进行端接匹配之后,如图8(c)、图8(d)所示,无论从接收到的波形的平整程度还是眼图的优化结果都可以明显观察到尖峰与抖动减小,足以说明信号得到完整的传输。

4 结束语

本文设计了高速雷达回波信号存储设备,针对在系统设计过程中可能出现的影响信号传输完整性的诸多因素进行分析。主要包括核心器件的选型,PCB板的布局布线,叠层以及差分对的设计。在整个PCB板的设计制造过程中信号完整性的思想始终贯穿其中。在重点分析差分传输线理论的基础上选取高速接口处的1组差分对提取拓扑结构,并对该差分对在进行端接匹配前后进行分析及眼图仿真。实验结果表明:采用ESD芯片进行端接处理后波形变得整齐,抖动与外部噪声明显减少,在PCB设计过程采用的多种预防性措施保证系统传输信号的完整,使存储设备稳定工作。

[1]任敏.基于FPGA的双通道机载数据存储系统设计[D].太原:中北大学,2015.

[2]王泽强.高速电路之信号回流路径分析[J].现代电子技术,2013,36(1):155-157,160.

[3]周润景,苏良碧.Cadence高速电路板设计与仿真[M].4版.北京:电子工业出版社,2011:97-105.

[4]王雪茹.信号完整性对雷达对抗系统的影响[D].西安:西安电子科技大学,2014.

[5]郁昊,叶勇.基于雷达处理机高速信号的信号完整性设计[J].测控技术,2012,31(3):128-130,134.

[6]杨少博,裴东兴,岳孝忠.高速数据采集系统中USB3.0数据传输接口设计[J].电子器件,2015,38(4):912-916.

[7]刘定坤.差分对对信号完整性的分析[J].电子制作,2013(11):162.

[8]李小荣.高速数模混合电路信号完整性分析与PCB设计[D].杭州:杭州电子科技大学,2010.

[9]王祥.信号完整性在高速PCB设计中的应用[D].上海:复旦大学,2013.

[10]ZHOU S L,GUAN Y L,TANG X K.Signal integrity analysis of high-speed signal connector USB3.0[J].Advanced Materials Research,2013(760):320-324.

[11]陈兰兵.Cadence高速电路设计:Allegro Sigrity SI/PI/EMI设计指南[M].北京:电子工业出版社,2014:171-178.

[12]沈立,朱来文,陈宏伟,等.高速数字设计[M].北京:电子工业出版社,2010:213-227.

[13]于争.信号完整性揭秘:于博士SI设计手记[M].北京:机械工业出版社,2013:91-99.

[14]田广锟,范如东.高速电路PCB设计与EMC技术分析[M].北京:电子工业出版社,2011:41-49.

(编辑:李妮)

Research on signal integrity of radar echo storage equipment

FAN Guohao1,2,YANG Shaobo1,2,ZHANG Yanbing1,2,MA Tiehua1,2

(1.National Key Laboratory for Electronic Measurement Technology,North University of China,Taiyuan 030051,China;2.Key Laboratory of Instrumentation Science&Dynamic Measurement of Ministry of Education,North University of China,Taiyuan 030051,China)

A high-speed radar echo storage system was designed and in view of the many factors that may affect the signal transmission integrity in the system design process,a variety of preventive measures were taken.From the main component selection,PCB locating and wiring,stack design and PCB design and manufacturing,IBIS model and Cadence simulation software were combined to analyze and study the problems of signal integrity differential pair reflection encountered in the radar echo storage system.On the basis of analysis on difference transmission line theory,a group of differential pair at high-speed interface was selected to extracts its topological structure.Analysis and eye pattern simulation were conducted for the signals received before and after termination matching.Experimental results show that using ESD chip for termination processing can reduce the jitter and external noise and neat the eye pattern.These measures can ensure reliability of the actual storage device and provide a useful reference for engineering practices.

radar echo;storage test;signal integrity;difference pair;IBIS model

A

:1674-5124(2017)02-0139-06

10.11857/j.issn.1674-5124.2017.02.028

2016-05-10;

:2016-08-30

范国浩(1991-),男,山西汾阳市人,硕士研究生,专业方向为智能仪器与动态测试。

张艳兵(1973-),男,山西运城市人,副教授,硕士生导师,研究方向为动态测控与智能仪器、计算机控制。