基于FPGA与STM32的低功耗数据采集系统

林 伟 王毅男

(上海应用技术学院电气与电子工程学院,上海 201418)

基于FPGA与STM32的低功耗数据采集系统

林 伟 王毅男

(上海应用技术学院电气与电子工程学院,上海 201418)

设计了基于低功耗、低成本的FPGA与STM32芯片的数据采集系统。系统使用单片SDRAM实现“乒乓”缓存操作,增强数据采集的连续性。采用改进的SPI通信方式完成FPGA和STM32之间数据与命令的传输,实现了通过控键输入实时、动态地配置系统采样参数。软件仿真和板上实测系统的采样精度14bit,采样速率80MS/s。

数据采集 FPGA STM32 SPI

在实现工业自动化测控的过程中,通常需要对被测对象的一些参数进行采集、分析和处理。在很多应用场合,都需要设计并应用高速数据采集系统,以在极短的时间内获取大量数据[1]。随着数据采集系统的最新发展,系统并/串行总线接口技术、系统通信的新技术也得到了不同程度的发展。数据采集模块已成为测量控制领域的重要组成部分,目前国内外常用的数据采集器和不同采集模块的设计都有各自的特点和存在的问题[2,3]。在便携式仪器仪表中,对数据处理速度的实时性、连续性要求更高。传统的数据采集卡较为昂贵,而且使用灵活性较差。为此,设计了高速ADC、FPGA与STM32组合的数据采集系统,在芯片选型上以高性能、低功耗、低成本为原则。

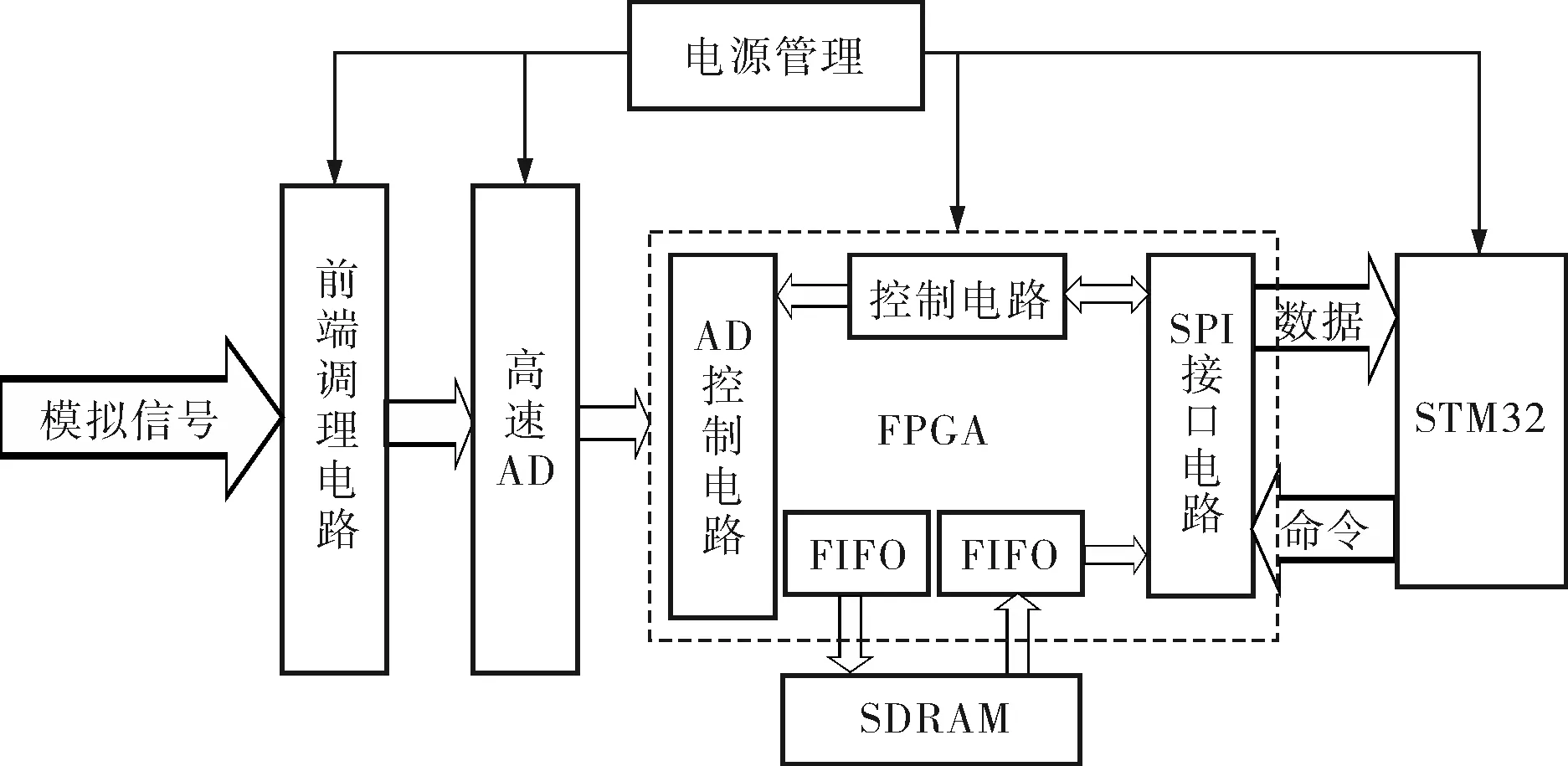

图1为数据采集系统的总体结构,主要由电源、模拟信号调理运放电路、模数转换电路、FPGA及其外设存储器、STM32及其外设键控电路组成。模拟信号经过前端电路的调理、运放后传输给ADC,完成模数转换,将数字信号输入FPGA内嵌的FIFO中。FPGA作为ADC和SDRAM的控制器,控制整个系统的数据流,再将FIFO中的数据传输到外设的SDRAM中,实现了大数据量的缓存,解决了FPGA片上内存不足的问题。再通过串行外围接口(Serial Peripheral Interface,SPI)将数据传给STM32处理。FPGA不但适合做高速数据接口和逻辑控制单元,而且有很强的信号处理能力,可以协助主处理器完成信号的预处理,能保证信号采集的精度与速度。STM32作为主控制器,内嵌ARM Cotex-M3内核,可以实时处理信号,也可以通过自带的USB模块将数据高速地传输到上位机,实现更为复杂的处理。

图1 数据采集系统结构框图

2 FPGA系统

FPGA选用Cyclone IV系列的EP4CE10E144-C8N芯片,这是一款45nm的低功耗、低成本的FPGA。内部含有10 320个逻辑单元、46个M9K的Block、414kbit/s嵌入式存储、两个通用PLL(每个PLL最多可以输出5路不同频率的时钟,完全满足系统设计的需求)。FPGA主要响应主控制器STM32的命令,完成ADC的控制配置和数据流的控制。

2.1ADC电路及其控制器

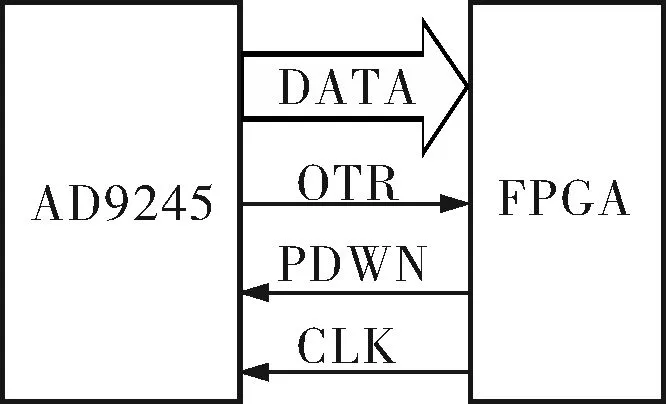

设计选用14bit、80MS/s的AD9245作为ADC芯片,3V单电源供电功耗360mW。信号差分输入,保证了系统的信噪比。AD9245的电路设计如图2所示。

图2 AD9245电路设计

AD9245通过数据总线DATA将14bit数字信号传输给FPGA,通过OTR标志告知FPGA数据超量程范围。FPGA为ADC提供工作时钟,保证数据的同步性,也简化了设计的复杂度。但是,FPGA与ADC的时钟相位仍然存在差异。系统数据传输过程中如果存在相位差,会引起系统亚稳态等问题的发生[4,5]。因此,FPGA内部的寄存器中对模数转换器输出数据通过系统时钟采样后进行两次寄存,以降低亚稳态继续传播下去的概率,保证数据传输的可靠性。

2.2单片“乒乓”缓存

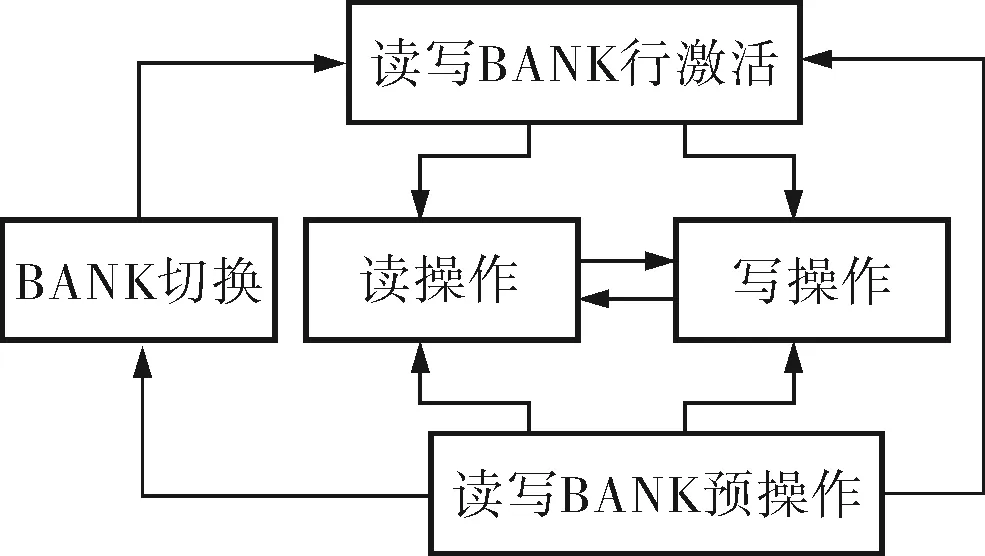

在实时数据采集系统中,为了保证数据的稳定性与连续性,一般使用存储器“乒乓”法[6]。“乒乓”是指通过控制器对两片存储器做读写操作,被写入的存储器写满时,由控制器切换该存储器的工作状态。为了节约成本,降低功耗,系统采用单片SDRAM完成“乒乓”设计。SDRAM只有一组地址总线与数据总线,所以无法像两片存储器那样同时进行读写操作。设计采用分时方法将读写操作分开控制,在控制器中设计一个工作指令计数器,通过计数标志来指示控制器切换读写操作。配置适当的SDRAM工作时钟和计数器的设定值即可实现读写操作的连续切换[7,8]。SDRAM的工作状态转移如图3所示。

图3 SDRAM的工作状态转移

初始化SDRAM后,往SDRAM的1、2BANK写入第一组数据,写完以后进入“乒乓”操作,这时,SDRAM的1、2BANK开始作为读数据缓存,而3、4BANK开始作为写数据缓存。第一步执行读数据缓存的行激活操作,然后开始读取数据,在开始读数据操作的同时开启指令计数器,每当进入下一条新的指令动作,指令计数器的计数就自动加一,执行行激活命令与预充电命令时不做加一动作,当计数到达配置的设定值时就控制切换到写数据状态,并且将指令计数器清零。进入写数据状态后,先判断数据缓存区的行激活命令是否已经执行,如果没有,先完成此操作,然后再开始写数据。写数据开始后,同样执行指令计数器的操作,完成状态切换。像这样反复切换读写操作直到读完一组数据或者是写完一组数据。当读完一组数据时,马上判断在写缓存区域中,一组数据是否写好,如果写好,就立刻切换BANK的读写工作状态。反之,控制器立即进入写数据状态,并且不再切换为读数据状态,保持在写数据状态直到写好一组数据,才进入切换读写BANK的工作状态。如果是写好了一组数据,处理方式与读完一组数据的情况相同,应该先判断在读数据缓存中是否已经读完一组数据,然后依照获得的判断结果进行处理,最后再进入切换读写BANK的状态。在BANK的读写切换状态中,SDRAM的3、4BANK作为读数据缓存,1、2BANK切换为写数据缓存。重复执行以上流程,便实现了单片SDRAM的不同BANK间的“乒乓”操作。

SDRAM芯片选择HYNIX H57V51262GTR芯片,512MByte存储空间,工作时钟100MHz,通过使用Quartus II软件自带的Signal Tap II(嵌入式逻辑分析仪)配合系统设计的硬件采集板卡对BANK的切换和读写操作进行观测。当读数据操作完成,判断写数据操作也已经完成,于是切换BANK读写状态,配置写数据缓存地址。

2.3FPGA与STM32通信

串口RS232通信速度过慢,无法保证系统采样的实时性与连续性;USB协议比较复杂,FPGA内部完成USB接口过于困难,外设USB接口芯片又增加了功耗、成本和电路板的体积;并口总线连接方式虽然数据传输速度快,但是资源利用过大,而且亚稳态现象严重。综合成本、稳定性及设计复杂度等因素,设计采用改进的SPI方式完成FPGA与STM32的通信[9]。

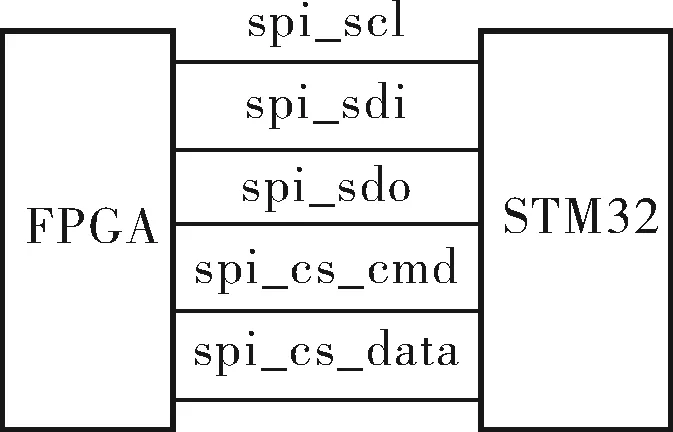

SPI为主从式接口,该模式的优点是可以有多个从器件。SPI包含MOSI、MISO、SCLK和CS共4个接口。实际应用中,主器件可能需要与多个从器件进行数据传输,理论上可以增加多根片选使能信号。

系统设计的SPI通信模块针对多个从器件需要多根片选的问题进行了改进。图4所示为SPI通信方式连接图。SPI通信模块的主器件是STM32,从器件是FPGA。SPI通信模块引脚定义如下:通信时钟spi_scl、主器件数据传输线spi_sdi、主器件数据输入线spi_sdo、模块选择片选线spi_cs_cmd和数据发送片选线spi_cs_data。其工作原理为:模块选择片选信号spi_cs_cmd低电平有效后,先利用主器件数据传输线spi_sdi发送8位模块选择信号(可以选择256个模块通信)。模块选择信号发送完,数据发送片选线spi_cs_data低电平有效后,利用主器件数据传输线spi_sdi发送16位数据到选中模块。

图4 SPI通信方式

FPGA接收数据时,首先模块片选信号spi_cs_cmd变成低电平,等到通信时钟spi_scl上升沿到来时,FPGA通过主器件数据传输线spi_sdi,利用左移移位寄存器读取模块选择信号,8个通信时钟后,即可读取完模块选择信号,并存储在8位模块选择寄存器中,同时模块选择信号接收结束标志位产生高电平。同理,在数据发送片选线spi_cs_data为低电平的情况下,等到通信时钟spi_scl上升沿到来时,FPGA通过主器件数据输出线spi_sdi,利用左移移位寄存器读取数据信号,16个通信时钟后,即可读取完数据信号,并存储在16位数据接收寄存器中,同时数据接收结束标志位产生高电平。当信号接收结束标志位和数据接收结束标志位为高电平时,模块选择寄存器和数据接收寄存器才是有效的。

FPGA发送数据时,首先数据发送片选spi_cs_data为高电平时,等到通信时钟spi_scl下降沿到来,将FPGA要发送的数据存入数据发送寄存器中;当spi_cs_data为低电平时,等到spi_scl下降沿到来时,数据发送寄存器通过左移移位寄存器,从主器件数据输入线spi_sdo发送数据给单片机,经过16个通信时钟后,数据发送完毕。

3 STM32系统

选用32位微控制器STM32F103ZET6,内部嵌有ARM Cotex-M3内核,最高工作时钟72MHz,在运行速度、功率消耗及稳定性等功能特性方面都比较强大。其内部集成有3个SPI控制接口,SPI最高通信速率可以达到36Mbit/s,完全可以与FPGA实现高速数据、命令通信,并配合控键完成参数配置[10]。

3.1FPGA控制模块

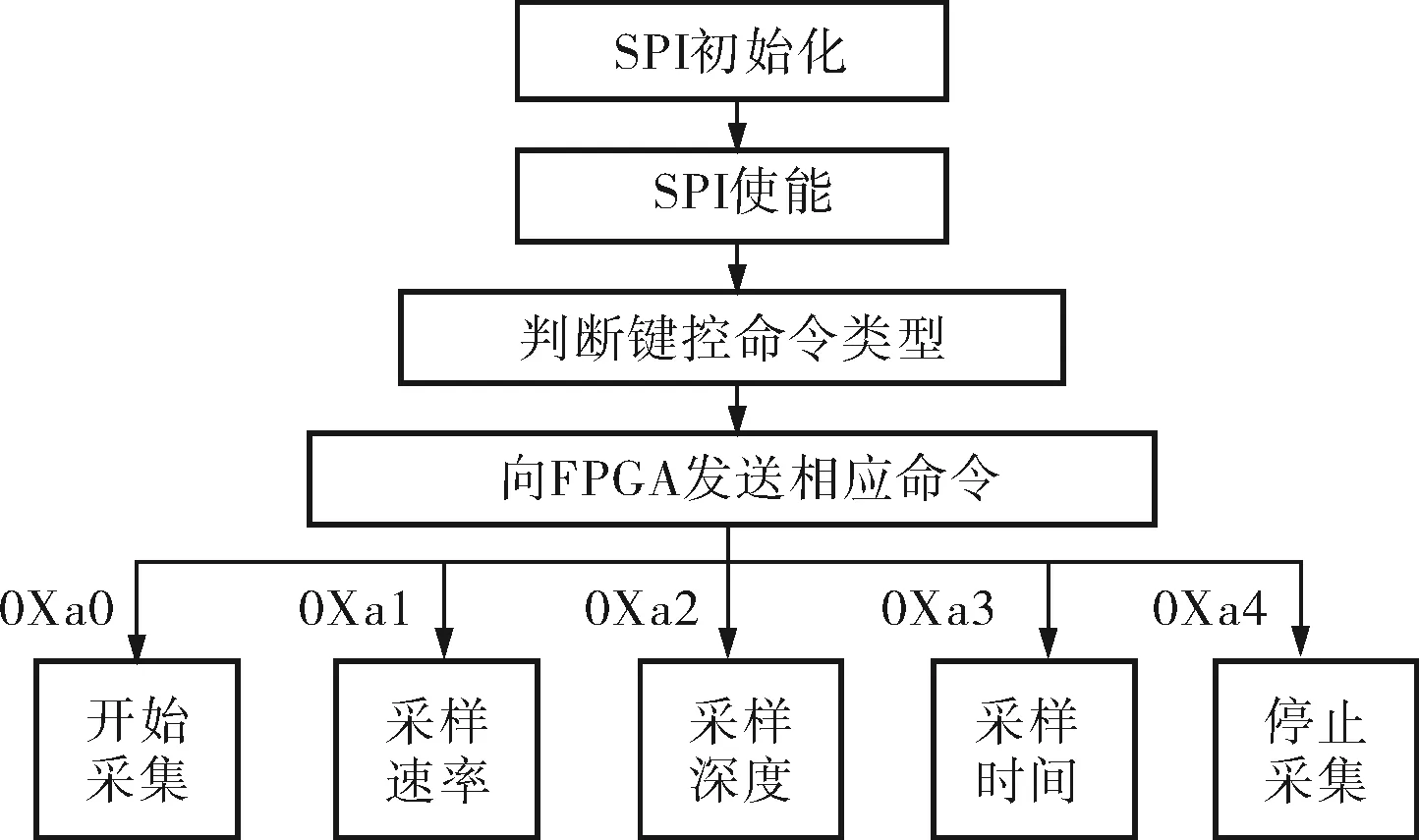

FPGA控制模块实现STM32对FPGA的实时控制,以动态方式配置采样参数,如采样频率、采样深度及采样时间等。同时,接收FPGA传输回来的信号数据和命令标志。 图5所示为动态配置采样参数的流程。首先,初始化并使能SPI接口,然后判断键控命令,并先将命令标志通过SPI接口发送给FPGA,再发送调节参数值。FPGA收到SPI数据先进行译码,解析命令类型,选定寄存器,根据再次接收的数据信号重新配置该寄存器。例如:当FPGA收到0Xa1,经过译码就得知需要重新配置采样速率寄存器,判断再次收到数据为正确格式的数据信号,即将采样速率寄存器配置为该数值。

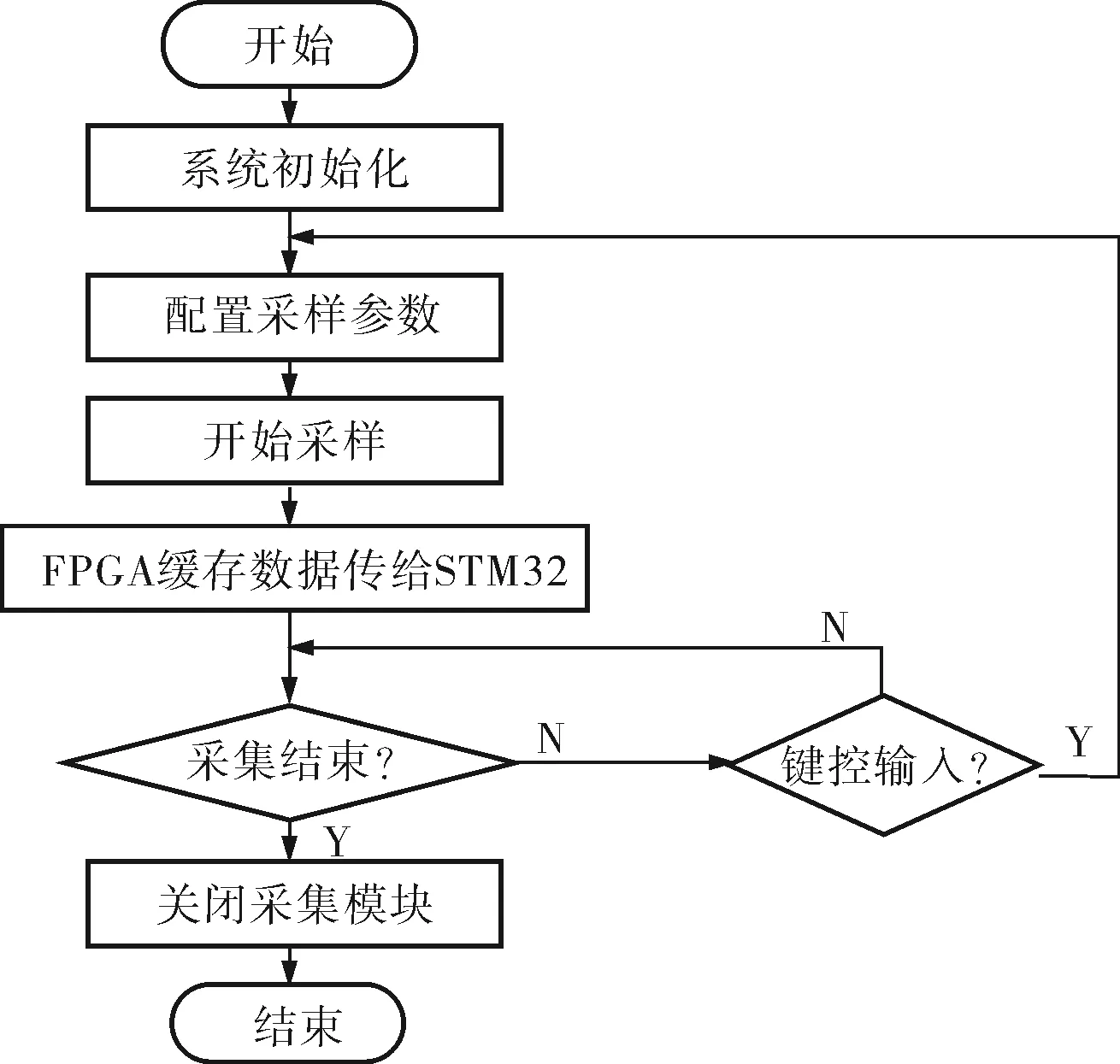

3.2采样系统工作流程

采样系统的整体工作流程如图6所示。系统上电后,STM32开始进行整个系统的初始化设置,初始化SPI接口、外部控键,配置FPGA采样参数,配置AD9245的工作模式。初始化和配置参数完成后,系统处于命令等待状态,当收到开始采样信号之后,通过SPI接口将采样命令传给FPGA,FPGA接到该命令后,控制ADC开始采样,同时实时地将采集的连续数据信号传给STM32。同时,系统进入命令检测等待状态,当FPGA收到停止采样信号就关闭采集模块,完成单次采样。当没有收到停止信号,就检测采样参数配置的键控输入,STM32检测到键控,便将命令信号通过SPI接口通知FPGA停止读写操作,重新配置采样参数,使用新参数进行数据采集,并重复上一轮操作。

图5 动态配置参数流程

4 系统测试

测试FPGA和STM32使用SPI方式的通信速度。SDRAM的工作时钟为100MHz,FPGA的工作时钟可以达到200MHz,所以SPI的数据传输速度决定整个系统的数据吞吐能力。在STM32的SPI通信模块中设置一个定时器,在开始从FPGA读取数据时开启该定时器,在读完N个数据后关闭该定时器,通过仿真软件查看该定时时间的计数值M,根据N和M的值即可估计SPI的传输速度。经过测试,STM32的SPI时钟为18MHz、FP-GA的系统时钟为100MHz时,测得SPI的通信速度为3.975Mbit/s;当STM32的SPI时钟为36MHz时,测得SPI的通信速度为6.565Mbit/s。无论在实时处理,或者需要上传PC的工作情况下,该速度都是够用的。

图6 采样系统工作流程

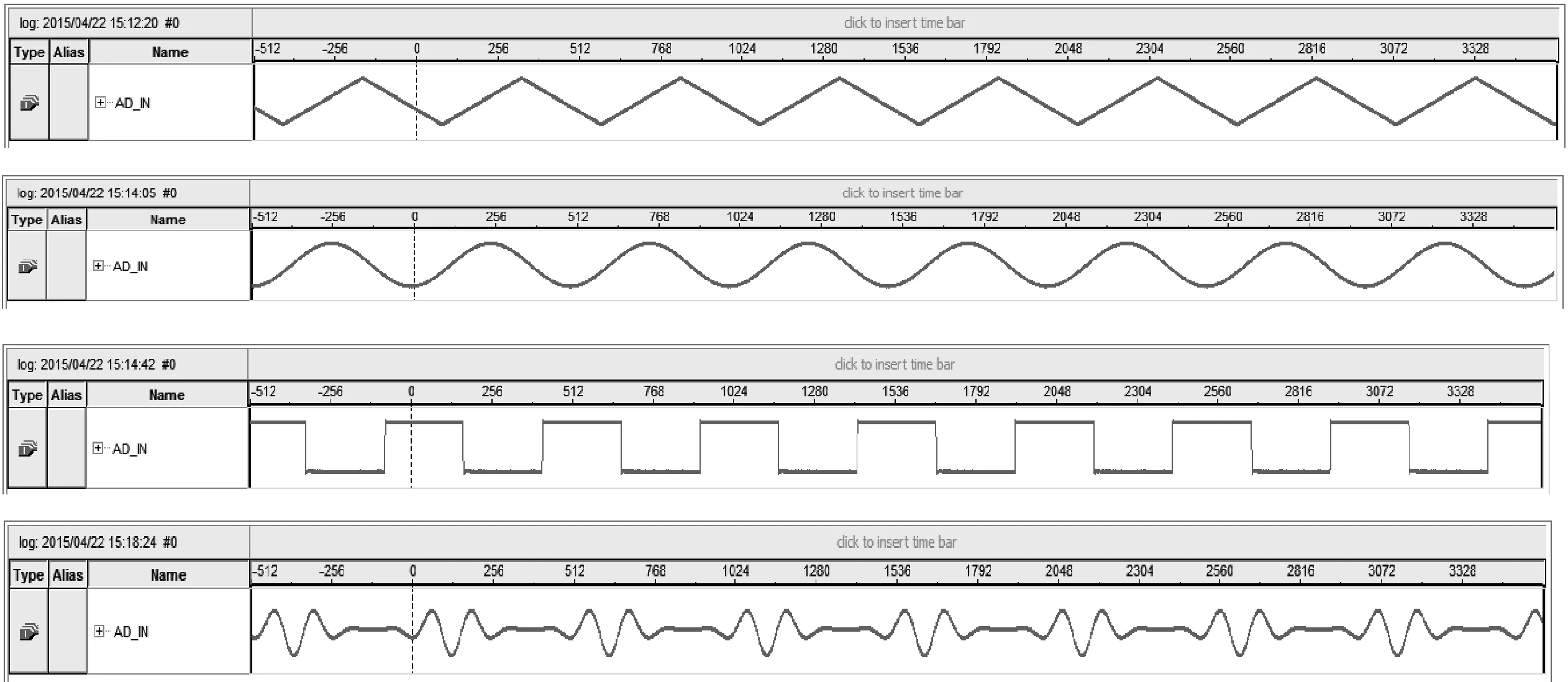

系统测试使用RIGOL DG1022信号发生器,分别输出频率为100kHz、峰峰值为5V的三角波、正弦波、方波和高斯脉冲波,配置AD9245以50MHz的速率进行采样,通过嵌入式逻辑分析仪得到输出到STM32端SPI接口的波形数据如图7所示,得到的采样数据连续且稳定。

5 结束语

采用FPGA与STM32设计了功耗低、成本低、体积小的数据采集系统。使用单片SDRAM的“乒乓”存储式设计增强了系统的存储能力和数据采集的连续性。使用改进式的SPI方式完成FPGA与STM32的通信,实现了数据采集参数的动态、实时化配置。数据采集系统操作简单、灵活性强、使用范围广,可以满足电子、工业领域中对信号采集的精度、速度和实时处理的要求。FPGA有强大的数据处理功能,可以利用FPGA进行数据的预处理,STM32也内嵌了丰富的外设接口,所以设计的数字采集系统可应用于不同的领域,通过软件设计即可满足工作需求,有很强的推广应用价值。

图7 嵌入式逻辑分析仪仿真曲线

[1] 黄志文,邵平,扈晓兰.基于FPGA的PXI高速数据采集系统设计[J].化工自动化及仪表,2010,37(5):60~63.

[2] 刘薇,张彦军,郑燕露,等.基于FPGA的多通道高精度采集传输系统的设计[J].化工自动化及仪表,2011,38(3):335~338.

[3] 李伟,刘齐飞,马景兰,等.基于USB存储技术的管道定位数据采集系统[J].化工机械,2014,41(5):618~622.

[4] 常高嘉,冯全源.基于FPGA的高速数据采集系统的设计与实现[J].电子器件,2012,35(5):615~618.

[5] 丁海飞,王红亮,张会新,等.基于ADS8365的多路数据采集存储系统设计[J].化工自动化及仪表,2012,39(1):81~84.

[6] 马培娇,张宇光,姚永兴,等.高速大容量存储系统的关键技术实现[J].化工自动化及仪表,2011,38(7):869~872.

[7] 张文涛,王琼华,李大海,等.实时视频采集系统的SDRAM控制器设计[J].现代电子技术,2009,32(20):57~59.

[8] 杨海涛,苏涛,巫幪.基于FPGA的SDRAM控制器的设计和实现[J].电子科技,2007,(1):8~12.

[9] 王珏文,金伟,蔡一兵,等.基于FPGA的SPI总线接口的实现[J].现代电子技术,2010,33(14):102~104.

[10] 马宗骥,李佩玥,章明朝,等.基于FPGA+ARM的数据采集系统设计[J].化工自动化及仪表,2012,39(9):1187~1189.

TH865

B

1000-3932(2016)02-0210-05

2015-05-18(修改稿)