延时消去滤波SRF-PLL方法

谢门喜,朱灿焰,杨勇

(苏州大学智能结构与系统研究所,江苏 苏州 215131)

延时消去滤波SRF-PLL方法

谢门喜,朱灿焰,杨勇

(苏州大学智能结构与系统研究所,江苏 苏州 215131)

并网型电力电子变流设备需要实时精确检测电网电压的相位以实现同步。对同步旋转变换锁相方法(SRF-PLL),分析了当三相电网电压不平衡时,Park变换鉴相输出信号特征,指出二倍频扰动引起相位偏差信息不准确,在SRF-PLL环路内应用延时消去滤波滤除该扰动,能使得锁相系统精确追踪正序分量。数字仿真表明,该方法稳态精度高,过渡过程快,计算量小,以TMS320F28335控制器实现了该算法,测试波形验证了正确性和有效性。

锁相环;不平衡电压;延时消去滤波;数字信号处理器

同步旋转坐标锁相方案(synchronous reference frame phase-locked loop,SRF-PLL)是一种流行的实用化方法,其结构包括3个部分:鉴相器将三相电压信号利用Park变换检测相位偏差;环路滤波PI调节器滤除相位偏差中的高频成分;积分型振荡器利用偏差稳态量计算相位信息,通过闭环调整,直到偏差为恒定值,输出信号实时跟踪输入信号。当三相电网电压平衡时,鉴相器输出为直流成分,SRF-PLL中的环路滤波器取值可设计为高带宽系统,获得较快的动态响应和足够滤波性能[1]。实际电网系统,由于负载不对称及动态投切,经常出现三相电压不平衡状态,在这种情况下,锁相同步环节应能追踪正序分量相角[2]。

1 不平衡电压鉴相器输出信号特征

忽略零序分量,不平衡的三相电压可表示为

式中:V+为正序分量的最大值;V-为负序分量的最大值;φ+,φ-为初相位;ω为基波角频率,ω=2πf=2π·50 rad/s。

利用clark变换:

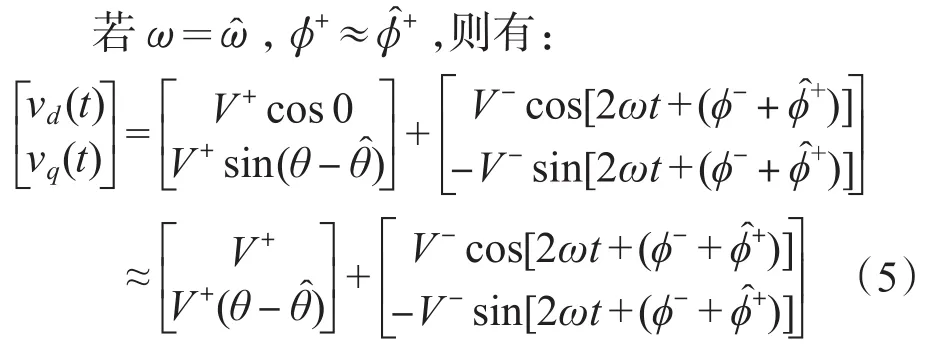

再利用Park变换:

式(5)表明,abc系下的负序分量在dq系下表现为二倍频扰动,其幅度为负序分量的最大值。为利用SRF-PLL方法准确检测到正序分量相角,适应电压不平衡,需要对鉴相信号滤除二次扰动分量,只保留反映相位偏差的直流分量,再进入后续模块,如图1所示。

图1 滤波器的配置Fig.1 Filter configuration

2 延时消去滤波

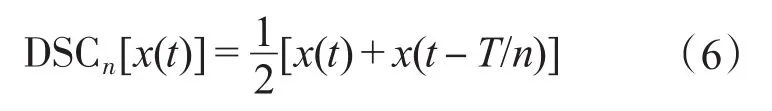

延时消去滤波(delayed signal cancellation)在时域中的表达式为[3]

式中:x(t)为要被滤的信号;T为基波周期,T= 0.02 s;n为延时因数。

该式表明,DSCn运算将当前信号与T/n时间段之前的信号相加后取一半,其频域传递函数为[4]

式(7)表明,DSCn运算等效滞后环节,其时间常数为

图2 DSC4滤波器的频率响应Fig.2 Frequency response of DSC4

数字化控制中,若采样频率为10 kHz,1个电网周期采样200个点,有:

DSC4运算需缓存前50个点,式(7)离散化表达为

其中,x(k)为x(t)的当前采样值,Z变换为

式(9)表明,实现DSC4运算需50个缓存器、1次加法运算、1次乘法运算。

在图1中filter的位置,应用DSC4运算,滤除鉴相器中的高次扰动量,构成DSC-SRF-PLL,可使锁相系统适应电网电压不平衡状况。此外,由于DSC4在2nd,6th,10th,…处衰减为0,该滤波器可适应电网电压含3th,7th,11th,…谐波污染的情况。

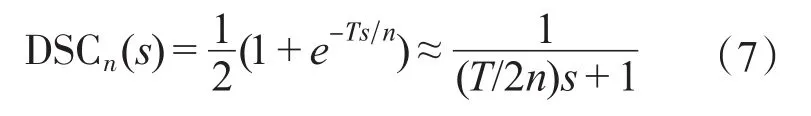

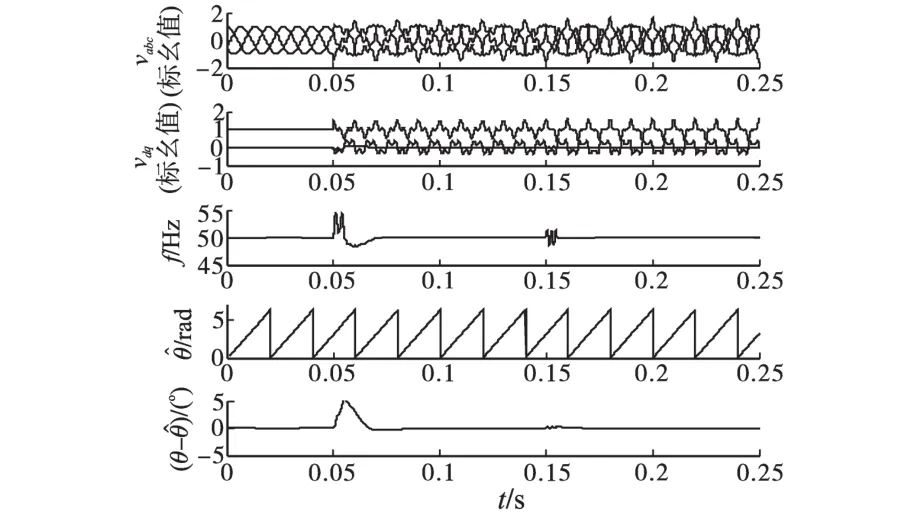

3 数字仿真

采用Matlab/Simulink建立数字仿真模型,并验证DSC-SRF-PLL的有效性。图3给出了电压不平衡情况下的仿真结果。波形从上往下依次为三相电压频率检测值相角检测值检测偏差初始状态三相电压平衡,在 0.05 s时刻,va突增至1.2(标幺值),vc突降为0,此时,vd与vq出现二倍频的振荡分量,滤波后经过约1个电网周期,相角偏差调节至O,且超调小于5°,频率超调小于3 Hz。在0.15 s时刻,va突降至0.8(标幺值),vc恢复至0.8(标幺值),不对称程度减弱,二倍频振荡分量幅度减小,系统仍能快速实时跟踪正序分量va。

图3 不平衡仿真结果Fig.3 Simulation results under unbalanced input

图4给出了电压谐波污染情况下的仿真结果,初始状态三相电压平衡,在0.05 s时刻,vabc加入3th,7th谐波,幅值分别为0.3(标幺值),0.2(标幺值)(相对于基波),系统经过2个周期的过渡后进入稳态,频率超调约4 Hz,相角超调约3°。0.15 s时刻,vabc增加0.1(标幺值)的11th谐波,由于DSC4的针对性滤波作用,稳态误差为0。

图4 谐波污染仿真结果Fig.4 Simulation results under distortion input

4 实验结果

以TI公司浮点型TMS320F28335为核心,在CCS开发环境下,采用C语言编写了软件实现DSC-SRF-PLL。信号发生器模拟电网电压不平衡、谐波状况,该信号经调理后送入F28335的12位AD模块转换为数字量,芯片内定时器产生频率为10 kHz的采样脉冲驱动中断程序运行,算法每0.000 1 s执行1次。对于式(3)中的三角函数,调用优化后的浮点运算库直接实时计算。PI调节器采用增量式结构以减小高速运算中的累计误差,DSC4采用滑动窗,每次中断进行数据更新。

图5给出了不平衡实验测试结果。图6给出了谐波实验测试结果。可以看出,在这两种故障状况下,系统均能成功跟踪基波分量。

图5 不平衡实验结果Fig.5 Experimental results under unbalanced input

图6 谐波实验结果Fig.6 Experimental results under distortion input

5 结论

在环路内应用延时消去对鉴相信号滤波,使得SRF-PLL方法在电网电压发生严重不平衡和特定的谐波污染状况下,有效锁定正序分量相位,数字化实现简单,计算量小,暂态响应速度适用于大多数应用场合。

[1]Chung Se-Kyo.A Phase Tracking System for Three Phase Utility Interface Inverters[J].IEEE Transactions on Power Electronics,2000,15(3):431-438.

[2]Wang Y F,Li Y W.Three-phase Cascaded Delayed Signal Cancellation PLL for Fast Selective Harmonic Detection[J].IEEE Transactions on Industrial Electronics,2013,60(4):1452-1463.

[3]Wang Y F,Li Y W.Analysis and Digital Implementation of Cascaded Delayed-signal-cancellation PLL[J].IEEE Transactions on Power Electronics,2011,26(4):1067-1080.

[4]GolestanS,RamezaniM,GuerreroJM,etal.dq-frame Cascaded Delayed Signal Cancellation Based PLL:Analysis,Design,and Comparison with Moving Average Filter Based PLL[J].IEEE Transactions on Power Electronics,2014,30(3):1618-1632.

SRF-PLL with Delayed Signal Cancellation

XIE Menxi,ZHU Canyan,YANG Yong

(Institute of Intelligent Structure and Systems,Soochow University,Suzhou 215131,Jiangsu,China)

Grid connected power converter requires precise detection of the grid voltage phase angle for synchronization in real time.Synchronous reference frame phase-locked loop(SRF-PLL)used Park transform as phase detector(PD).As three-phase grid voltages were unbalanced,the PD output contained disturbances oscillating at double fundamental frequency,which leaded phase error inaccurate.Analyzed the filtering characteristics of Delayed Signal Cancellation(DSC)and it′s application in-loop within SRF-PLL attenuated the particular frequency component.As a result,the DSC-SRF-PLL could track the fundamental frequency positive sequence.The simulation carried out by Matlab/Simulink shows that this method has feature of high steady precision,fast response and small computation burden.The algorithm has been implemented and tested in a float-point DSP TMS320LF28335 to verify the correctness and effectiveness.

phase-locked loop;unbalanced voltage;delayed signal cancellation;digital signal processor

TM764

A

10.19457/j.1001-2095.20161014

2015-09-02

修改稿日期:2016-04-06

国家自然科学青年基金项目(51407124)

谢门喜(1984-),男,讲师,Email:xiemenxi@suda.edu.cn