一种应用于DDS 14位1 GS/s电流舵型DAC的设计

杨俊浩,张甘英,张 涛

(中国电子科技集团公司第58研究所,江苏无锡214035)

一种应用于DDS 14位1 GS/s电流舵型DAC的设计

杨俊浩,张甘英,张涛

(中国电子科技集团公司第58研究所,江苏无锡214035)

设计了一种基于SMIC 0.13 μm CMOS工艺的14位1 GS/s分段式电流舵型DAC。该DAC采用6+8的分段结构,1.2 V/3.3 V双电源供电,满摆幅输出电流为20 mA。采用两级行列温度计译码结构、输出形式可调开关驱动电路以及四开关结构,应用于直接数字频率合成器中。线性度性能满足指标要求,DNL≤1LSB,INL≤1.5LSB。

分段式;电流舵;数模转换器;直接数字频率合成器

1 前言

直接数字频率合成(Direct Digital Synthesize,DDS)是一项关键的数字化技术。与传统的频率合成相比,具有高分辨率、高转换速率、低功耗和低成本等优点,广泛应用于电信及电子仪器领域[1]。作为DDS系统核心的数字模拟转换器(Digital-to-Analog Converter,DAC),其性能直接决定了合成信号的特性,这就要求DAC具有高速高精度以及较高的动态性能。

分段电流舵DAC,集二进制码和温度计码电流舵DAC的优点,具有先天性的高速高精度特性。高位电流源由经过译码后的温度计码控制,以获得较好的线性度和匹配特性,而低位电流源直接由二进制码控制以减小面积,同时降低译码电路的复杂度。由于电流舵DAC最终输出为电流信号,不需要增加额外的电压缓冲器就可以驱动电阻负载,有效提高了DAC的转换速率。

文章第2节介绍DAC系统结构和关键模块电路设计;第3节介绍电路仿真和版图设计;第4节给出结论。

2 DAC系统结构及设计

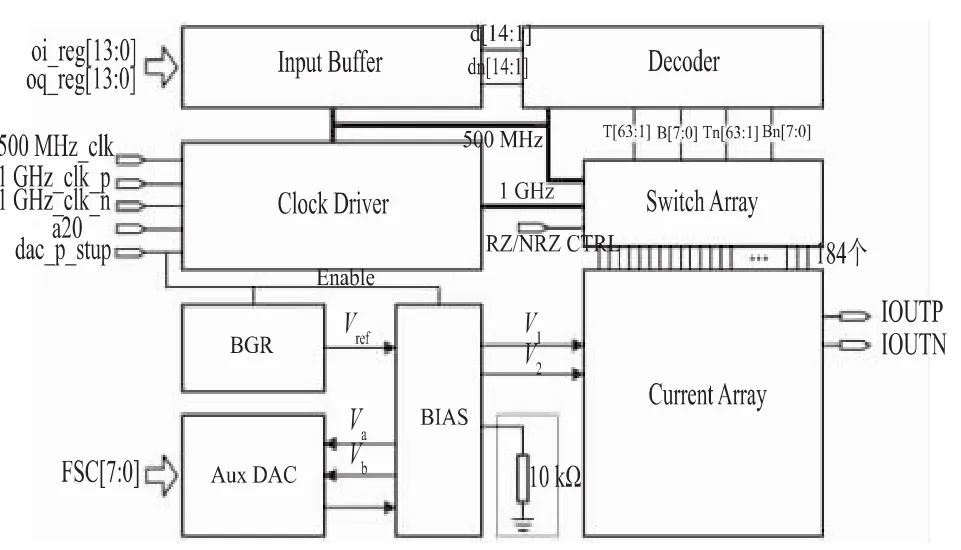

本文DAC的数字部分主要由输入缓冲寄存器、译码器、开关信号阵列和时钟驱动电路组成,结构如图1所示。两路14 bit数据信号进入输入缓冲寄存器以保证其同步性。译码器采用行列译码的方式,译码后数据经过开关信号阵列内的单元电路处理产生最终的开关控制信号。时钟驱动电路为相关模块分别提供500MHz的数据传输时钟和1GHz的数据转换时钟。

图1 电流舵DAC结构框图

2.1分段及译码

实际中,分辨率在10位以上的DAC基本采用分段译码结构,对全温度计译码及二进制译码的优缺点进行了折中。对于分段式电流舵DAC而言,采用何种分段策略是根据不同应用的特点,由性能、面积、功耗等因素折中考虑的,而整个DAC的性能通常由高位温度计译码结构的子DAC特性主导。

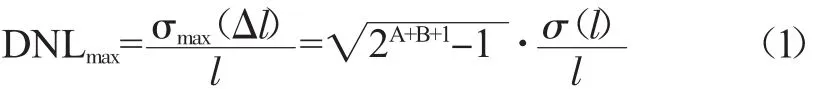

对于分段电流舵型DAC,温度计译码结构对应的相邻输入码变化时,只有一个MSB的电流单元进行了切换,则其相邻码间切换电流总和的最大值发生在相邻输入码落在段间的情况下。假设一个N位分辨率的DAC分为3段,低A位是二进制译码,中间B位为温度计译码,高(N-A-B)位为温度计译码,则其最大DNL估算值为:

由(1)式可知,分段电流舵型DAC的最大DNL估算值和所有低位位数之和有关,其比全温度计译码结构要大,但比全二进制译码结构要小,介于二者之间。

与此同时,由于高位温度计译码具有单调性,毛刺只会出现在输入信号进行段间跳变的时刻,即DAC中对应二进制译码部分的开关全部关断,而对应温度计译码部分的开关开启的时刻,其可能产生的最大毛刺为2A+B-1。分段除了导致输出端最大可能的毛刺大小不同外,还会造成对随机性误差和系统性误差分布的影响。也就是说,增加分段式电流舵DAC中温度计译码的位数时,随机性失配和系统性延迟带来的误差量都将增大。本文中的DAC根据实际应用需求,选取了6+8的分段方式。

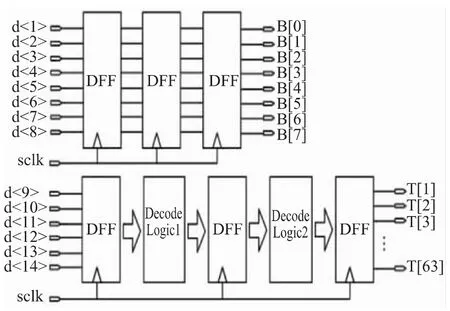

二进制译码结构部分的输入码d〈8:1〉与带有权值的电流开关一一对应,因此可以直接用于控制电流单元。而对于温度计译码结构部分的输入码d〈14:9〉,需要一个译码电路将输入信号进行译码后再用于控制电流单元。图2为两段式DAC的分段译码电路结构框图。

图2 分段译码电路结构框图

当温度计码转换位数较高时,直接采用门电路实现会存在两个问题:一是门电路中允许的最大MOS管串接数量有限,二是不同译码信号通路之间的延迟匹配性会变差。因此,这里采用2级译码以保证门电路的实现[2],并插入寄存器对译码中间信号进行同步。

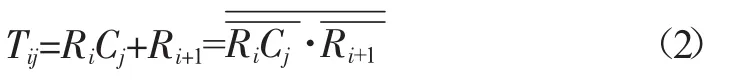

一般地,较高位数温度计译码的电路实现方式为行列译码,其译码表达式为:

其中,Ri和Cj可以通过文献[3]中介绍的方法快速得到,并用门电路直接实现第一级译码;第二级译码根据公式(2)对应的逻辑单元实现,完整的温度计译码结构如图3所示。整个译码电路由NAND、NOR两种输入逻辑和同步用DFF组成,满足高速译码要求和良好的延迟匹配性。

图3 两级行列温度计译码结构

2.2开关驱动电路

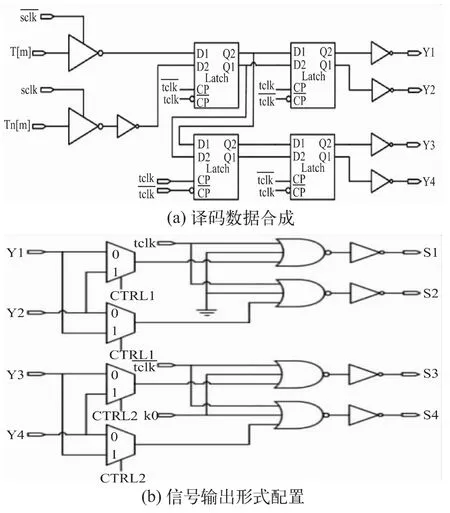

开关驱动电路用于产生四开关结构的控制信号,结构如图4所示,同时具有数据二路合一路、开关驱动和降低开关控制信号交叉点的作用。Y1、Y2、Y3和Y4为经译码合成后的数据控制信号。加入控制信号CTRL0/1和k0,并利用转换时钟tclk对开关信号重新编码生成S1、S2、S3和S4,配合四开关电路结构,实现对信号输出形式的控制。设计中,将开关驱动逻辑中PMOS管尺寸设置较大,NMOS管尺寸设置较小,使驱动信号上升时间比下降时间短,实现互补交叉点降低,避免开关同时关断。由于在tclk的跳变沿处总会发生开关的切换,产生相应的毛刺信号。因此,毛刺信号与输入信号的变化不再有直接关系,仅仅取决于转换时钟的频率[4]。这样,将原有谐波的能量转移到奈奎斯特频带以外,可以有效抑制谐波失真,提高DAC的动态性能。

图4 开关驱动电路

2.3四开关结构及电流源

本文设计的电流舵型DAC采用PMOS的Cascode结构作为电流源管,以提高输出阻抗,如图5所示。结合四开关结构和开关控制信号,可配置输出3种不同形式:NRZ,RZ一般模式和RZ交替模式。为减小毛刺影响,开关的输出端接了减小馈通效应的伪管,以提高其动态性能。

对于模拟信号的重构,DAC通常有两种基本的信号输出方式:不归零(NRZ)和归零(RZ)。这里,引入交替模式的四相开关,其与RZ方式类似地改变了DAC的传输函数,并较RZ结构更适合欠采样模式。同时由于前后半周期内的输出信号幅值相同,仅存在180°相移,所以其基波信号的功率与基本电流开关结构的DAC相同,并在功率特性方面优于RZ模式。图6为本文DAC不同输出形式的逻辑时序图。

图5 四开关结构及电流源

图6 不同输出形式逻辑时序图

3 仿真及版图

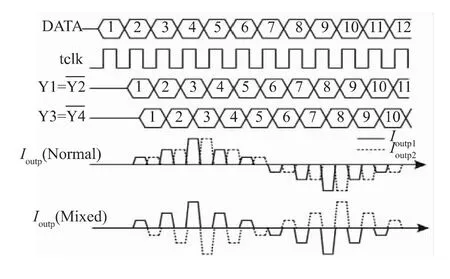

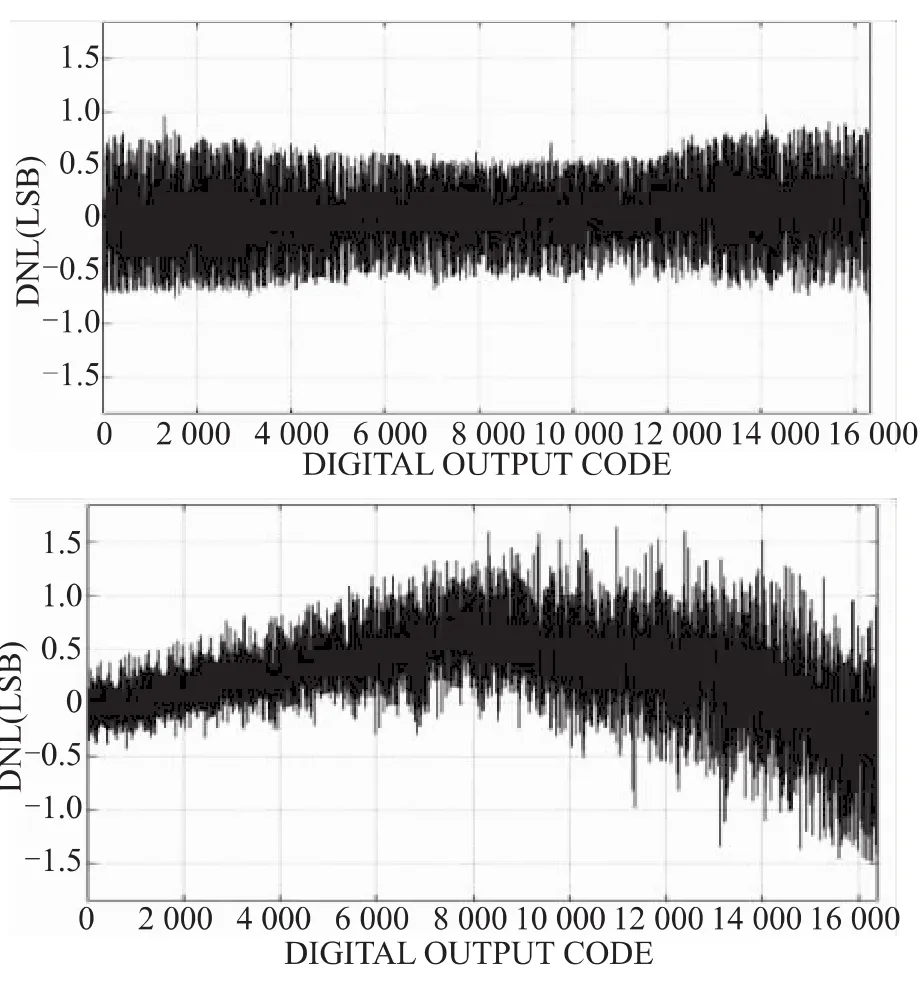

通过改进电路结构,调整电路中器件的尺寸,实现线性度优化设计,以保证DAC线性度性能满足指标要求:DNL≤1 LSB,INL≤2 LSB。14位DAC在1 GSPS、25℃、TT典型工艺条件下,使用HSIM结合MATLAB仿真得到的线性度性能如图7所示:DNL≤1 LSB,INL≤1.5 LSB。

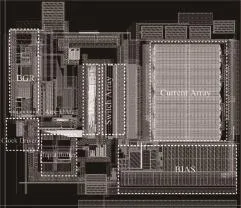

图8是放进DDS中的DAC版图,电流源阵列左侧为译码电路和开关驱动电路,下方为偏置模块。

4 结论

本文提出的电流舵型DAC采用6+8分段方式,配合可输出不同形式的四开关结构,在高速高精度下达到了较高的动态性能,可灵活应用于DDS系统中。线性度性能满足指标要求:DNL≤1 LSB,INL≤1.5 LSB。

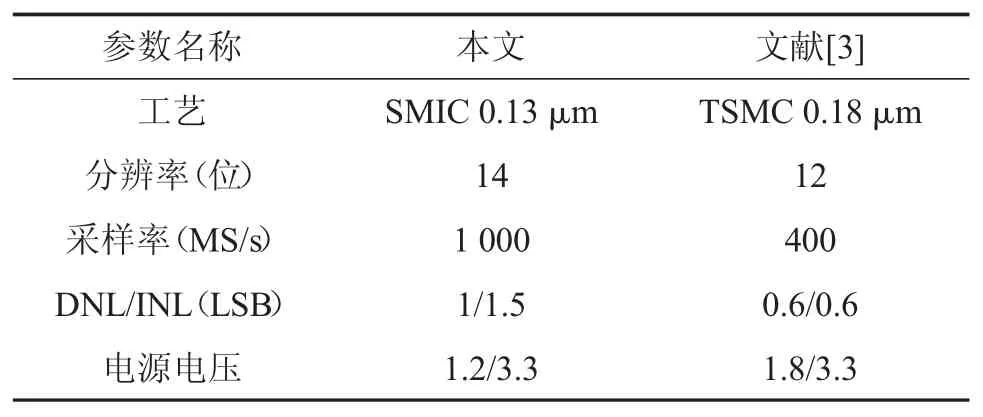

表1给出了该DAC的主要性能参数。

图7 DAC线性度仿真波形

图8 放进DDS中的DAC版图

表1 本文提出的DAC性能参数

[1]王兵.频率合成技术发展浅析 [J].电子信息对抗技术,2009,24(3):74-77.

[2]HALDER S,BANERJEE S,GHOSH A,et al.A 10 bit 80 MSPS 2.5 V 27.65 mV 0.185 mm2segmented current steering CMOS DAC[C].Proc 18thInt Conf VLSI Design,Kolkata,India.2005:319-322.

[3]薛晓博.高速高精度电流舵数模转换器关键设计技术的研究与实现[D].浙江大学博士论文,2014.

[4]PARM S,MIM G,PARM S C,et al.A digital to analog converter based on differential quad switching[J].IEEE J Sol Sta Circ,2002,37(10):1335-1338.

Design of 14-bit 1 GS/s Current Steering D/A Converter for DDS Application

YANG Junhao,ZHANG Ganying,ZHANG Tao

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214035,China)

A 14-bit 1 GS/s current-steering DAC manufactured in SMIC 0.13 μm CMOS is presented in the paper.The 6+8 segmented architecture consists of 6 thermometer decoded MSBs and 8 binary decoded LSBs. The full-scale current output is 20 mA with 1.2 V/3.3 V dual power supply.Two-level logic decoder,switch driver circuits with configurable output form and a special quad switch circuit are designed for the DDS application.DNL is less than 1 LSB and INL is less than 1.5 LSB.

segment;current-steering;digital-to-analog converter(DAC);direct digital synthesizer(DDS)

TN402

A

1681-1070(2016)08-0030-04

2016-4-29

杨俊浩(1988—),男,江苏溧阳人,硕士,助理工程师,现从事数模混合集成电路设计工作。