薄外延CMOS芯片阱掺杂浓度与击穿电压的关系

韩兆芳,谢 达,乔艳敏

(中国电子科技集团公司第58研究所,江苏无锡214035)

微电子制造与可靠性

薄外延CMOS芯片阱掺杂浓度与击穿电压的关系

韩兆芳,谢达,乔艳敏

(中国电子科技集团公司第58研究所,江苏无锡214035)

CMOS电路由于寄生结构的影响,易于发生闩锁效应。主要通过流片实验测试验证,探讨了在外延厚度较薄的情况下阱掺杂浓度与击穿电压之间的关系。提出了在不改变外延厚度、保证芯片抗闩锁性能的前提下,提高CMOS器件击穿电压的方法。

CMOS集成电路;闩锁效应;外延片;穿通击穿

1 引言

CMOS器件具有低静态功耗、高输入阻抗以及较佳的噪声抑制能力等特性,在超大规模集成电路中应用广泛。尽管CMOS集成电路有众多优点,但它并非完美无缺,比如由于与生俱来的寄生结构影响,易于发生闩锁效应,严重时会导致芯片直接烧毁。

常见预防闩锁的方式,除了在设计时采取一些措施外,在工艺上采用外延片也是比较有效的方式之一。采用外延片时,外延层厚度需要进行控制,如果外延层太厚,达不到理想的抗闩锁性能,特别对一些具有抗辐照指标的电路来说,比如抗单粒子闩锁,很难达到预期效果。如果外延层较薄,对CMOS器件源漏之间的击穿电压(BVds)会有一定的影响。在采用薄外延以保证电路抗闩锁性能的前提下,如要提升器件的击穿性能,必须考虑采取合理的措施。本文主要通过流片实验验证,探讨了在外延厚度较薄的情况下阱掺杂浓度与击穿电压之间的关系,从而在不改变外延厚度、保证芯片抗闩锁性能的前提下,提高器件的击穿电压。

2 流片试验

为了保证电路具有良好的抗闩锁性能,特别是在辐照环境下具有良好的抗单粒子闩锁性能,电路选用了比较薄的外延片,即4.5 μm厚度的P型外延片,采用0.5 μm N阱CMOS工艺流片。电路的工作电压为4.5~5.5 V,为了在一定的过电应力(EOS)及出现电源波动或者过冲的条件下电路能够正常应用,电路PMOS管源漏之间的击穿电压(BVds)需在9.5 V以上。

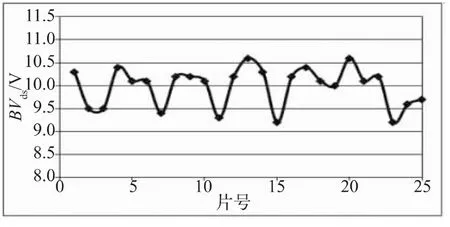

流片后封装的电路经抗闩锁测试,在过电流闩锁测试中所有引脚可以达到300 mA以上,部分引脚甚至可以达到500 mA,具有较好的抗闩锁性能。但在衬底接地的情况下,圆片PMOS管源漏之间的实际击穿电压BVds不够高,测试值分布如图1。

图1 圆片击穿电压分布图

部分圆片的击穿电压低于要求的9.5 V,最低的甚至已经接近9 V,在容易出现电源波动以及信号过冲的环境下,如果过冲的瞬时电压达到9 V以上,就容易出现电路击穿失效,偏低的击穿电压已经影响到电路的正常应用。

3 试验结果分析

3.1剖面分析

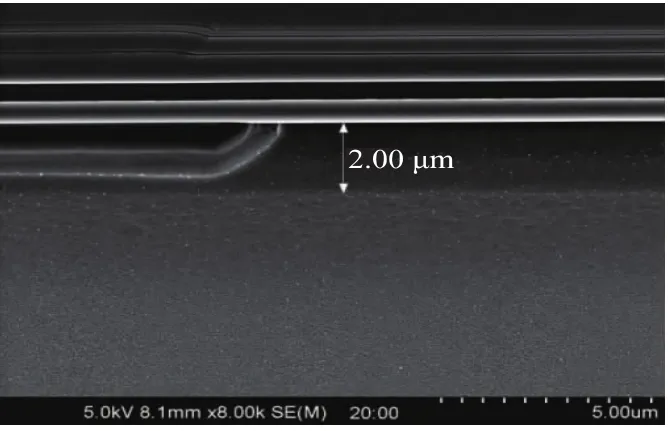

为了查找BVds偏低的原因,首先对芯片做剖面染色分析,在扫描电镜下观测芯片中PMOS管的剖面,发现经过N阱推进的工艺热过程后,P型硅衬底中的掺杂B离子上扩,导致外延厚度变薄,芯片的外延厚度变得只有2 μm左右,N阱和衬底之间的外延层厚度只剩余0.4 μm左右。芯片剖面SEM照片见图2。

图2 芯片剖面SEM照片

流片后外延厚度变薄导致耗尽区变薄,是影响击穿电压的原因之一,但为了保证电路的抗闩锁性能,在不更改设计的前提下,不希望改用厚外延流片。因此,需要分析是否还存在其他因素影响BVds,并进行调整以提升击穿电压。

3.2阱掺杂影响

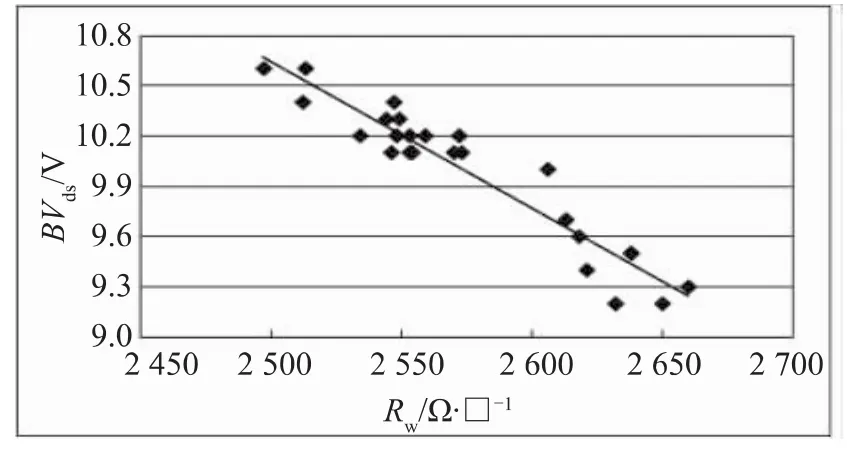

BVds除了与N阱和P型衬底之间的外延层厚度有关外,阱与外延层之间的P/N结两端掺杂浓度对其影响也比较大。对于单边突变结,特别是掺杂浓度较低的阱区域一侧,对击穿的影响更大。阱掺杂浓度可以用阱方块电阻(Rw)表征,Rw值越高,阱掺杂浓度越低。统计发现,BVds和Rw呈现出线性的反比关系,Rw偏高的,BVds就偏低,如图3所示。

图3 芯片BVds和Rw的对应关系

根据图3中BVds和阱方块电阻Rw的统计关系,可以看到阱方块电阻Rw值越高,即阱掺杂浓度越低,其击穿电压相对就越低,阱掺杂浓度和电路击穿电压呈正比关系,这和正常的PN结击穿时PN结两端的掺杂浓度越低击穿电压越高是相反的。一般情况下,对于PN结两边掺杂浓度差距较大的单边突变结,PN结击穿电压VBR主要取决于轻掺杂一侧的掺杂浓度,即N阱的掺杂浓度,掺杂浓度越低,击穿电压越高。正常PN结击穿电压VBR和掺杂浓度的对应关系如图4。

图4 击穿电压与掺杂浓度的对应关系

该芯片的阱掺杂浓度为1016N/cm-3量级,如果耗尽区足够宽,其击穿形式为雪崩击穿,击穿电压可以达到十几甚至数十伏。实验芯片在9 V左右就出现击穿,而且从剖面染色可以看到,N阱与衬底之间的外延层只余下0.4 μm左右的厚度,说明该芯片BVds击穿不是常见的雪崩击穿,而是由于耗尽区宽度不够导致的穿通击穿,这与阱掺杂浓度越高、BVds反而越高的现象是一致的,穿通电压与寄生三极管基区(即N阱)掺杂浓度呈正比关系。

3.3测试方式影响

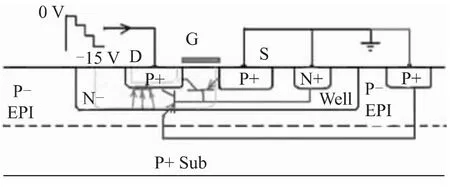

另外,为了验证芯片中的PMOS源漏击穿是穿通击穿,采用两种方式测量BVds,一种方式在测试时衬底悬空,另外一种方式在测试时衬底接地。两种不同的测试方式击穿示意图如图5、图6所示。

图5 衬底悬空时的BVds测试示意图

图6 衬底接地时的BVds测试示意图

衬底悬空时,漏极(D)、源极(S)的重掺杂P区和栅极(G)下面阱内的沟道N区构成寄生的横向PNP三极管,击穿主要发生在漏极的重掺杂P区(相当于三极管发射极)和栅极下面的沟道区域(相当于三极管基极)之间的PN结上;衬底接地时,除了在漏极P区和栅极沟道之间的PN结上可能发生击穿外,漏极、N阱和P型外延(包括重掺杂的衬底)组成寄生的纵向PNP三极管,在漏极P区和N阱之间也存在击穿的可能。

经测试,同一个芯片在衬底悬空时明显比衬底接地时的BVds测试值高,且在衬底接地时测试BVds越低的芯片,相对于在衬底悬空时的测试值差距越大,最多差2 V左右。由于N阱区域的掺杂浓度是相对固定的,不论是栅极下面的沟道区域还是漏极下面的阱区域,两者掺杂浓度差距不大,只是耗尽区宽度不同,沟道区域耗尽区相对要宽一些,再加上阱掺杂浓度和击穿电压呈正比关系,可以确认纵向PNP三极管为穿通击穿,如果要提高BVds的测试值,则需要重点提高纵向三级管的穿通击穿电压。

3.4BVds提高分析

在半导体器件物理中,三极管的穿通电压公式如下:

其中NB为三极管基区掺杂浓度,Wb0为基区宽度,εε0为材料的介电常数。

如果要提高寄生PNP三极管的穿通电压,在材料介电常数一定的条件下,可以增加基区(即N阱)掺杂浓度,也可以增加基区宽度,即N阱的深度。由于芯片所用的外延片为4.5 μm的薄外延片,在现行的工艺条件下,根据芯片剖面染色测量的照片,因为衬底中B离子的上扩,外延仅余下2 μm左右,N阱与外延之间的间隙已经很小了,如果增加推阱时间或者温度,会造成衬底中的B离子上扩更加严重,由于衬底是重掺杂的,其掺杂浓度远高于N阱注入剂量,反而会造成阱的深度缩小,即寄生纵向三极管基区宽度缩小,更不利于提高穿通电压。为了保证电路的抗闩锁性能,增加外延厚度也不失为一个好的选择。因此,最好是通过增加N阱注入剂量,提高纵向寄生PNP三极管基区掺杂浓度,来提升穿通电压。

3.5N阱注入对抗闩锁性能的影响

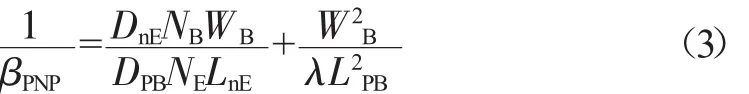

CMOS电路内触发寄生的闩锁效应,寄生PNPN结构环路的电流增益必须要大于l,即:

在寄生的PNPN可控硅器件中,PMOS管的N阱相当于纵向PNP管的基区,在有源区掺杂浓度高于N阱掺杂浓度2~3个数量级的情况下,共射极直流增益βPNP与器件结构参数的关系可近似表示为:

式中DnE、DpB为发射区、基区中少子扩散系数,LnE、LpB为发射区、基区少子扩散长度,NB、NE为基区、发射区掺杂浓度,WB为基区宽度,λ为与基区杂质分布情况有关的系数。从式中可以看出,PNP管的增益与基区掺杂浓度NB近似于成反比关系,如果增加N阱的掺杂浓度,可以降低PMOS管内寄生的PNP管的增益,从而降低βPN·PβNPN的值,在提升BVds的同时,也增强了电路的抗闩锁性能,提高了电路的可靠性。

4 阱掺杂调整实验

挑选一批厚度接近的外延片流片,其中2片(19# 和20#)进行阱掺杂浓度调整,阱注入剂量增加10%,其余的圆片按照正常剂量进行阱注入。圆片流出后,按照衬底接地的方式测量BVds,阱注入调整的圆片BVds比其他圆片高2 V左右,可以看出阱注入剂量调整对于BVds提升明显。整批圆片BVds测试结果见图7。

在选用较薄的外延以保证芯片抗闩锁性能的情况下,对阱注入剂量需要慎重考虑,阱掺杂浓度增加虽然可以提升击穿电压,但也不宜增加太多,根据击穿电压与掺杂浓度的对应关系,芯片的阱掺杂浓度不宜高出1016N/cm-3量级,否则会导致器件的雪崩击穿电压过低,影响电路应用。

图7 实验圆片击穿电压分布图

5 结束语

对于采用薄外延流片的电路,特别是流片后实际外延厚度只有2 μm左右的芯片,阱注入剂量对于电路中管子的源漏击穿参数影响较大。通过增加阱注入剂量可以提高管子的穿通击穿电压,同时还有利于提高电路的抗闩锁性能。

在增加阱掺杂浓度后,由于沟道区的阱区掺杂浓度也随之改变,也会同时改变管子的开启电压,为了避免影响电路的输出驱动和速度,需要另外进行开启电压的调整。

[1]施敏.半导体器件物理与工艺[M].苏州:苏州大学出版社,2002.

[2]T F Miyahira,A J Johnston.Catastrophic latch-up in CMOS analog-to-digital converters[J].IEEE Trans Nucl Sci,2001,48(6).

[3]唐晨,孙伟锋,陆生礼.CMOS电路中抗Latchup的保护环结构研究[J].现代电子技术,2006,(04).

[4]郝跃,贾新章,董刚,等.微电子概论[M].北京:电子工业出版社,2011.

[5]王蕴辉,于宗光,孙再吉.电子元器件可靠性设计[M].北京:科学出版社,2007.

[6]韩郑生.抗辐射集成电路概论[M].北京:清华大学出版社,2011.

[7]维捷斯拉夫·本达,约翰·戈沃,邓肯A·格兰特.功率半导体器件——理论及应用 [M]. 北京:化学工业出版社,2011.

[8]姚立真.可靠性物理[M].北京:电子工业出版社,2004.

Research of Relationship Between Well Doping Concentration and Breakdown Voltage in Thin-Epitaxy CMOS Chips

HAN Zhaofang,XIE Da,QIAO Yanmin

(China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214035,China)

Potential parasitic structure in CMOS integrated circuits may cause latch-up effect from time to time.To solve the problem,the paper makes experiments to explore the relationship between well doping concentration and breakdown voltage in CMOS chips with thin epitaxy technique via wafer testing. Aneffective method increasing breakdown voltage of CMOS deviceswhile retaining epitaxy thickness and anti-latch-up capability is proposed.

CMOS integrated circuit;latch-up effect;epitaxy wafer;punch-through breakdown

TN432.1

A

1681-1070(2016)08-0037-04

2016-4-27

韩兆芳(1975—),男,山东济宁人,工学硕士,毕业于西安电子科技大学技术物理学院,现在中国电子科技集团公司第58研究所从事集成电路及元器件失效分析工作。