一种基于DSP的通用存储器接口的设计

解同同,李天阳

(1.江南大学物联网工程学院,江苏无锡214122;2.中国电子科技集团公司第58研究所,江苏无锡214035)

一种基于DSP的通用存储器接口的设计

解同同1,李天阳2

(1.江南大学物联网工程学院,江苏无锡214122;2.中国电子科技集团公司第58研究所,江苏无锡214035)

DSP芯片的通用存储器接口可以满足DSP芯片访问片外存储器的需求,减少DSP芯片中嵌入式存储器的面积,提升DSP芯片整体性能。设计一款高性能的通用存储器接口是DSP芯片设计工作中的重要环节。设计并实现了一种基于DSP的通用存储器接口,支持多种同步或异步的ROM、SRAM和Flash存储器,支持存储器突发访问,支持外部总线共享。经过仿真验证,存储器接口可以正常工作。目前已成功应用于一款32位DSP芯片中。

DSP;通用;存储器接口;突发访问

1 引言

DSP芯片用于数字语音或图像处理等大数据吞吐量的领域时,需要大容量存储空间的支持[1],而DSP芯片有限的片内存储器容量限制了DSP功能的发挥,因而DSP芯片需要通过片外存储器来扩大存储空间[2]。存储器接口按照所控制的存储器类型可以分为两种:专用存储器接口和通用存储器接口。专用存储器接口针对单一类型的存储器,可重用性不好。目前大部分的高性能DSP芯片使用的都是通用外部存储器接口[3],可以支持多种存储器,具有良好的通用性。通用存储器接口通过IP核重用的方式,可以用于不同要求的DSP芯片,从而减少开发时间,降低成本,加快芯片投入市场的速度。

在执行存储器访问时,访问存储器比访问CPU内部的寄存器或Cache的速度要慢得多。为了充分发挥CPU的速度,就有了突发访问技术(Burst)技术,突发访问一次性读取成组的数据,使较慢的存储器能够适用于较快的CPU。本文所设计的通用存储器接口在支持多种存储器的基础上,还支持存储器突发访问,适用于DSP芯片。

2 通用存储器接口的功能分析

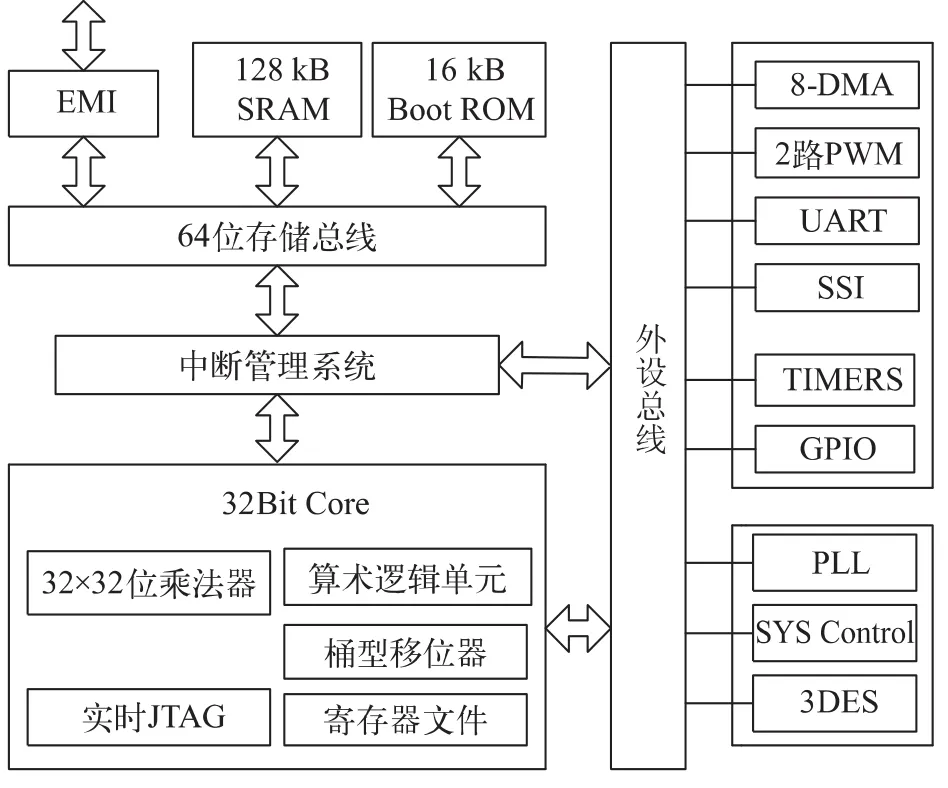

本文所设计的通用存储器接口是外部存储器接口,用于一款32位高性能DSP芯片GX300。这款DSP芯片的整体结构如图1所示。GX300支持32位指令集,最大工作频率300 MHz。电路包含了DSP内核、PLL、看门狗、8路PWM、4个32位timer、2路UART、2路SPI等模块。芯片的性能特点主要有:运算频率300 MHz、支持16 bit和24 bit指令编码、7级流水线、可编程的读写周期、支持数据读写缓存、带滑动窗的函数调用和返回、外部总线频率可配置、内置指令与数据缓存、支持片外flash、ROM和SPI三种启动方式启动。

图1 GX300芯片整体结构框图

图1中的EMI(external memory interface)即为本文所设计的基于DSP的通用存储器接口。EMI通过64位存储总线与系统连接,可以连接片外存储器和具有合适接口的外部设备。EMI具有64位的内部总线、32位的外部总线。

EMI通过灵活地编程调整存取参数,可支持多种存储器和外设的连接。主要类型为非复用的异步或同步 存 储 器 ROM、EPROM、NORflash、RAM 和PSRAM/SSRAM;复用的异步或同步存储器NOR flash和PSRAM/SSRAM。

EMI支持多种存储器的互联,支持的数据访问类型有同步和异步的非复用访问方式的器件,同步和异步的复用访问方式的器件。可通过编程以支持以下几种存储器类型:(1)复用异步访问存储器(复位后默认);(2)复用突发传输型存储器;(3)非复用异步型存储器;(4)非复用块传输型存储器。

外部总线仲裁使得EMI能与其他主设备共享外部总线,使得外部主设备能够访问连接在外部总线上的其他设备。设定占有模式和保持模式两种总线模式。占有模式下EMI作为外部总线主机工作,此时其他任何主设备都不可以访问外部总线。而在保持模式下,EMI容许其他主设备访问外部总线。外部总线可以被锁定以容许EMI对外部总线不受干扰的连续访问。EMI会一直占用外部总线直到锁存访问请求无效。

本文设计的EMI模块已经成功应用于32位的DSP芯片GX300,此DSP芯片已经通过测试并且流片,EMI模块满足设计要求。

3 设计方案

3.1总体设计

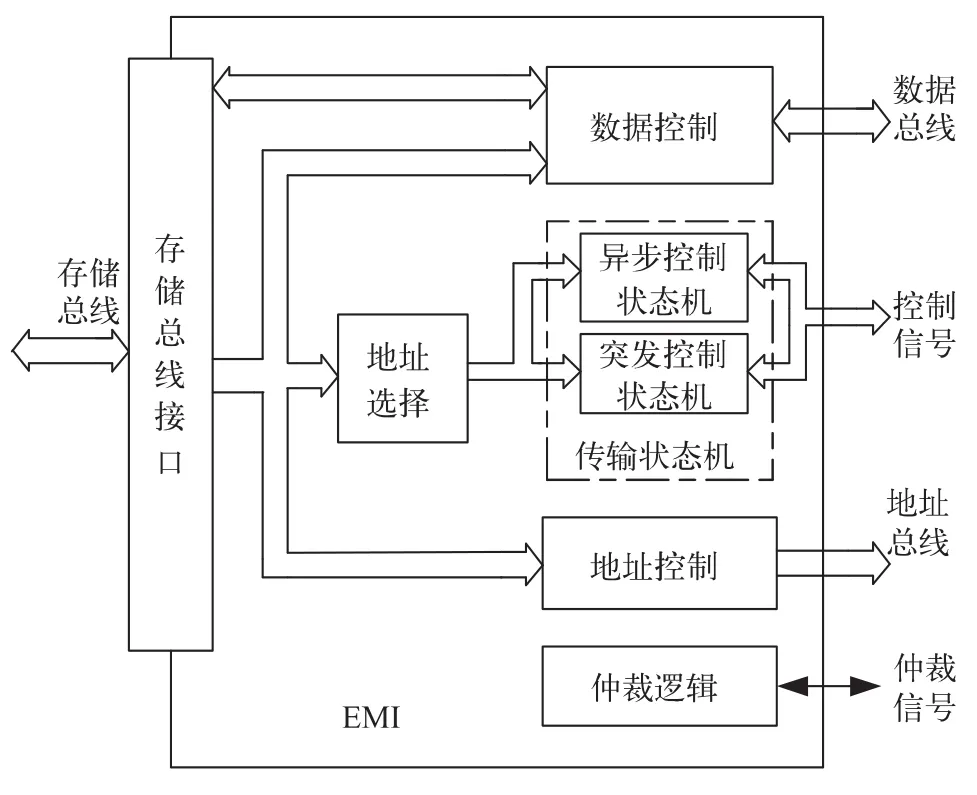

图2为EMI的整体结构框图,主要由数据控制模块、传输状态机模块、地址控制模块、仲裁逻辑模块和地址选择模块构成。本文将重点介绍地址选择模块和传输状态机模块的设计。

图2 EMI模块总体结构框图

地址选择模块根据存储总线的地址信号选择需要访问的外部存储区域,包括选择所需的存储区域控制参数和地址,并将控制参数传给传输状态机。

数据控制模块用于存储总线数据线与外部总线数据总线之间的转换,解决了位宽转换问题,使EMI可以支持16位、32位的外部存储器。

传输状态机模块内部包含了异步控制状态机和突发控制状态机,异步控制状态机用于异步存储器的控制,突发控制状态机用于同步存储器或存储器的突发访问。传输状态机的设计中设置了多个可选的访问相位,可通过寄存器进行灵活的设置使EMI具有多种功能。

地址控制逻辑用于地址转换,负责向外部地址总线发送地址信号。

仲裁逻辑模块通过仲裁信号接口同其他外部设备进行连接,使EMI可以和其他主设备共享外部总线。

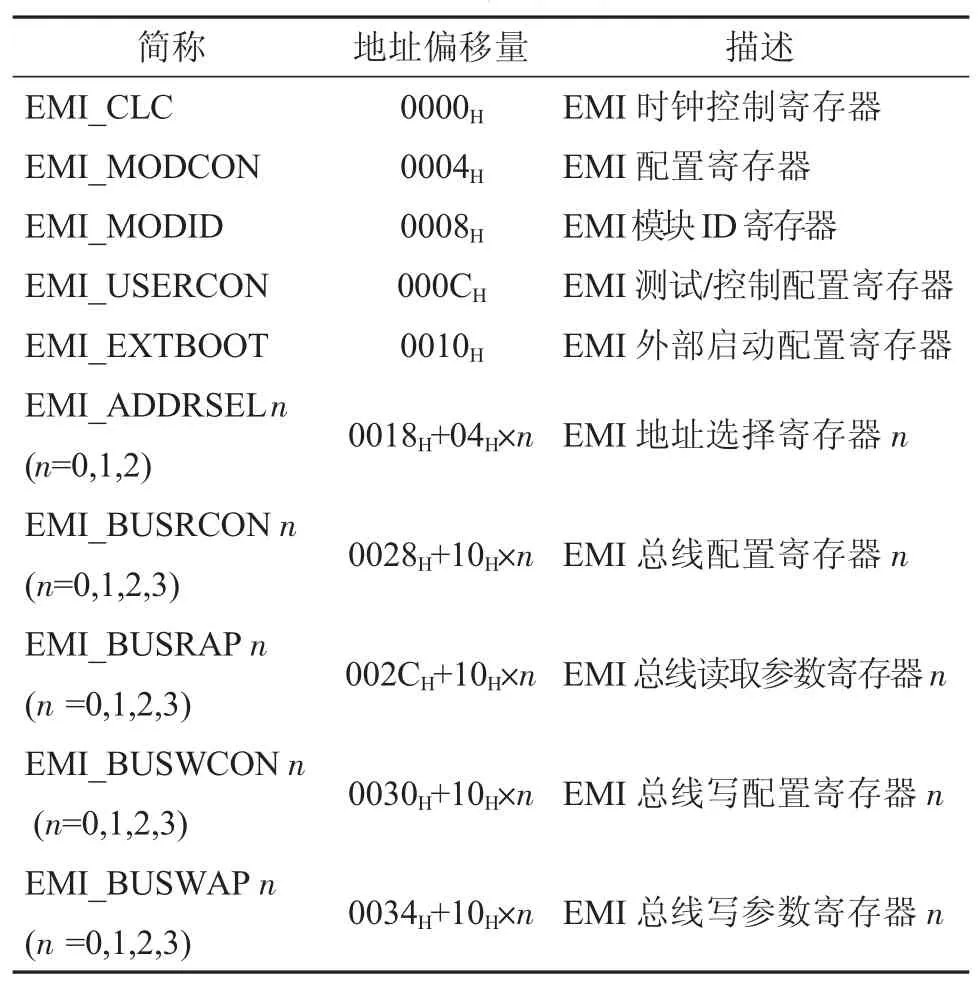

根据EMI应具有的功能,对EMI的接口信号进行设计。表1列出了EMI接口信号。EMI具有4个片选信号,支持4个存储区域,EMI需要寄存器对访问操作进行灵活的设置。表2介绍了EMI的寄存器。

表1 EMI接口信号列表

表2 EMI内部寄存器

3.2地址比较模块的设计

EMI提供4块用户可编程的存储区域,如表3所示。每一块存储区域对应一组寄存器和一个片选信号,来设置外部总线的传输参数。外部总线对这些用户可编程的存储区域中的一个进行操作,通过EMI进行适宜的转换。片选信号用来选择存储区域;地址选择寄存器用来配置存储区域的地址空间;总线配置寄存器和总线参数寄存器用来设置传输的速度、类型和参数。

地址选择模块工作的整体流程如图3所示。

(1)32位的存储总线地址同时进入4个存储区的地址比较逻辑。

(2)4个存储区域同时进行地址比较,比较的结果决定了存储总线地址是否处在有效的存储区域内。如果没有匹配的地址,Region仲裁逻辑将产生一个NO MATCH信号。如果有匹配的地址,Region仲裁逻辑产生一个Region Matched信号到下阶段。Region仲裁逻辑按照存储区域的优先级进行仲裁,Region 0的优先级最高,Region 4的优先级最低,如果有不止一个Region匹配,输出优先级高的。

表3 各存储区域对应的片选信号和寄存器描述

(3)参数选择逻辑根据上一阶段的输出选择合适的访问周期参数。各存储区的参数可由相对应的寄存器设置。最后选择逻辑将检查具有最高优先级的存储区域的访问参数,确定是否为无效的访问。如果访问是无效的,将产生一个ERROR ACK信号并且中止本次访问。否则,访问参数被供给外部总线驱动逻辑。

(4)输出的访问参数将传到传输状态机模块适当的状态机中。

图3 地址选择模块工作流程

地址比较逻辑是地址选择模块的核心部分,地址比较电路通过地址比较,以判定要进入的外部存储区域[4]。通过EMI_ADDRESELn(n=0,1,2,3)寄存器的设置,使每个EMI存储区域都能获得独立的基地址和长度。

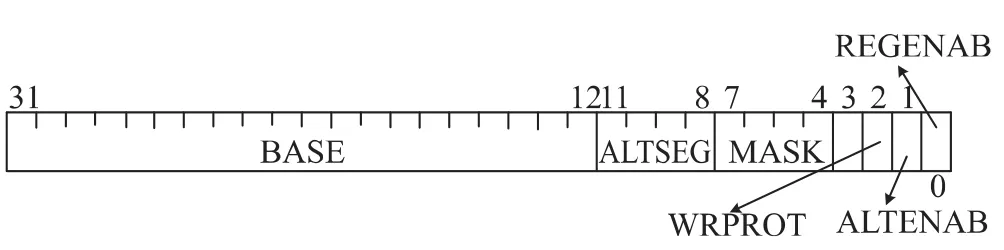

EMI_ADDRESEL寄存器分配情况如图4所示。REGENAB位是单个存储区域的使能控制位,如果REGENAB=0,则存储区域被禁用,存储区域的地址比较将不会发生。ALTENAB位决定了由ALTSEG位域定义的存储区域预备段能否用于地址比较。WRPROT位对存储区域写保护,如果WPROT=1,则存储区域被保护,那块存储区域在写访问时将不会发生地址比较。MASK位域决定存储区域的长度,它指定了必须有多少位的总线地址与BASE位域的内容相匹配(从A[26]开始,最大15位,A[31:28]是必须匹配的)。ALTSEG位段决定了用于与总线地址A[31:28]进行地址比较的预备段的数量(如果ALTENAB=1)。BASE位段决定了要和总线地址比较的基地址,和MASK配合使用。

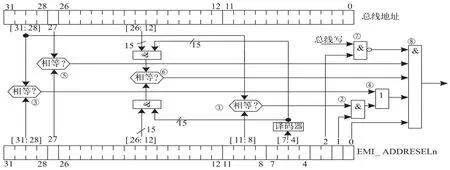

当EMI处理外部总线访问时,总线地址是在4个存储区域平行进行比较。地址比较的具体过程如图5所示。

(1)总线地址最高的4位与ALTSEG位段进行比较(预备段地址)。比较结果(相等为1,否则为0)提供给一个与门。

(2)如果ALTENAB=0,则预备段功能被禁用,与门输出结果为0。如果ALTENAB=1,则预备段功能被使能,步骤1中ALTESEG位段与总线地址分部位的比较结果被提供给或门。

图4 EMI_ADDRESEL寄存器

(3)总线地址最高的4位(主段地址)与BASE位段的最高4位进行比较。比较结果(相等为1,否则为0)传给或门。

(4)或门综合“主”和“预备”段地址比较的结果。如果总线地址在存储区域选定的段中,或门输出为1,否则为0。或门的结果发送到最后的与门。

(5)总线地址的第27位(无条件的)与BASE的第15位(EMI_ADDRESEL第27位)进行比较,比较结果(相等为1,否则为0)传给最后的与门。

(6)MASK位通过译码器扩展和与门的作用来控制参与比较的位。总线地址被选中的位([26:12]中)与BASE中被选中的位(EMI_ADDRESEL的[26:12]中)进行比较,比较结果(相等为1,否则为0)传给最后的与门。

(7)如果对一块只读区域进行写操作(WPROT=1),与非门的输出结果为0,这样就防止了这块只读区域被选中。与非门的输出结果传给最后的与门。

(8)最后一个与门总共有5个输入,除了前面各相位产生的输入外,还有EMI_ADDRESEL寄存器的REGENAB位。如果存储区域被使能(REGENAB=1)且地址比较产生匹配,最后的与门输出1。当该区域被定义为只读访问时,访问不是写访问。

3.3传输状态机设计

传输状态机模块内部包含了异步控制状态机和突发控制状态机两大部分。异步控制状态机用于异步存储器的控制,突发控制状态机用于同步存储器或存储器的突发访问控制。

在传输状态机的设计中设置了多个可选的访问相位,可通过寄存器进行灵活的设置使EMI访问不同类型的存储器。对不同类型存储器的访问,或者在不同存储器访问间切换,时序变化是有规律的。控制状态机就是根据传输中的访问相位设置状态的[5]。

3.3.1异步控制状态机的设计

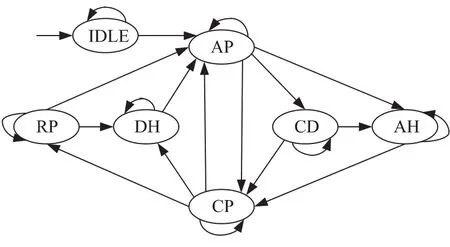

异步控制状态机用来产生访问异步存储器所需的各种控制信号[6]。异步控制状态机的状态转换如图6所示。IDLE:空闲状态,当要退出访问时,将直接转到IDLE状态;AP:地址相位;AH:地址保持相位;CD:命令延迟相位;CP:命令相位;DH:数据保持相位;RP:恢复相位。

图5 地址比较流程

图6 异步控制状态机

由异步控制状态机的状态转换图可知,AP和CP状态最为关键,而RP、DH、CD和AH阶段是可以跳过的。异步控制状态机开始时先从IDLE转到地址相位以确定访问地址,在访问有复用端口或低速设备时地址相位可通过地址保持相位或命令延迟相位,如有必要AP要先后经过地址保持相位和命令延迟相位才能进入下一阶段,然后转到CP(命令相位),在命令相位控制机设置各种控制信号,DH(数据保持相位)用于写访问时为数据传输提供延迟,RP(恢复相位)用于不同器件访问切换时提供延迟,RP和DH都是可选的,最后如要进行下一个访问操作CP(可经过DH或RP)转到AP,继续下一轮状态转换。

3.3.2突发控制状态机的设计

突发控制状态机用来产生访问异步存储器所需的各种控制信号。突发控制状态机是在异步控制状态机的基础上进行设计的,比异步控制状态机多了BP(突发相位)状态。

突发访问传输是指取得总线控制权后连续进行多个数据的传输。突发访问时,只需要给出目的地的首地址,访问第一个数据后,第2~N个后续数据会在首地址基础上按一定规则自动被寻址和传输[7]。

突发控制状态机的状态转换如图7所示。访问操作进行到CP(命令相位)后,必须转到BP(突发相位)状态。BP(突发相位)提供了突发访问所需的条件。

图7 突发控制状态机

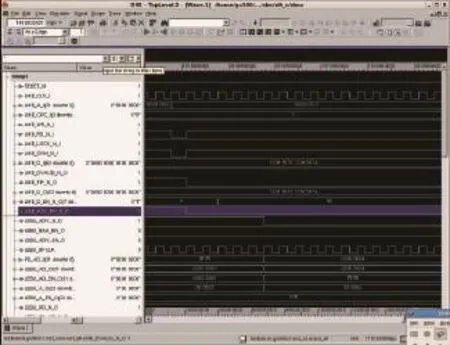

4 仿真验证

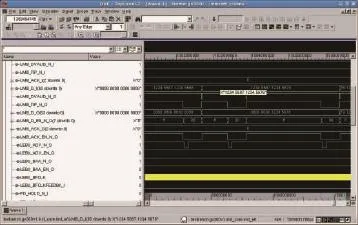

本设计采用VHDL实现,用Synopsys公司的VCS进行仿真。

验证方案:在EMI外部连接一块32位SRAM,64位存储总线通过EMI向SRAM的随机地址写入数据,成功写入数据后读出数据,写入数据与读出数据进行比较。

如图8所示,存储总线上的64位数据1234_5678_1234_5678H成功写入SRAM中。

如图9所示,在写入数据成功后,存储总线上从SRAM同一地址读出的64位数据为1234_5678_1234_5678H。读出数据与写入数据相同,符合设计预期。

5 结论

本文设计了一款用于DSP的通用存储器接口,重点介绍了其地址选择模块和控制状态机的设计,最后通过了仿真验证,满足设计要求。该接口支持复用或非复用的多种位宽的SRAM、ROM和FLASH,支持存储器的突发访问,支持4块外部存储区域。

图8 通过EMI向SRAM写入数据

图9 通过EMI从SRAM读出数据

[1]孟哲,陈国靖.DSP芯片的选型[J].现代计算机,2000(04): 76-78.

[2]廖专崇,黄俊义.存储技术的现状与未来 [J].电子产品世界,2004(Z1):51-55.

[3]陆祯琦.一种DSP片上存储机制及其系统的设计与实现[D].上海交通大学,2009.

[4]薛祎杰,戎蒙恬,刘文江.一种可配置Nand-Flash控制器的设计[J].信息技术,2006,30(11):1-4.

[5]王力纬.多端口存储器控制器IP核的设计与实现[J].武汉大学学报:理学版,2007(5):617-621.

[6]付兴飞,陈胜刚,曾思,陈书明.基于AMBA总线的存储控制器接口设计 [J].计算机研究与发展,2015(S2): 119-123.

[7]张国霞.嵌入式SRAM/SSRAM/FLASH控制器的设计及关键面积算法研究[D].西安电子科技大学,2009.

Design of a DSP-based Universal Memory Interface

XIE Tongtong1,LI Tianyang2

(1.College of Internet of Thing,Jiangnan University,Wuxi 214122,China;2.China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214035,China)

Universal memory interface in DSP chip is able to meet the demands of accessing external memory and reduce the embedded memory in the DSP chip area,thereby enhancing the overall performance of the DSP chip.The design of a high-performance universal memory interface is of great importance in designing a DSP chip.The paper designs and develops a universal memory interface based on DSP,which is compatible with a variety of synchronous or asynchronous ROM,SRAM and Flash memory,supports memory burst access and enables external bus sharing.Simulation shows that the memory interface works well.The design has been successfully used in a 32-bit DSP chip.

DSP;universal;memory interface;burst access

TN402

A

1681-1070(2016)08-0024-06

2016-3-30

解同同(1988—),男,江苏徐州人,硕士研究生,研究方向为集成电路设计。