改进DICE结构的D触发器抗SEU设计

孙 敬,陈振娇,陶建中,张宇涵

(1.江南大学,江苏无锡214062;2.中国电子科技集团公司第58研究所,江苏无锡214035)

改进DICE结构的D触发器抗SEU设计

孙敬1,2,陈振娇2,陶建中1,2,张宇涵2

(1.江南大学,江苏无锡214062;2.中国电子科技集团公司第58研究所,江苏无锡214035)

基于DICE结构主-从型D触发器的抗辐照加固方法的研究,在原有双立互锁存储单元(DICE)结构D触发器的基础上改进电路结构,其主锁存器采用抗静态、动态单粒子翻转(SEU)设计,从锁存器保留原有的DICE结构。主锁存器根据电阻加固与RC滤波的原理,将晶体管作电阻使用,使得电路中存在RC滤波,通过设置晶体管合理的宽长比,使其与晶体管间隔的节点的电平在SEU期间不变化,保持原电平状态,从而使电路具有抗动态SEU的能力。Spectre仿真结果表明,改进的D触发器既具有抗动态SEU能力,又保留了DICE抗静态SEU较好的优点,其抗单粒子翻转效果较好。

单粒子翻转;DICE;D触发器;静态SEU;动态SEU

1 引言

随着航空航天事业的飞速发展,各类电子器件更多地应用在环境非常恶劣的空间中,如人造卫星、空间站、宇宙飞船等的控制系统。高辐射环境中的高能粒子在穿过电子器件的敏感区时,其轨迹上沉积的电荷被器件电极收集,引发单粒子效应[1~3],造成器件逻辑状态的改变或器件的损坏。为此,提高电路的抗辐照加固能力至关重要。

随着电路工艺特征尺寸的降低和集成度的提高,SRAM存储单元的节点电容和工作电压稳步下降,使得更小能量的粒子也能引起存储单元的翻转[4~5]。对单粒子翻转的加固方法很多,系统级加固主要通过逻辑判决对已经发生错误的信息进行纠错和检错,如三模冗余技术等;电路级加固采用增加冗余的方法进行加固,如DICE技术等。三模冗余技术利用三个功能相同的模块和表决器来屏蔽错误[6],抗动态SEU能力较强,但抗静态SEU能力不足,并且三模冗余技术带来了面积增大、功耗增加等不可回避的问题。DICE技术在存储单元中增加冗余的存储状态,利用“状态恢复”反馈电路来恢复翻转的数据,抗SEU能力较强[7]。

在时序电路中,由于存在反馈信号,如果节点发生翻转,通过反馈线,电路会锁存该节点翻转后的状态值,使时序电路状态发生错误,从而影响整个电路的正确性[8~9]。触发器是电路中较常使用的时序器件,所以本文以D触发器单元结构作为抗辐照加固的研究对象。由于普通D触发器抗静态、动态SEU的能力较弱,DICE结构抗静态SEU的能力较强,但抗动态SEU的效果较差,针对该问题,本文设计了改进DICE结构的主-从型D触发器。

2 主-从型抗辐照D触发器设计

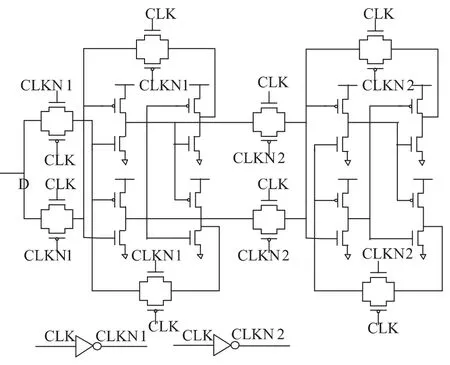

2.1基于DICE结构的主-从型D触发器

根据主-从型D触发器的电路结构,在高辐射环境下,普通D触发器并不具备抗SEU能力,而DICE结构电路因其较强的抗SEU能力而广泛应用在抗辐照加固的设计电路中[5],为此将主-从型D触发器与DICE结构电路结合,设计如图1所示的基于DICE结构的主-从型D触发器。

图1 DICE结构的主-从型D触发器

主从锁存器均采用DICE结构作为基本单元,用来提高单元电路的抗SEU翻转阈值,进行抗静态SEU加固[7]。数据输入端插入钟控反相器,以降低功耗。D触发器的时钟输入端插入两个相同的反相器,分别产生反相的时钟信号CLKN1和CLKN2。相对独立的两个时钟信号,增强了电路抗单粒子瞬态脉冲的能力。当其中一个反相器受到瞬态脉冲干扰时,另一个反相时钟信号不受其干扰,从而保证错误信息不会被写入DICE存储单元[8]。

DICE存储单元中锁存的数据通过反相器输出,使DICE存储单元与外界隔离,从而提高存储数据的正确性。该电路设计思路简单,相对于其他抗SEU方法芯片面积较小、功耗较低;缺点是对动态SEU没有加固能力。

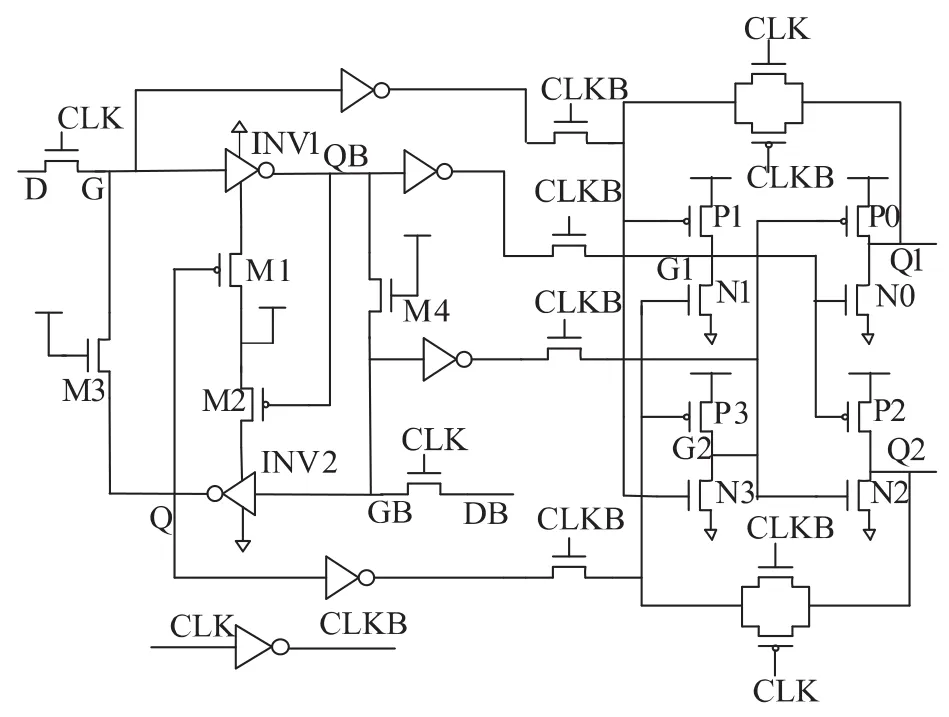

2.2改进DICE结构的主-从型D触发器

研究表明DICE具有较强的抗静态SEU能力,但抗动态SEU能力较弱[4~5]。为此本文对DICE结构的主-从型D触发器电路进行了改进,改进后的结构如图2所示。

图2 改进DICE结构的主-从型D触发器

主锁存器中,晶体管M3和M4作电阻使用,使得电路中存在RC滤波。基于RC滤波技术就是在锁存器反馈环路中增加一个电阻,形成的RC滤波电路以消除其上的脉冲[11],这种方法的优点是设计简单,缺点是速度和功耗性能降低。4个节点G、Q、GB、QB中任意单节点发生翻转,通过设置M3和M4合理的宽长比,使其与晶体管间隔的节点的电平在SEU期间不变化,保持原电平状态。晶体管M1和M2处于导通或截止状态时,决定电源能否通过反相器INV1和INV2对相连节点进行充电。由于4节点的特殊冗余结构,在SEU结束后,相邻节点通过充放电的形式将发生翻转的节点恢复原电平状态[12]。

从锁存器采用DICE存储单元,用来提高单元电路的抗SEU翻转阈值,进行抗静态SEU加固,其基本思想是采用冗余结构备份存储的数据。DICE存储单元的4个节点相互隔离,并且相互锁存,任意单节点发生翻转时,利用其他3个节点的正确状态通过反馈回路恢复翻转节点的状态值[7~8]。

该设计中,主锁存器采用抗静态、动态SEU设计,从锁存器保留原来的DICE结构,使电路既具有抗动态SEU能力,又保留了DICE面积小、功耗低的优点。

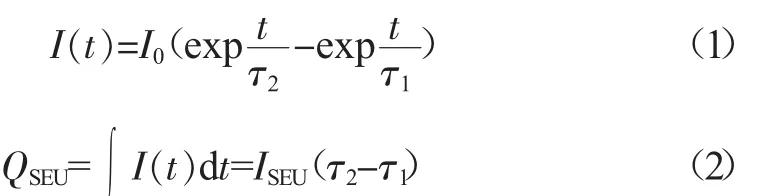

3 单粒子效应仿真

本文主要使用Cadence组件Spectre来进行软错误的故障注入以及延迟和能量的估算。软错误的故障注入通常使用双指数模型的干扰电流源,估算模型如公式(1)、(2)所示[13]。

公式(1)中的QSEU是SEU在电路内部某个节点的电荷,ISEU是SEU在这一节点由淀积电荷形成的干扰电流,τ2代表电荷聚集时间常数,τ1代表离子轨迹建立常数。τ2和τ1的取值和工艺、模型等都有密切联系。相关文献[14]提供τ2和τ1的取值情况,本文中取τ2=200ps,τ1= 50 ps。如果所收集的电荷量达到这一临界值,工作电压达到翻转的阈值电压,存储节点的值发生翻转。

3.1主锁存器的SEU仿真与分析

3.1.1主锁存器抗静态SEU仿真

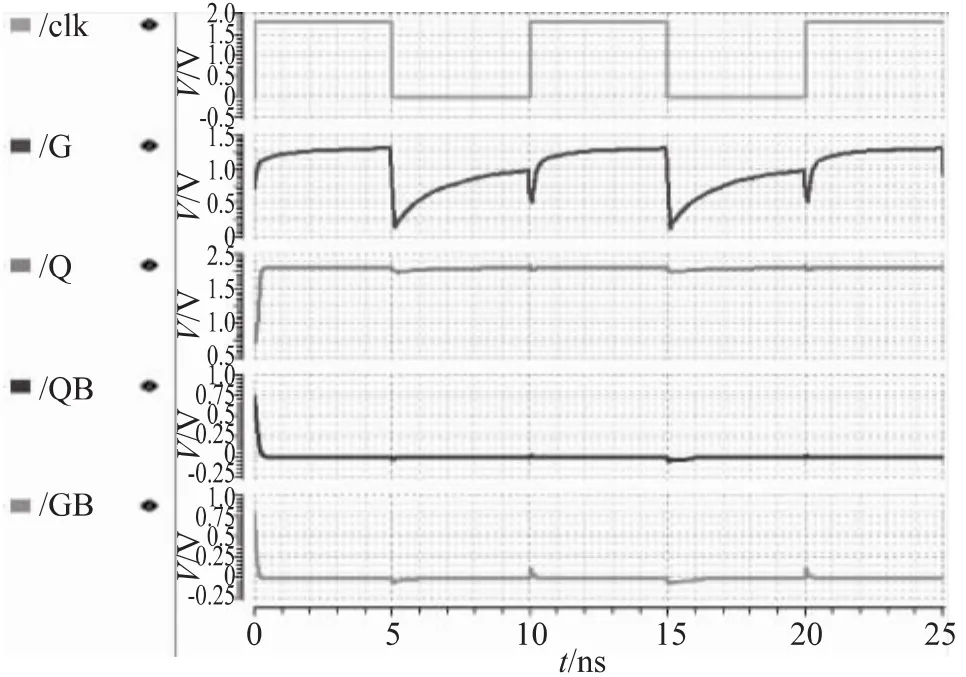

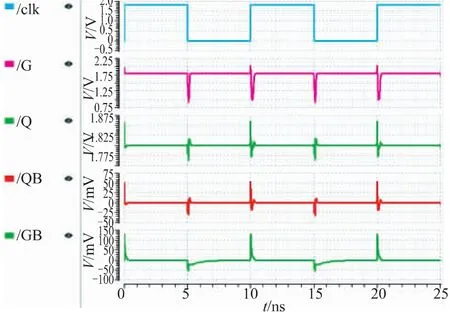

假定G=1,QB=0,GB=0,Q=1。如果节点G发生了SEU,此时G=0,因为晶体管M4起电阻的作用,这样存在RC滤波。通过合理设置M4的宽长比,使得节点Q的电平在0.5 ns的SEU期间不变化,这样Q仍然为高电平,所以此时M3关断。这样电源无法通过反相器INV1对节点QB充电,所以QB仍为0,从而节点GB也仍为0。当节点G的SEU结束后,节点Q通过M4对节点G充电,使得节点G恢复到高电平,电路仿真如图3所示。

图3 节点G发生翻转的仿真

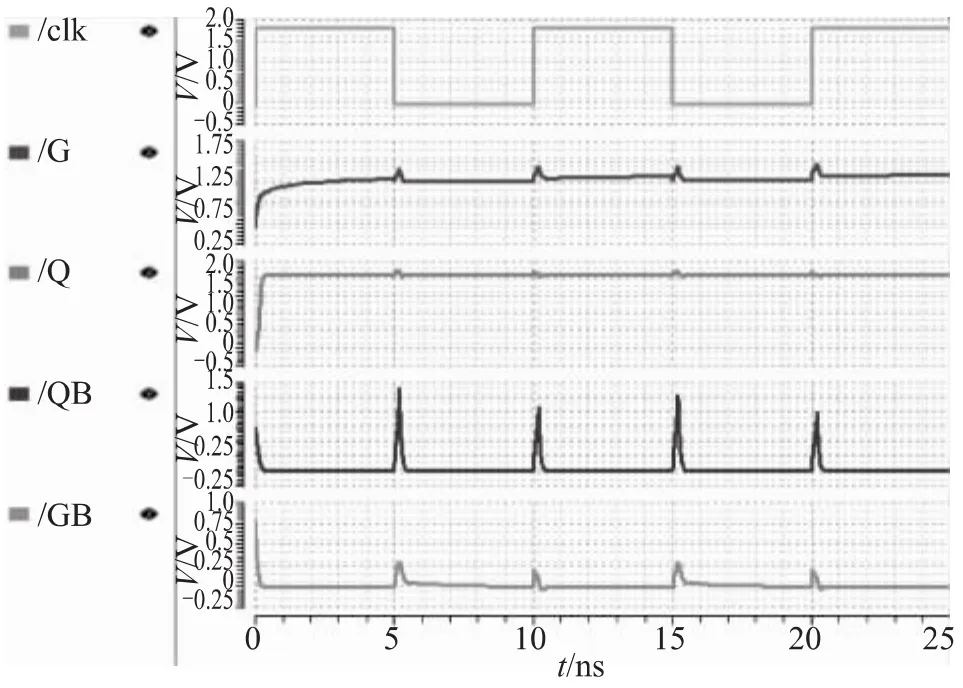

如果节点QB发生SEU,即QB=1。因为在节点QB对GB充电的路径中,晶体管M3起电阻的作用,所以存在RC滤波。在0.5 ns的时间内,节点GB电平不变,从而节点Q、G电平都不变。当节点QB的SEU结束,节点G通过反相器INV1迫使节点QB恢复低电平,电路仿真如图4所示。

图4 节点QB发生翻转的仿真

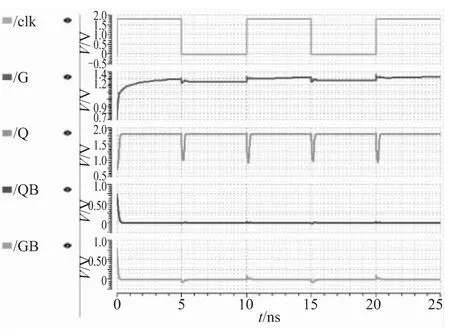

如果节点Q发生SEU,即Q=0。由于晶体管M4作电阻,起RC滤波的原因,节点G不受影响,另外2个节点也不受影响。当节点Q的SEU结束时,通过反相器INV2,Q点恢复到高电平,电路仿真如图5所示。

图5 节点Q发生翻转的仿真

如果节点GB发生SEU,即GB=1。因为晶体管M3起电阻的作用,这样存在RC滤波。在0.5 ns的时间内,节点QB电平不变,从而节点Q、G电平都不变。当节点GB的SEU结束,节点Q通过反相器INV2迫使节点GB恢复低电平,电路仿真如图6所示。

同理,根据电路的对称性可知当GB=1、Q=0、G=0、QB=1时,电路也具有抗静态SEU的能力。

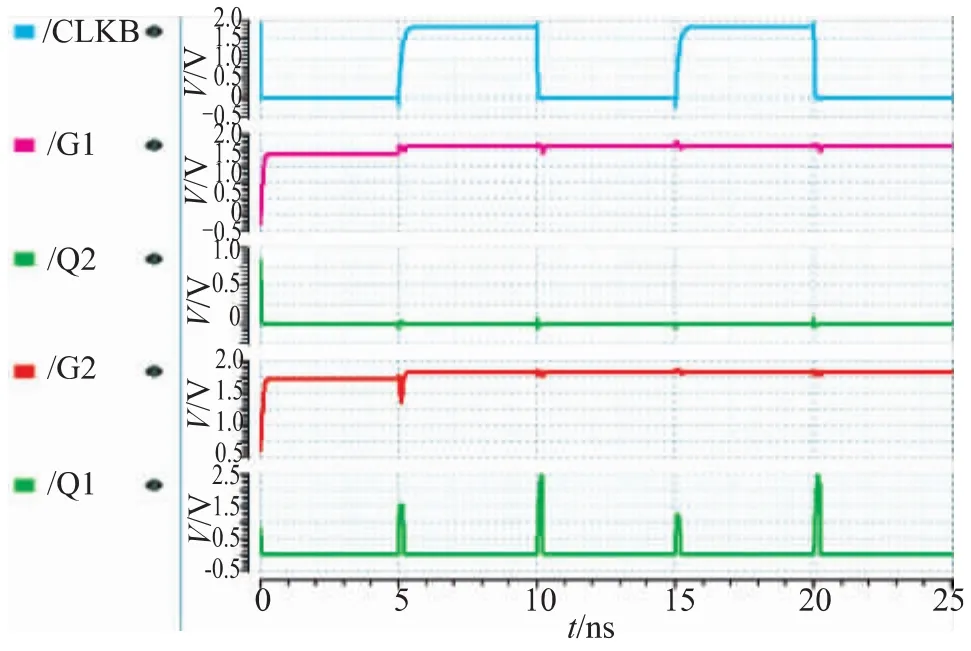

3.1.2主锁存器抗动态SEU仿真

如果在晶体管M3关断前的时间内,D端发生了SEU。假设D端的初始值为1,发生SEU后D端变成0。由于此时内部的4个节点的数据都已经建立起来,D端的SEU会使节点G的电平也从1变成0。由上面的静态SEU分析可知节点G的变化不会影响其他节点。当D端的SEU结束或者晶体管M3关断后,G点会恢复到原来的电平,电路仿真如图7所示。

图6 节点GB发生翻转的仿真

图7 D端发生翻转的仿真(D初始值为1)

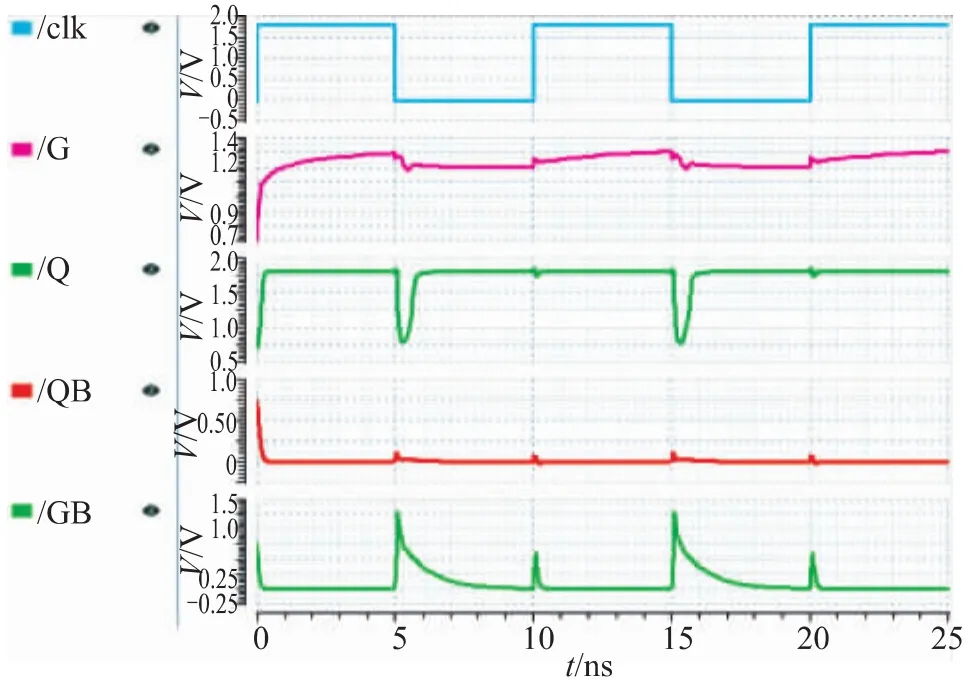

D端的初始值为0,发生SEU后D端变成1。在D端发生SEU前,电路内部4个节点情况为G=0、QB=1、GB=1、Q=0。由于D端发生了SEU,导致节点G变为1。INV1的NMOS管子被打开,此时节点QB电平往下降。由于RC滤波的存在,节点QB电平不能传输到节点GB。同样由于RC滤波的存在,节点G的1也不能传到节点Q。当D端的SEU结束或者晶体管M3关断后,经过一段时间后节点Q把低电平通过M4传递到节点G,使节点G恢复到低电平,节点GB通过INV2使得节点QB恢复到高电平,电路仿真如图8所示。

同上分析,当节点DB发生动态SEU,D锁存器也不会保存错误的值。所以该主锁存器除了能抗静态SEU外,还能抗动态SEU。

图8 D端发生翻转的仿真(D初始值为0)

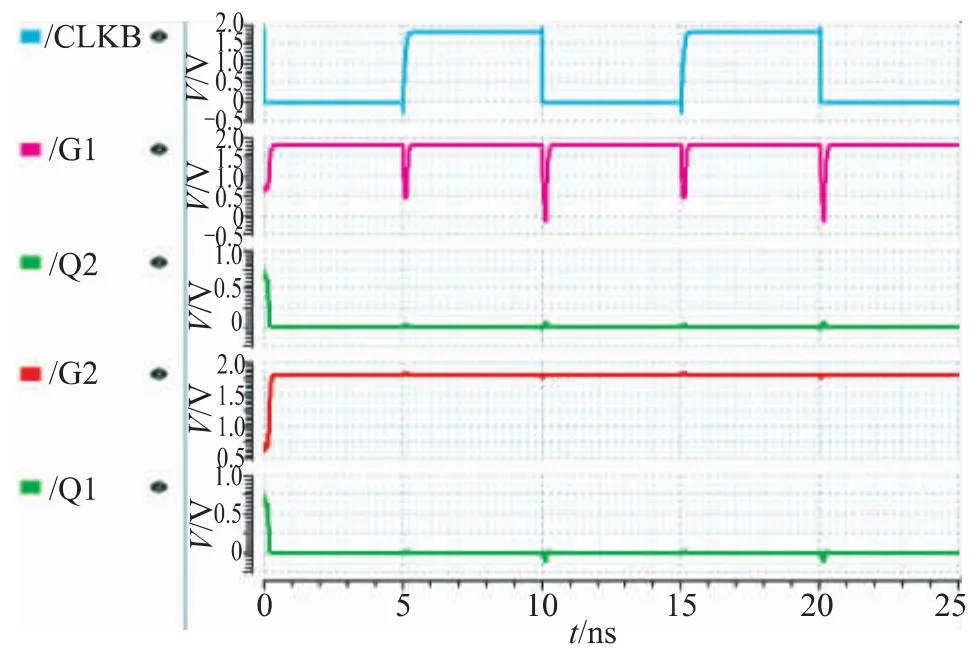

3.2从锁存器的SEU仿真与分析

假定4个节点的初始值为:G1=1,Q1=0,G2=1,Q2=0。

若节点G1发生SEU,此时G1=0。N0关断,Q1保持原来的电平;P2管打开,节点Q2的上拉管打开,Q2的电平发生翻转变成高电平。因为节点Q2与P3管的栅极相连,所以P3管被关断,此时节点G2处于三态。当G1点SEU结束,此时该节点的电平从低电平往上升,导致节点Q2电平往下降。最后稳定时,节点G1为高电平,节点Q2为低电平。4个节点的电平在经历了节点G1的SEU后,最后回到初始电平,仿真结果如图9所示。

图9 节点G1发生翻转的仿真

若节点Q1发生SEU,此时Q1=1。P1关断,G1保持原来的电平;N3管打开,G2的电平发生翻转,即G2=0。因为G2与N2的栅极相连,所以N2管被关断,此时Q2处于三态。当Q1点SEU结束,4个节点的电平最后回到初始电平,仿真结果如图10所示。

图10 节点Q1发生翻转的仿真

如果在节点G2、Q2发生SEU,最后4个节点都会保持初始电平。同上面的分析,当4个节点保存的值为G1=0、Q1=1、G2=0、Q2=1时,电路也具有较强的抗SEU能力。

由反相时钟信号控制的4个NMOS管做开关使用,在其即将关断时,主锁存器的4个输出端,即G、GB、Q、QB中的某一个发生了SEU,当SEU结束后电路会恢复初始值。所以在结束SEU后,从锁存器能够恢复正确的值。所以,该从锁存器电路也具有抗动态SEU的能力。

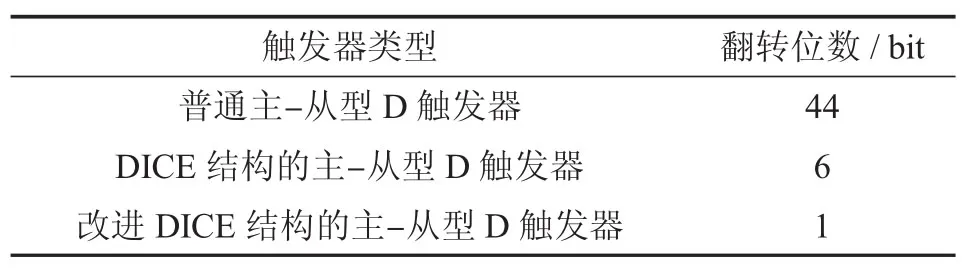

3.3仿真统计

对3种D触发器轰击100次,其翻转位数统计如表1所示。普通D触发器没有进行加固,翻转了44位,其翻转位数最多,抗单粒子翻转性能最差;本文设计的改进DICE结构的主-从型D触发器的翻转位数最少,抗单粒子翻转性能优于普通主-从型D触发器和DICE结构的主-从型D触发器。

表1 3种D触发器的翻转位数统计

4 结束语

根据Spectre仿真结果,本文设计的改进DICE结构的主-从型D触发器抗静态SEU、动态SEU的效果较好,抗单粒子翻转的能力较强。设计中,主锁存器采用抗静态、动态SEU设计,从锁存器保留DICE结构,增强其抗单粒子瞬态脉冲的能力,功耗较低。

[1]KimT,JeongY,YangK.Low-powerhigh-speed performance of current-mode logic D flip-flop topology using negative-differential-resistance devices[J].Circuits,Devices&Systems,IET,2008,2(2):281-287.

[2]李海霞,李卫民,谭建平,等.一种低功耗抗辐照加固256 kB SRAM的设计[J].微电子学与计算机,2007,24(7): 142-145.

[3]胡明浩,李磊,饶全林.基于RHBD技术CMOS锁存器加固电路的研究[J].微电子学与计算机,2010,07:206-209.

[4]俞剑.双立互锁存储单元单粒子效应加固方法研究[J].计算机工程,2013,3:272-278.

[5]周恒,李磊.一种加固SRAM单元DDICE及外围电路设计[J].微电子学与计算机,2015,05:68-72.

[6]张丹丹,杨海钢,李威,等.DICE型D触发器三模冗余实现及辐照实验验证 [J].半导体集成电路,2014,39(7): 495-500.

[7]田浩,杨洪强,马骁,等.基于DICE结构的主-从型抗辐照触发器设计[J].微电子学,2013,2:65-69.

[8]张英武,袁国顺.一种抗单粒子全加固D触发器的设计[J].固体电子学研究与进展,2009,03:403-406,464.

[9]李玉红,赵元富,岳素格,梁国朕,林任.0.18 μm工艺下单粒子加固锁存器的设计与仿真 [J].微电子学与计算机,2007,12:66-69.

[10]赵金薇,沈鸣杰,程君侠.改进型抗单粒子效应D触发器[J].半导体技术,2007,01:26-28,32.

[11]姚茂群,张立彬,耿亮.电流型CMOS脉冲D触发器设计[J].电子与信息学报,2014,09:2278-2282.

[12]宋红东,胡晨,杨军.一种用于高可靠性同步器电路的D触发器设计[J].电子器件,2003,01:99-103.

[13]Sharma K G,Sharma T,Singh B P,Sharma M.Modified SETD-FlipFlopDesignforLow-PowerVLSI Applications[C].DevicesandCommunications (ICDeCom),2011 International Conference,2011:1-5.

[14]Messenger G C.Collection of charge on Junction Nodes from Ion Tracks[J].IEEE Transactions on Nuclear Science,1981,29(6):2014-2031.

Design of Radiation Hardened D Flip-Flop Based on DICE

SUN Jing1,2,CHEN Zhenjiao2,TAO Jianzhong1,2,ZHANG Yuhan2

(1.Jiangnan University,Wuxi 214062,China;2.China Electronics Technology Group Corporation No.58 Research Institute,Wuxi 214035,China)

In the paper,the research of master-slave type D flip-flop radiation hardening method facilitates the improvement of circuit structure of the DICE-based type D flip-flop.The master latch adopts the design of anti-static and anti-dynamic SEU while the slave latch retains the original DICE structure.The master latch generates RC filter using transistors as resistance and enables anti-dynamic capability by setting reasonable length/width ratio.The Spectre simulation results show that the improved D flip-flop is equipped with strong anti-dynamic SEU capability and retains good anti-static SEU capability.

single event upset(SEU);DICE;D flip-flop;static SEU;dynamic SEU

TN402

A

1681-1070(2016)08-0019-05

2016-4-12

孙敬(1990—),女,安徽宿州人,硕士研究生,研究方向为抗辐照加固SRAM设计。