数字化变电站信号采集合并单元设计

炎 云,王 醒

(1.延津县供电公司,河南 延津453000;2.深圳供电局有限公司,广东 深圳 518000)

数字化变电站信号采集合并单元设计

炎 云,王 醒

(1.延津县供电公司,河南 延津453000;2.深圳供电局有限公司,广东 深圳 518000)

针对IEC61850标准规定的所有功能要求进行分析,建立了完善的通信模型,并使用模块化设计方法,从硬件和软件两个方面进行了设计工作。在硬件方面,根据新式电子互感器的数字输出标准,提出了ARM+FPGA的解决方案。在软件方面,阐述了合并单元的通信模型的建立,插值算法的原理和对数据进行同步的过程,还有IEC61850对以太网帧结构的定义。

IEC61850;合并单元;插值算法;FPG

作为电子式互感器的输出接口,合并单元控制各路的电子式互感器采样,接收它们输出的数字信号,并将采样值进行同步处理,将处理后的数据照约定的数据格式打包,通过以太网发送给保护和测控设备。在 IEC60044中最早提出了合并单元的概念,IEC61850-9并没有对合并单元进行新的定义,而是将合并单元的概念进行了深化,把合并单元作为逻辑设备融入到IEC61850的整个体系中[1-3]。

对于合并单元解决方案的争论主要集中于以下方面:针对实现的功能不同对合并单元进行模块划分工作,依据合并单元所要完成的相关功能,将合并单元划分为多路数据的采集和存储、同步信号的接收和同步采样的完成、以太网网络通讯模块[4-5];同步信号的接收和同步采样的实现方案;多路数据的采集和存储模块的实现方案,该模块是合并单元接收电子式互感器数字信号的接口,主要完成互感器数据的接收和存储[6];数据处理模块的实现方案;网络通信模块的实现方案。要实现上述设计方案,必须借助三种关键技术:(1)嵌入式处理器技术和实时操作系统技术。(2)FPGA/CPLD可编程逻辑器件技术。(3)GPS技术。

1 IEC61850 合并单元设计方案分析

1.1IEC61850协议浅析

IEC61850标准协议是唯一主要应用于变电站通信网络和通信系统的国际化标准,通过规范变电站自动化系统的输出,实现设备的无缝连接。正因为它的重要地位,各大电力设备生产商、运营机构都在致力于研究其产品与这一标准协议的接轨问题。

变电站通信网络和系统协议 IEC61850 标准草案提出了变电站自动化系统信息分层的概念,针对变电站自动化通信网络与协议将变电站通信系统划分为 三个层次,分别是变电站层、间隔层和过程层[7],并且定义了层和层之间的通信接口。一次设备的电压电流互感器对电网进行采样,数字化和集成化的信息加入到变电站自动化体系的这一过程对变电站自动化系统结构的更深层次的发展具有深刻的意义。IEC61850协议关于变电站通信系统规定了两种协议方式,分别是IEC61850-9-1 和IEC61850-9-2,但都是建立在 10Mbps/100Mbps 以太网的基础上,所以也产生了以下三种可能出现的通信系统拓扑结构。首先是点对点连接和过程总线相结合的结构,其次是过程总线共享互感器数据的结构,最后是过程总线和站内总线统一的结构模型。

无论在数字化变电站采用何种结构,互感器的采样信息的传输都需要遵循的网络协议,都需要按照 IEC61850 的要求。

1.2合并单元的功能要求

不论电子式电流互感器还是电子式电压互感器,采样测量值都要经过二次转换器进行转换后,才能送往合并单元。每个互感器都要占用一个物理接口,一台合并单元汇集多个互感器的信息,就要具备相应的物理接口数量,合并单元连接互感器最多可以达到12个。合并单元从GPS模块中获取同步秒脉冲,修正本地系统的时钟,给各路互感器采样数据提供时间标准[1]。

收稿日期:2016-03-28

作者简介:炎云(1982―),女,河南新乡人,工程师,主要从事电力系统及自动化研究。

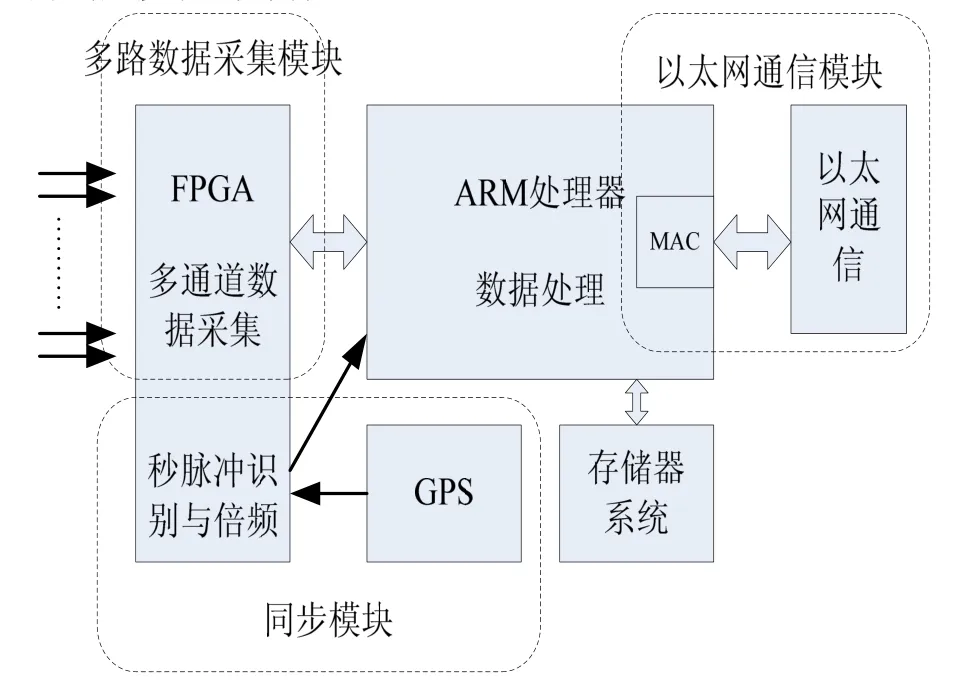

通过对合并单元定义的分析,其功能主要表现为以下三个方面:多路数据的采集和存储、同步信号的接收和同步采样的完成、网路通信。合并单元的功能模块结构如图1所示。

图1 合并单元功能模块框图

同步模块的功能是接收GPS产生的同步秒脉冲信号,对该信号进行识别修正本地时钟,对多路的电流、电压互感器采样数据进行同步化处理,在IEC60044-8中列举了两种同步化方法,即发送同步采样脉冲法和插值计算法。多路数据采集模块,合并单元需要多个接口来接收各路电子式互感器的采样数据。送入合并单元的电子式互感器的输出所包含的内容,在IEC60044-7/8标准中有详细的规定[2-3],包括测量用三相电流、保护用三相电流、中性点电流这7组电子式电流互感器的数字输出和三相电压、中性点电压和母线电压这5组电子式电压互感器数字输出。网路通信模块合并单元在完成对某一环节的一次侧电子式互感器采样数据的接收和同步处理以后,需要根据 IEC61850-9定义的帧格式将各路采样数据打包,通过以太网发送给继保设备。本设计选用的处理器 STM32F107XX带有以太网介质访问控制模块(MAC),可以通过物理层驱动 PHY,直接连接以太网。

2 合并单元硬件设计方案

2.1硬件设计总体方案

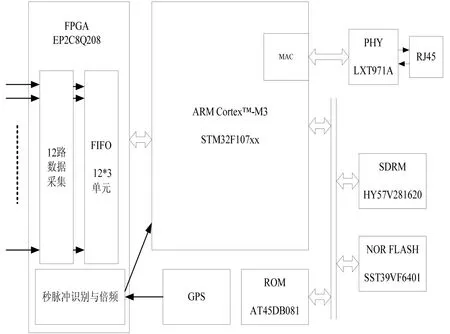

前面提到合并单元的定义和功能,根据合并单元的功能需要,本设计选用 ARM+FPGA的解决方案。由FPGA芯片实现12路数字通道输入和存储,存储的数据由 ARM芯片来进行插值算法处理,处理数据结果通过处理器芯片自带 MAC发送到以太网。具体的系统硬件框图如下图2所示。

图2 合并单元系统硬件框图

整个系统的运行由ARM芯片STM32F107来进行控制。GPS模块通过授时功能发出秒脉冲,送给FPGA芯片EP2C8Q208,由FPGA中的秒脉冲的识别电路来进行识别,如果识别成功,则由FPGA中的倍频电路将1Hz的脉冲进行4K的倍频,做为电子式互感器数据采集的采集同步时钟。

2.2主处理器的选择

由于系统的功能实时性要求比较高,需要实时操作系统来做为软件平台,所以本方案选用具有ARM内核的处理器STM32F107来做为系统内核。

新STM32的标准外设主要有两个十二位DA(数模转换器) (快速交替模式下 2M sample/s)和十个 T(定时器),具有两个十二位 AD(模数转换器),可以满足多路模拟量处理。另外,处理器还具有2个I2C接口、5个USART接口和3个SPI端口和高品质数字音频接口IIS,可以满足各种工业环境中与其他硬件设备的连接。此外STM32F107拥有CAN2.0B接口两路,全速USB(OTG)接口,以及以太网10/100 MAC模块,适用于民用电子产品的开发和应用。此芯片常常应用在医疗机构、工业控制、手持式设备、个人家庭音响和电机控制产品需求。

2.3存储器系统

本设计所选的处理器 STM32F107虽然已经具备256KB Flash和64KB的SRAM存储空间,但是由于实时操作系统和大容量的数据处理的需要,还需扩展程序存储器和数据存储器。STM32F107的地址总线宽度为32位,寻址范围可达4G的线性地址空间,STM32F107提供了必要的存储器控制信号来访问外部的存储器,数据字节以小端格式存放在存储器中。

本设计方案中选用的程序存储器为 NOR FLASH芯片SST39VF6401,它具有4M16位容量,足以满足搭载实时操作系统和将来系统升级的需要。

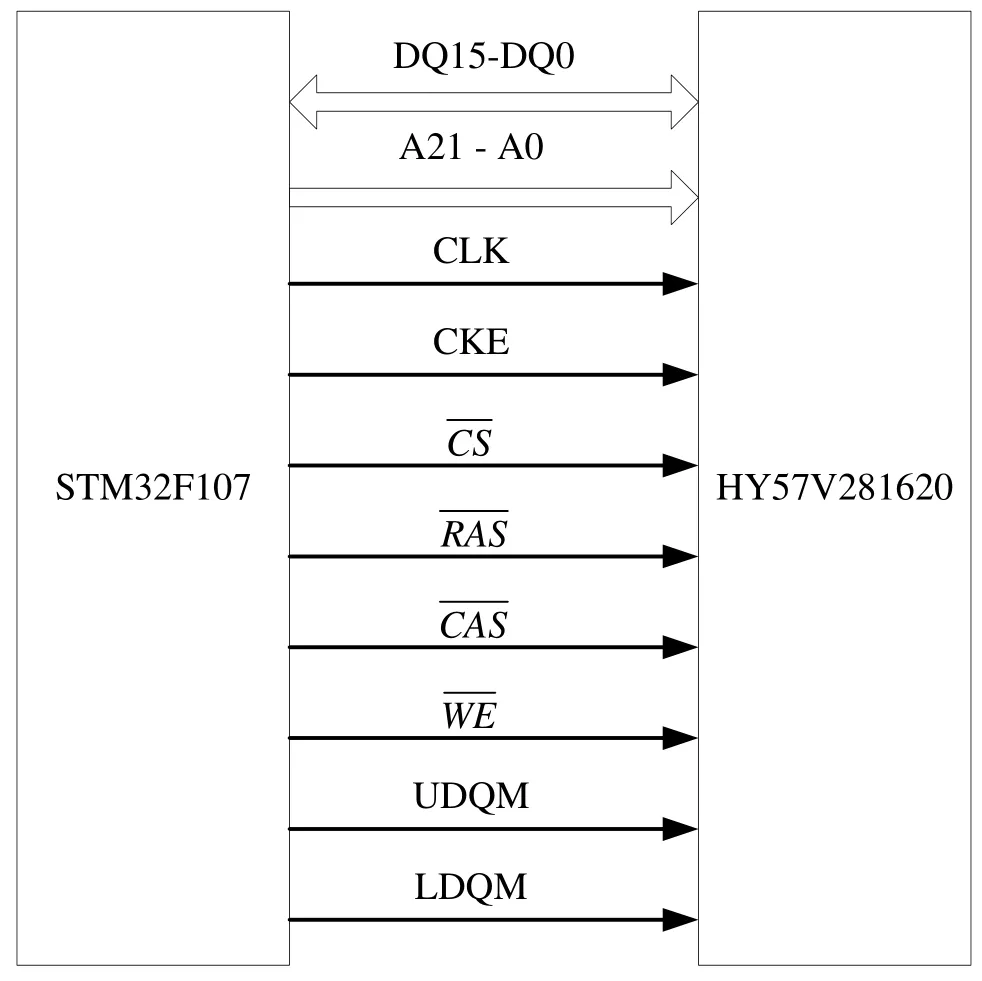

本方案中选用的数据存储器为 SDRM芯片HY57V281620,该芯片与STM32F107的接口电路如图3所示[8]。

2.4FPGA

合并单元要接收处理最大 12路二次转换器过来的电流、电压值,继电保护对数据的误差要求有一定限制,最大不得超过4微秒。CPU间的数据传输较多,集成度低。现场可编程门阵列具有丰富的触发器与输入输出引脚,集成度高,设计特定用途电路的时间短、软件编程简易、实现速度快、是现实多路接收的最佳选择。基于以上的特点,在硬件设计上我们采用了FPGA作为实现对合并单元中数据的接收模块,很方便地实现同步功能。

2.5以太网接口

电子式互感器采样数据由合并单元接收,并经过同步处理,处理完成后,按照 IEC61850-9-1定义的帧格式将各路互感器传输的采样数据打包,并通过以太网发送给继保设备。

图3 HY57V281620接口电路示意图

3 结语

本文以 IEC61850标准为手段,充分利用先进的嵌入式系统的新理念,选用具有 ARM内核的处理器STM32F107做为系统内核,为系统各种功能的实现提供了有力的平台。利用μC/OS II实时操作系统的特点,将任务模块化处理,有力解决了软件程序量大、结构复杂等困难。使用二阶插值算法做为数据同步方法,也简化了电路接线的复杂程度。

(责任编辑 吕春红)

[1] IEC61850-9-1.Communication Networks and Systems in Substations- Part9-1:Specific Communication Service Mapping(SCSM)- Sampled analogue values over serial unidirectional multidrop point to point link[Z]. 2003-01-01.

[2] IEC60044-7.Instrument Transformers-part 7:Electronic Voltage Transducer[Z].2002-01-01.

[3] IEC60044-8.Instrument Transformers-part 8:Electronic Current Transformers[Z].2002-01-01.

[4] 曹团结,尹项根,张哲,等.电子式互感器数据同步的研究[J].电力系统及自动化学报,2007,9(2):108.

[5] 徐雁,向珂,肖霞. 一种基于 FPGA&DSP的电子式互感器数字接口实现方案[J].高压电器,2006,42(3):208-210.

[6] A. Apostolov, F. Auperrin, R. Passet, et al. IEC 61850 Process Bus based Distributed Waveform Recording. In:IEEE Power Engineering Society General Meeting[Z]. 2006-01-01.

[7] 刘建峰,李开成,张昌华,等.基于 ARM的电子式互感器合并单元的研究[J].电测与仪表,2008,45(508):49-52.

[8] LXT971A,3.3V Dual-Speed Fast Ethernet PHY Transcei[Z]. 2012-09-05.

Digital Substation Design of Signal Acquisition Merge Cells

YAN Yun,et al

(Yanjin Power Supply Company, Xinxiang 453000, China)

For the functions of the IEC61850, this paper built a perfect communication model by using modular design approach. The design work included hardware aspect and software aspect. On the hardware side, according to the standard of digital output of the new electronic transformer, the paper provided ARM&FPGA solution. On the software side, the author elaborated on how to build the communication model of merging unit, the principle of the interpolation algorithm and data synchronization process, as well as the definition of Ethernet frame structure in IEC61850.

IEC61850; merging unit; interpolation algorithm; FPGA

TM63

A

1008–2093(2016)03–0011–03