基于UVM的FPGA测试技术的研究

曾清乐 宋文强 李敬磊

(工业和信息化部电子第五研究所,广东 广州 510610)

基于UVM的FPGA测试技术的研究

曾清乐 宋文强 李敬磊

(工业和信息化部电子第五研究所,广东 广州 510610)

FPGA设计规模和复杂度的急剧增加使得对其测试的难度提高。本文研究UVM(通用验证方法学)架构和特点,采用UVM搭建验证平台,以TS101作为上位机、FPGA作为其接口控制功能为例,验证FPGA逻辑设计的正确性。

现场可编程逻辑器件;通用验证方法学;待测设计

1 引言

FPGA是英文Field Programmable Gate Array(现场可编程门阵列)的缩写,是在GAL、CPLD等可编程器件的基础上进一步发展的逻辑器件,其应用越来越广泛,由FPGA器件所实现的功能正逐渐取代以往的传统软件,在现代电子系统中扮演着越来越重要的角色,被广泛地应用于航空、航天、通信、汽车工业等领域。随着FPGA应用领域的扩展以及其重要性的提高,其可靠性就变得越来越突出,因此对FPGA的测试验证将变得尤为重要。通用验证方法学(UVM,Universal Verification Methodology的缩写)起源于OVM(Open Verification Methodology),是由Cadence、Mentor和Synopsys联合推出的新一代验证方法学。UVM具有可配置、可复用的特点,可产生受约束的随机化激励,以达到对系统的充分验证。

本文以TS101为上位机、FPGA作为其接口控制功能为验证对象,使用基于System Verilog语言[1]的UVM验证方法学构建验证平台,完成验证需求,提高了验证效率和平台的可重用性。

2 UVM介绍

2.1 UVM验证方法概述

UVM验证平台[2]由一系列可重用的通用验证部件(UVC,Universal Verification Component)组成,包括数据包、驱动器、BFM(Bus Functional Mode)、序列发生器、监视器、代理、环境、记分板(Scoreboard)等。这些通用验证部件具有可配置、易使用、封装成型,以及可重用等优点。下面简要介绍各部件的作用:

数据包(Transaction/Sequence):是发送到驱动器(Driver)的激励事物,可以是普通数据包、总线事物、指令集等,可经过SystemVerilog约束随机化过程来产生,即激励信号;

驱动器(Driver)/BFM:是将由传输级模型(TLM,Transaction Level Modeling)产生的上层抽象化的数据流,根据特定的传输协议和传输时序转化成信号级发送给DUT(Design Under Test,待测试设计);

序列发生器(Sequencer):启动特定的Sequence,使其产生受约束的随机传输级数据;

监视器(Monitor):根据特定协议采集数据并转换成传输级模型发送给记分板(Scoreboard);

记分板(Scoreboard):比较输入与输出信号并给出比较结果;

代理(Agent):像一个虚拟的容器,将序列发生器(Sequencer)、驱动器(Driver)、监视器(Monitor)封装在一起;

环境(Environment):也像一个虚拟的容器,将代理(Agent)、记分板(Scoreboard)、数据包(Transaction/Sequence)封装在一起。

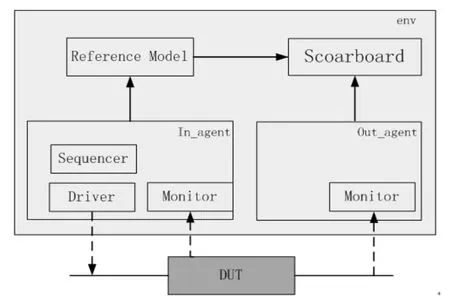

图1 典型的UVM平台示意图

图1[3]中实线连线表示验证平台不同组件之间的数据连接,虚线连线表示验证平台与DUT之间的物理接口连接。In_agent封装了Sequencer、Driver和Monitor,主要用于向DUT发送激励信号,过程为首先在Driver中申请一个item(Transaction),在Sequencer调度下由Sequence产生一个item(Transaction),再由Driver根据协议驱动到DUT端口上。同时In_agent的Monitor将产生的激励信号发送至Reference Model。Reference Model通常模拟DUT的行为。Out_agent的Monitor用于监测DUT的输出,并将数据发送至Scoreboard。Scoreboard将接收来自Reference Model和DUT输出的数据进行对比。

2.2 验证模块概述

本文中的验证模块是以TigerSHARC为DSP的上位机,FPGA主要作为其接口控制。DSP是采用慢速设备协议,通过配置寄存器设置等待周期为3;读写操作的译码过程为:首先给出存储器的片选信号,开始传送过程,同时发出地址信息。在下一周期里,RD或WR变为有效。对于写操作,Tiger-SHARC驱动数据;若为读操作,被测的DUT开始驱动数据。

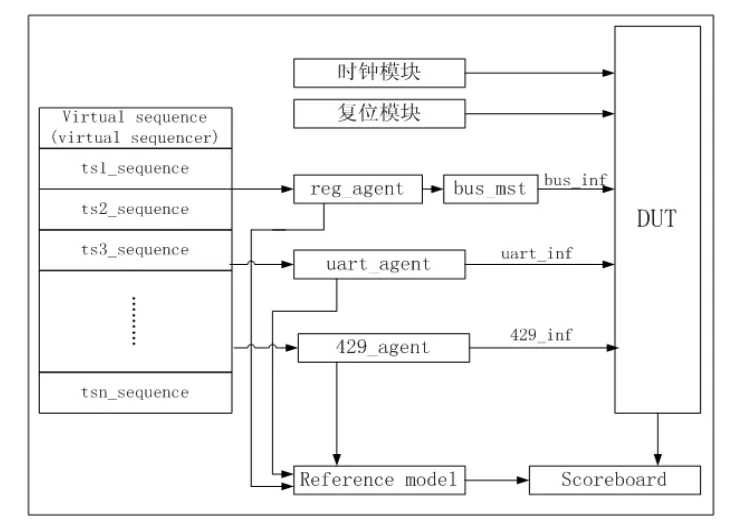

图2 验证模块接口关系图

表1 地址映射关系表

待测设计接口关系如图2所示,地址映射关系如表1所示。TS101(TigerSHARC 101)通过总线与DUT(FPGA)进行通信,需要通过串口输出数据时,首先TS101向DUT对应的FIFO中写入数据,再发送命令启动数据发送;DUT接收完串口数据后给出有效标记,TS101判断数据有效标记,标记有效时,读取数据。其中异步串口的波特率为5Mbps,每字节10bit,包括起始位1位,数据位8位,停止位1位,无奇偶校验位,空闲状态为高电平。TS101需要通过Arinc-429总线输出数据时,TS101向DUT对应的FIFO中写入数据,DUT通过Arinc-429总线输出;接收Arinc-429总线数据时,数据经DUT译码存储后,TS101通过总线读取。其中Arinc-429通信协议[4]是一种广泛应用于航空系统的串行通讯协议。该协议规定了差分传输,双极性归零码,最高100kbps。通信字为32bit,数据字间隔为4位,奇校验。

3 基于UVM的验证平台设计

从验证模块分析测试需求,搭建验证平台需要3个Agent,1个总线协议转换BFM(Bus Function Model)。第一个Agent命名为reg_agent,主要是用于产生地址、数据、读/写、片选信号;第二个Agent命名为429_agent,主要是用于产生429总线数据和接收429数据;第三个Agent命名为uart_agent,主要用于产生串口数据和接收串口数据;一个BFM是将reg_agent产生的总线数据,按照总线时序驱动到DUT端口。基于UVM验证平台的可重用性,Agent和BFM均设计为可配置的。例如对于串口uart_agent,继承uvm_sequence_item的类中成员变量数据长度和停止位长度可定义、奇偶校验的有效性、奇校验/偶校验、校验位长度,以及在接口驱动时可根据波特率调整驱动时序。对于reg_agent,继承uvm_sequence_item的类地址和数据位可参数化位数、成员变量读/写控制信号、数据、地址信号。对于BFM(Bus Function Model),主要是按照时序驱动数据到端口,定义为通用的类,根据不同的芯片时序驱动总线数据。

基于UVM的验证平台如图3所示。整个验证平台由外部脚本环境和内部UVM环境组成。脚本文件是控制平台的编译、仿真运行等。整个平台在虚拟Sequencer调度下,由Sequenc产生激励信号分别给 reg_agent、uart_agent和429_agent的Driver,驱动DUT的端口。Reference Model接收来自各个Monitor的信号模拟DUT的行为。Scoreboard接收来自DUT的输出结果与Reference Model输出结果进行比较,在本验证平台为比对输入与输出数据的一致性。

图3 基于UVM验证平台

4 验证结果及其分析

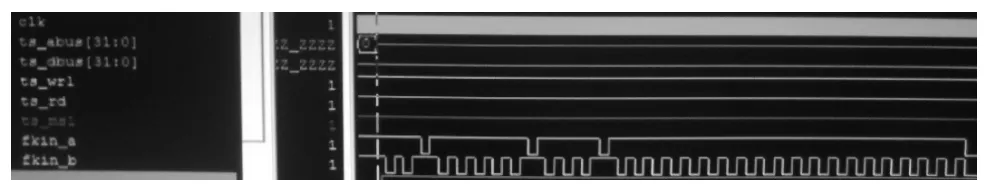

以DUT接收Arinc-429总线数据为例分析验证结果。通过429_agent模拟Arinc-429信号输入至管脚fkin_a、fkin_b,输入的数据确定为0x8820,输入的波形如图4所示。Arinc-429数据输入至 FPGA,FPGA接收并存储至地址0xFC0000F,模拟DSP读取。图5为DSP读取的结果,可以看出与输入一致。

图4 Arinc-429输入数据的波形

图5 DSP读取Arinc-429数据结果波形

其次,本文的验证平台将寄存器、DSP总线、UART串口和Arinc-429总线分离出来,构造出多个独立的agent,这样在对下一个项目进行验证的时候,每一个独立的子agent都可以被其他环境进行例化重用。而传统的测试床将所有信号集中在一个工程中,一旦项目中模块稍有变化便不能进行复用。因而,将信号进行分离的方法使得验证的环境变得更加灵活,同时极大地提高验证环境的重用性。

5 结束语

本文搭建的基于UVM验证平台的FPGA验证环境,具有高效性和可重用性。该验证环境针对不同的功能模块进行独立的、可配置的设计,从而提高了验证的效率。下一步研究方向是研究采用自动化的脚本语言,以及研究构建合理的人机交互界面生成验证环境,以便更有效地提高测试效率。

[1]钟文枫.SystemVerilog与功能验证[M].北京:机械工业出版社,2010.

[2]Accdlera.Universal verification methodology1.1 user's guide [M].Cadence Design Systems Inc.,Mentor Graphics Corp.,Synopsys Inc.,2011.

[3]张强.UVM实战[M].北京:机械工业出版社,2014.

[4]ARINC公司.ARINC429传输规范[Z].2002.

Research on FPGATesting Technology Based on UVM

Zeng Qingle Song Wenqiang Li Jinglei

(CEPREI,Guangzhou 510610,Guangdong)

Dramatically increasing in the scale and complexity of FPGA design makes it more difficult to be tested.This article studies the structure and characteristics of universal verification methodology(UVM).It uses UVM to set up the verification platform,taking the TS101 as the host computer and FPGA as function of the interface control,verifying the correctness of the FPGA logic design.

FPGA;universal verification methodology;DUT

TN407

B

1008-6609(2016)05-0065-03

曾清乐,男,湖南衡阳人,硕士研究生,工程师,研究方向:软件测试。