基于Nios II的动爆冲击波记录仪设计

刘雪飞 ,马铁华 ,王俊峰 ,尤文斌 ,崔 敏

(1.中北大学 电子测试技术国家重点实验室,太原030051;2.中北大学 仪器科学与动态测试教育部重点实验室,太原030051)

随着航天科技的发展及未来战争精确打击的需求,能够准确测试动爆冲击波的各项性能参数是衡量评估导弹战斗部毁伤效应的重要依据[1-2]。传统动爆冲击波记录仪多以微处理器 (单片机、ARM或DSP)为主控制器,或以微处理器与FPGA/CPLD相结合的方式[3-5]。上述硬CPU+FPGA的设计方案,设计者不仅要在微处理器的选型及与FPGA/CPLD相互匹配的过程中花费时间,且当系统的设计方案改变时,需再选器件及重新设计PCB板。

针对上述问题,提出了一种基于Nios II的动爆冲击波记录仪设计方案。该方案以SOPC技术为基础,将整个控制系统构建在单片FPGA(field programmable gate array)上,具有体积小、开发周期短、可靠性高等优点。

1 记录仪总体设计

1.1 系统结构组成

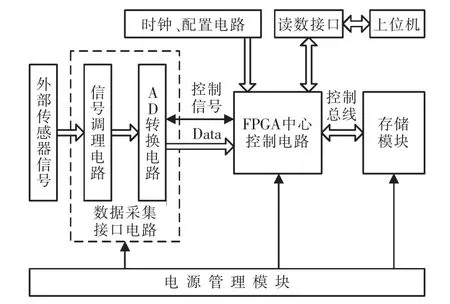

动爆冲击波记录仪结构组成如图1所示,包括中心逻辑控制电路、数据采集接口电路、Flash存储模块、时钟、配置电路、读数接口、电源管理模块。Nios II软核处理器为记录仪核心控制器,控制与协调整个测试系统中各部分的协作与运行。

图1 记录仪系统框图Fig.1 Block diagram of recorder system

在FPGA内用硬件描述语言VHDL设计AD逻辑控制、数据编码等功能。使用Quartus II工具的Megawizard Plug_In Manager设置相应的参数,构建4 KB的内部 FIFO来缓存数字量,并采取半满即读的方式,即FIFO中存储2 KB数据时,给出半满标志 HF。使用嵌入在Quartus II工具中的 SOPC Builder系统集成工具,从IP组件中定义和建立Nios II嵌入式系统。

1.2 接口电路

1.2.1 信号调理电路

为了前置单元能可靠记录被测信号,不对其它设备产生干扰,在模拟信号输入电路中加有过电压保护网络,保证在有效地记录被测信号的前提下不对被测信号造成任何干扰。调理电路如图2所示。

图2 信号调理电路Fig.2 Circuit of signal conditioning

1.2.2 启动存储信号接口

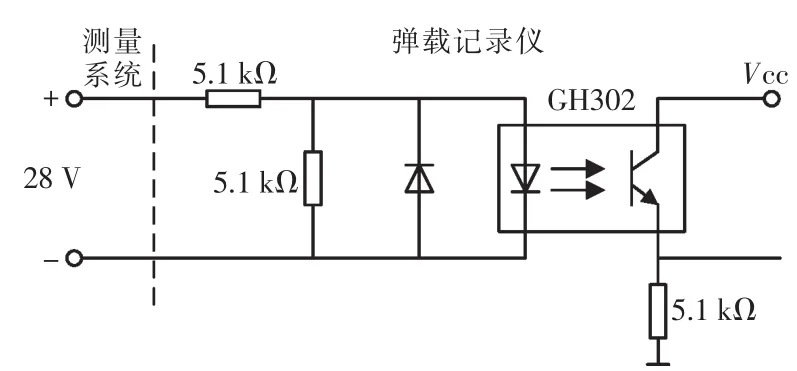

测量系统控制记录仪的启动存储信号为一高电平有效28 V电平信号,存储器收到信号后,顺序执行“擦除”和“开始记录”2个动作,接口电路如图3所示。

图3 启动存储接口电路Fig.3 Interface circuit of launch memory

1.3 存储模块

存储介质选用三星公司的K9WAG08UlA存储芯片。每片闪存有16384块,每块有64页,每页有2048 B写入区和64 B备用区,其典型编程周期为200 μs,典型擦除周期为1.5 ms。有效期内无效块≤320个。页是K9WAG08UlA存储芯片读写操作的基本单位[6]。

2 以Nios II为核心的SOPC设计

2.1 硬件平台设计

SOPC是一种灵活、高效的嵌入式系统硬件解决方案,是以 Nios II软核处理器为核心[7]。将Nios II软核处理器和功能模块集成到同一个现场可编程逻辑阵列FPGA上,构成一个可编程的片上系统,减少芯片使用数量,减小了电路板尺寸,提高了系统稳定性。

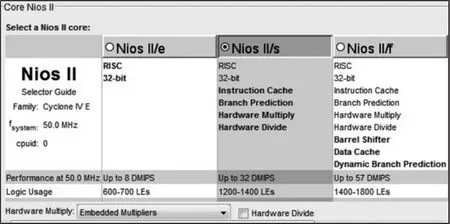

加入Nios II处理器时,设置进入Nios系统模块的时钟频率为50 MHz,Nios II处理器核的设置页面如图4所示。

Nios II嵌入式系统包含Nios II微处理器内核、JTAG 调试模块 jtag-uart、RAM IP 核、EPCS 控制器epcs_flash_controller、存储Flash接口、串行通信接口组件UART、并行输入/输出口(PIO)等。

图4 Nios II处理器核的设置页面Fig.4 Setting page of the II Nios processor core

2.2 系统SOPC软件设计

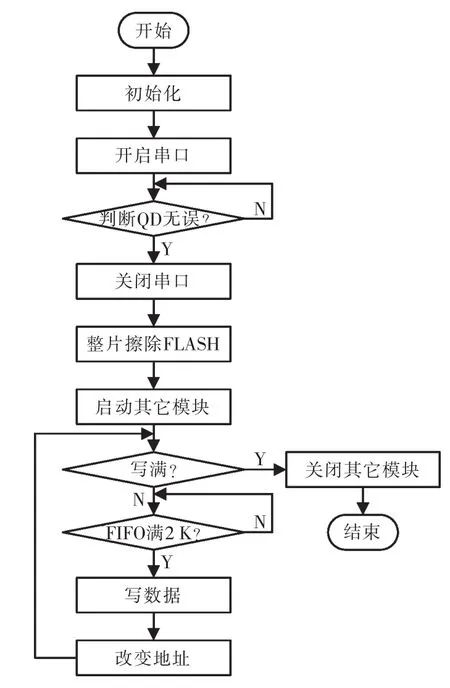

软件系统主要完成数据采集和数据存储命令的发送和控制。Nios II嵌入式系统的所有软件开发任务都是在Nios II集成开发环境(IDE)下完成的,并通过JTAG下载线下载到FPGA中运行。系统流程如图5所示。

图5 软核主程序流程Fig.5 Soft flow chart of main program

当系统上电或复位时,系统从串行配置器件EPCS16中读出用户数据,快速配置FPGA,将应用软件调到Nios II处理器上运行。Nios II软核处理器开始检测触发信号QD并判断,判断无误后对FLASH进行擦除操作,擦除结束后FPGA内部A/D控制模块提供A/D工作的时钟,同时Nios II软核处理器配置FLASH写数据的地址。配置完地址后发送写命令给FLASH芯片,向存储器FLASH写入数据。当数据记录完毕或闪存存满后,整个记录系统就退出数据采集,进入休眠状态。

采用C语言在Nios II IDE开发工具中实现控制数据读写和发送控制指令功能。

2.3 读数接口

通过在Nios II系统中集成通用的UART内核,以RS-232协议的形式与外界进行命令传输。通过USB读取FLASH存储器中的数据到上位机,并通过VB编写的上位机软件显示给用户。

3 试验结果

为了确保系统具备高精度、高可靠性的功能,在实验室应用激波管进行系统校准。以激波管产生马赫数为1.2~1.3之间的激波作为激励源,共进行了3次试验,试验所得校准参数如表1所示,表中T为低压室气体温度,单位为K;P1为低压室气体初始压力值,单位为MPa;P2为激波管高压室的压力值,为被校准系统实测压力值,单位为MPa。

表1 校准参数表Tab.1 Calibration parameter list

激波速度v:

式中:s为两传感器之间的中心距离,这里为460 mm;Δt为两传感器上升沿时间差,单位为ms。

马赫数Ma:

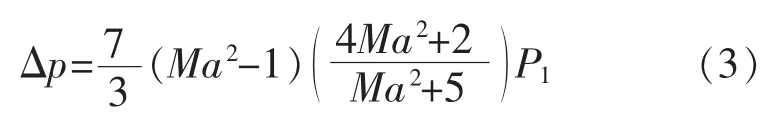

激波反射超压值Δp:

高压室气体压力值P2:

典型测试曲线如图6所示。

图6 典型测试曲线Fig.6 Typical test curve

由表1和图6可以看出系统校准试验中系统误差均小于5%,证明了该测试系统具有一定可靠性,可以应用于实际冲击波超压测试试验。

4 结语

本文提出了基于Nios II的动爆冲击波记录仪,为相关器件工作状态的特性测试与理论校验提供了详细、精确、高可靠性的原始数据。比较于传统动爆冲击波记录仪设计的方案,基于Nios II来设计更加适合,不仅能解决记录仪小型化的问题,大大降低了设计复杂度,减少了开发周期,而且系统的升级十分方便。该设计为动爆冲击波数据的采集存储提供了一种全新的实现手段,且具有很高的实用价值。

[1]田壮,杜红棉,祖静,等.战斗部动爆冲击波存储测试方法研究[J].弹箭与制导学报,2013,33(3):66-69.

[2]刘建伟,裴东兴,尤文斌,等.回收式固态弹载记录仪抗高冲击设计[J].传感技术学报,2012,25(8):1045-1048.

[3]丁永红,尤文斌,马铁华.舰用动爆冲击波记录系统的设计与应用[J].爆炸与冲击,2013,33(2):194-199.

[4]张娇婷,张颖龙,朱怡,等.基于ARM+FPGA的通用导弹弹载记录仪的设计[J].弹箭与制导学报,2014,34(2):38-41.

[5]刘书文,骆英.基于NiosⅡ的超声相控阵数据采集系统[J].仪表技术与传感器,2014(6):72-75.

[6]盛江坤,邱孟通,姚志斌,等.NAND型Flash存储器总剂量效应实验研究[J].原子能科学技术,2014(8):1502-1507.

[7]黄海波,蒋伟荣,刘勇,等.基于SOPC的智能车辆道路识别与跟踪[J].仪器仪表学报,2012,33(2):321-326.