0.8 µm SOI CMOS抗辐射加固工艺辐射效应研究

马慧红,顾爱军

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

0.8 µm SOI CMOS抗辐射加固工艺辐射效应研究

马慧红,顾爱军

(中国电子科技集团公司第58研究所,江苏 无锡 214035)

采用抗辐射0.8 µm SOI CMOS加固技术,研制了抗辐射SOI CMOS器件和电路。利用Co60γ射线源对器件和电路的总剂量辐射效应进行了研究。对比抗辐射加固工艺前后器件的Id-Vg曲线以及前栅、背栅阈值随辐射总剂量的变化关系,得到1 Mrad(Si)总剂量辐射下器件前栅阈值电压漂移小于0.15 V。最后对加固和非加固的电路静态电流、动态电流、功能随辐射总剂量的变化情况进行了研究,结果表明抗辐射加固工艺制造的电路抗总剂量辐射性能达到500 krad(Si)。

SOI;radiation-hard;ASIC;SIMOX

1 引言

近年来,由于在器件隔离、速度及密度上相对于体硅具有显著的优势,SOI(绝缘体上硅)技术受到了研究者们的广泛关注[1]。

在抗辐射加固应用方面,SOI技术具有先天的优势,是体硅技术所不能比拟的。

首先,SOI技术由于有完全的隔离结构,能很好地免疫单粒子闩锁效应。

其次,由于埋氧化层的存在,SOI技术确保了对单粒子效应的低敏感性[2,3]。

第三,SOI技术分布电容小,电路速度高,并且不存在阱区,使得电路集成度得到大幅度提高。然后,由于埋层二氧化硅的存在,限制了SOI工艺抗总剂量辐射的能力,国外已在部分耗尽SOI 工艺上实现抗超高总剂量电离辐射加固[4~10],国内鲜有类似报道。

为了提高ASIC电路在抗总剂量辐射方面的能力,本文采用0.8 µm SOI CMOS抗辐射加固工艺技术,研制出抗辐射SOI CMOS器件和电路,并且对研制的抗辐射SOI CMOS器件和电路进行辐照试验,得到采用抗辐射加固工艺与未采用加固工艺的0.8 µm SOI CMOS器件的Id-Vg曲线以及前栅、背栅阈值随辐射总剂量的变化关系。

2 实验

采用全剂量SIMOX圆片制备0.8 µm SOI CMOS晶体管和ASIC电路,所用晶圆埋氧层厚度为375±5 nm,顶层硅厚度为205±5 nm,所用工艺涉及N+、P+双掺杂多晶硅栅技术、Salicide(自对准硅化物)、LOCOS隔离技术等。

为了提高SOI CMOS器件的抗总剂量辐射性能,采用离子注入工艺在BOX(埋层二氧化硅)中引入电子陷阱,降低辐射后器件的背栅阈值电压漂移。同时为了提高NMOS的前沟道导电能力,本文进行了一系列的试验来优化NMOS的沟道掺杂工艺和器件结构。利用Co60γ源对器件和电路的电离总剂量辐射特性进行研究,从而来对比采用抗辐射加固工艺前后的器件和电路在电学特性上和抗辐射性能上的差异。

3 结果与讨论

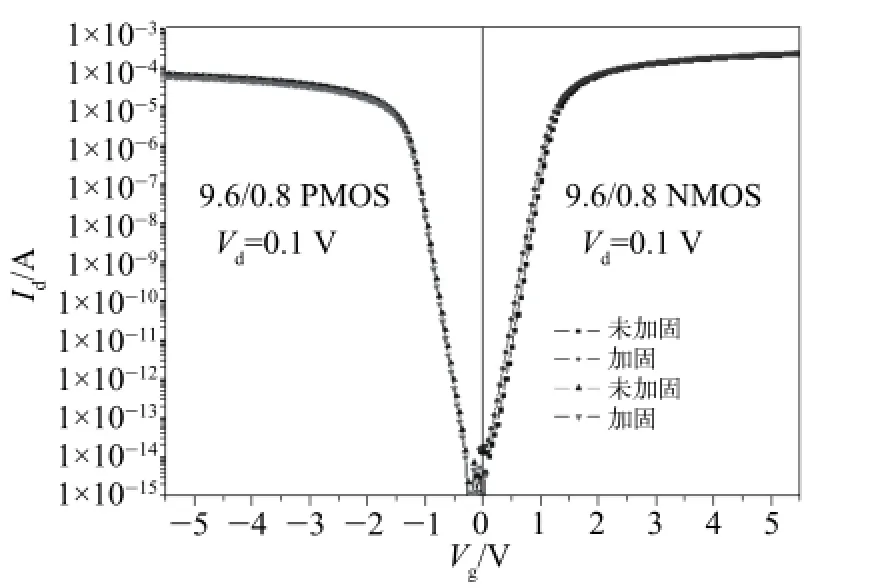

图1是典型未加固(Normal sample)和加固(RH sample)的NMOS和PMOS转移特性曲线,器件宽长比均为9.6 µm/0.8 µm,漏端电压Vd=0.1 V,可以看出转移特性在常态下基本是一致的,器件漏电低于10-14A。

图1 未加固和加固的NMOS和PMOS的转移特性曲线

表1显示了采用抗辐射0.8 µm SOI CMOS加固工艺前后的器件常态电学特性对比,其中Vt1表示器件前栅阈值电压,Vt2表示器件背栅阈值电压,Idsat表示器件饱和电流,Vbd表示器件源漏击穿电压。从表1可以看出,采用抗辐射加固工艺后的器件特性与原工艺相当,满足电路应用的需求。

对未采用抗辐射加固工艺和采用加固工艺的器件和电路进行总剂量辐照实验,剂量点选择300 krad(Si)、500 krad(Si)、1 Mrad(Si)、2 Mrad(Si)。对比器件和电路的电学特性。

表1 未采用抗辐射加固工艺和采用加固工艺的器件参数对比图

图2~图6是总剂量辐照后器件的电学特性变化情况(测试条件:Vg=-2~5 V,step=0.05 V,Vd=0.1 V),其中图2为未采用抗辐射加固工艺的NMOS器件的Id-Vg特性曲线,辐照偏置为前栅ON偏置(Vg=5 V,Vs=Vd=Vb=Ve=0 V)。可以发现较之常态的NMOS器件,随着辐射总剂量的增加,漏端电流不断增加,甚至超过了µA级别,而且有继续增大的趋势。1 Mrad(Si)总剂量辐射后,NMOS器件前栅阈值电压漂移约为0.15 V。

图3是未采用抗辐射加固工艺的NMOS器件的背栅Id-Vbg特性曲线,可以发现,在背栅电压为25 V左右时,漏端电流开始出现,这是一个正常的状态。而随着辐射剂量的加大,背栅阈值电压降低,漏端电流大幅增加,器件的特性改变,在辐射总剂量达到2 Mrad(Si)时,漏端电流达到了µA级,显然,该器件在如此恶劣的环境下不能正常工作。

图2 未采用抗辐射加固工艺NMOS器件的前栅Id-Vg特性曲线

与之对比,图4是采用抗辐射加固工艺的NMOS器件的Id-Vg特性曲线,其测试条件和未加固的器件相同。同在不断增大辐射剂量的情况下,加固NMOS器件与未加固器件的电学特性变化截然不同。采用抗辐射加固工艺的NMOS器件其漏端电流保持正常状态,1 Mrad(Si)总剂量辐射后,NMOS器件前栅阈值电压漂移0.11 V左右。

图3 未采用抗辐射加固工艺NMOS器件的背栅Id-Vbg特性曲线

在受到少量辐射时,未加固器件的背栅特性已经严重变化,而从图5中可以发现在同样的测试条件下,采用抗辐射加固工艺器件的漏端电流在Vbg=25 V左右只有少量的增加,最高也就达到pA级别。对比图3和图5,我们能够清晰地发现,采用抗辐射加固工艺的器件具有很高的抗总剂量辐射能力,即使在2 Mrad(Si)总剂量辐照的恶劣环境下依然能正常工作。

图4 采用抗辐射加固工艺NMOS器件的前栅Id-Vg特性曲线

图5 采用抗辐射加固工艺NMOS器件的背栅Id-Vbg特性曲线

我们在PMOS器件上也进行了同样的辐照实验,偏置采用前栅OFF偏置(Vg=Vb=Vs=5 V,Vd=Ve=0 V)。结果表明,抗辐射加固PMOS器件具有很好的抗辐射性能,1 Mrad(Si)总剂量辐射后,PMOS器件前栅阈值电压漂移0.148 V左右,满足工程化应用要求。

图6 不同辐射总剂量下采用抗辐射加固工艺PMOS器件的前栅Id-Vg特性曲线

采用0.8 µm SOI CMOS抗辐射加固工艺制造集成度约1万门的ASIC电路,图7与图8是未采用抗辐射加固工艺和采用加固工艺的电路静态(IDDQ)与动态电流(IA)随辐射剂量的对比曲线,剂量点选择100 krad(Si)、300 krad(Si)、500 krad(Si)和750 krad(Si)。由实验结果可以看出,辐照前静态电流和动态电流处于正常,电路功能正常。当辐射剂量超过300 krad(Si)时,未加固电路静态电流和动态电流开始突变,电路功能出现异常。而加固电路在剂量增加到750 krad(Si)和1 Mrad(Si)时依然维持较小的静态电流和动态电流。

图7 未采用抗辐射加固工艺和采用加固工艺的电路静态电流对比图

表2为抗辐射加固电路的辐照试验结果,当总剂量辐射达到500 krad(Si)时,电路静态电流能够满足100 µA的指标要求,在增加50%辐照剂量的情况下,电路静态电流、动态电流和功能仍能够满足规范要求。

4 结论

图8 未采用抗辐射加固工艺和采用加固工艺的电路动态电流对比图

通过理论和试验验证,可以得出:采用抗辐射加固工艺的器件其电学特性能够达到常态要求,器件的抗辐射性能显著好于未采用抗辐射加固工艺器件,在1 Mrad(Si)总剂量辐射后器件的指标满足电路制造的要求。此外,采用抗辐射加固工艺的电路在抗总剂量辐射性能上更胜一筹,当辐射总剂量达到一个很高的数值时,抗辐射加固工艺电路的静态、动态电流依然能保持辐照前的水平,最后试验得出采用抗辐射加固工艺制造的电路具有抗500 krad(Si)总剂量辐射的能力。

表2 电路辐照试验结果

上述结果证明通过抗辐射加固工艺可以显著提高SOI CMOS器件和电路的抗总剂量辐射能力。

[1] Auberton Herve A J. SOI: materials to systems [A]. IEEE International Electron Device Meeting Technical Digest, 1996.

[2] Brady F T, S cott T, Brown R, et al. Fully-depleted submicron SOI for radiation hardened application [J]. IEEE Trans Nucl Sci, 1994, 41: 2304.

[3] Hatano H. Radiation hardened high performance CMOS VlSI circuit design [J]. IEE Proceedings-G, 1992, 139: 287.

[4] Zhang Guoqiang, Liu Zhongli, Li Ning, et al. Influence of fluorine on radiation-induced charge trapping in the SIMOX buried oxides [A]. Proceeding of 7th International Conference on Solid-State and Integrated Circuits Technology, 2004.

[5] Hughes H, McMarr P. Radiation-hardening of SOI by ion implantation into the buried oxide [S]. US Patent. No.5795813.

[6] White M H, Adams D A, Murray J R, et al. Characterization of scaled SONOS EEPROM memory devices for space and military systems [A]. Non-Volatile Memory Technology Symposium, 2004.

[7] Wu Junfeng, Zhong Xinghua, Li Duoli. Improved breakdown voltage of partially depleted SOI nMOSFETs with half-backchannel implantation [J]. Chinese Journal of Semiconductors, 2005, 26(10): 1875.

[8] Ohno T, Izumi K, Shimaya M, et al. CMOS/SIMOX devices having a radiation hardness of 2Mrad(Si)[J]. Electron Lett, 1987, 23: 141.

[9] Liu S T, Jenkins W C, Hughes H L. Total dose radiation hard 0.35µm SOI CMOS technology [J]. IEEE Trans Nucl Sci, 1990, 37: 2013.

[10] Mao B Y, Chen C E, Pollack G, et al. Total dose hardening of buried insulator in implanted silicon-on-insulator structures [J]. IEEE Trans Nucl Sci, 1987, 34: 1692.

Study of the Radiation-hard 0.8 µm SOI CMOS Process Radiation Influence

MA Huihong, GU Aijun

(China Electronics Technology Group Corporation No.58 Research Institute, Wuxi 214035, China)

The paper focused on the radiation-hard 0.8 µm SOI CMOS process, the devices and circuits were fabricated. The devices and circuits’ behavior in Co60γ ray irradiation circumstances was studied. It shows that the devices with and without the radiation-hard technology had different performance. The hardened devices’ threshold voltage of the front gate shifts less than 0.15 V. The hardened circuits’ standby current, dynamic current and function were also tested. The results showed that the circuits with the radiation-hard process can meet the specification of 100 µA over the total dose range of 500 krad(Si).

SOI; radiation-hard; ASIC; SIMOX

TN402

A

1681-1070(2015)07-0020-04

马慧红(1972—),女,2004年毕业于东南大学,毕业后工作于中国电子科技集团公司第58研究所,从事半导体原材料、备件采购及原材料、备件国产化替代工作和民品项目申报管理工作。

2015-03-13